電子發燒友網報道(文/周凱揚)隨著AI與HPC運算的盛行,如今為了將算力繼續擴展下去,CPU和GPU都在朝著多核的方向發展下去,計算密度也在大幅提升。此外,數據中心也越來越多地開始轉向異構工作負載,對基礎架構、性能和可用性提出了又一輪的要求,也在加速存儲產品的轉型,催生了CXL這樣的新技術,但僅僅只靠CXL,是無法打破我們所說的內存瓶頸的。

加速內部流量成為服務器性能的新關鍵

100GbE模塊的出現后,在網絡交換與傳輸性能如此發達的當下,遠程存儲已經成了越來越多企業的首選。但本地存儲也在經歷一輪性能的革命,NVMe、NVDIMM等技術演進進一步降低了存儲的網絡延遲,解決了一路走高的內部帶寬需求。

那么服務器內部數據的移動要如何跟上呢?在復雜的服務器基礎架構中,內部數據的交換往往由多個內存緩沖拷貝組成,比如內核到I/O、I/O到特定硬件,實現方式主要靠不同層級的軟件棧,但軟件到軟件間的數據交換仍靠的是CPU。

當下的內存數據移動的軟件標準為memcpu,雖然已經足夠穩定,但也限制了應用的性能。比如為了提供上下文隔離而招致更大的軟件開銷。所以大家開始嘗試DMA,這種用于卸載軟件復制循環的策略。雖說這樣做解放了CPU的部分負擔,但這種方案與特定設備的接口綁定,只適合專門的特權軟件和I/O用例,更別提前向兼容了,尤其是在公有云這種多人功用的虛擬環境中。

SDXI,新的數據加速器接口標準

這就引出了一系列痛點,比如既要從CPU執行周期中將I/O解放出來,又要保證架構的穩定性。提供虛擬機加速的同時,又能幫助開發者從已有軟件棧中遷移到新的方案上,還要考慮到當下新的內存互聯方案,比如CXL、Gen-Z等等。為了解決這些痛點,2020年起,SNIA(全球網絡存儲工業協會)成立了一個新的工作組并提出了SDXI(智能數據加速器接口)這一概念,為的就是提供一個可擴展、虛擬化且前向兼容的內存數據移動與加速接口規范。

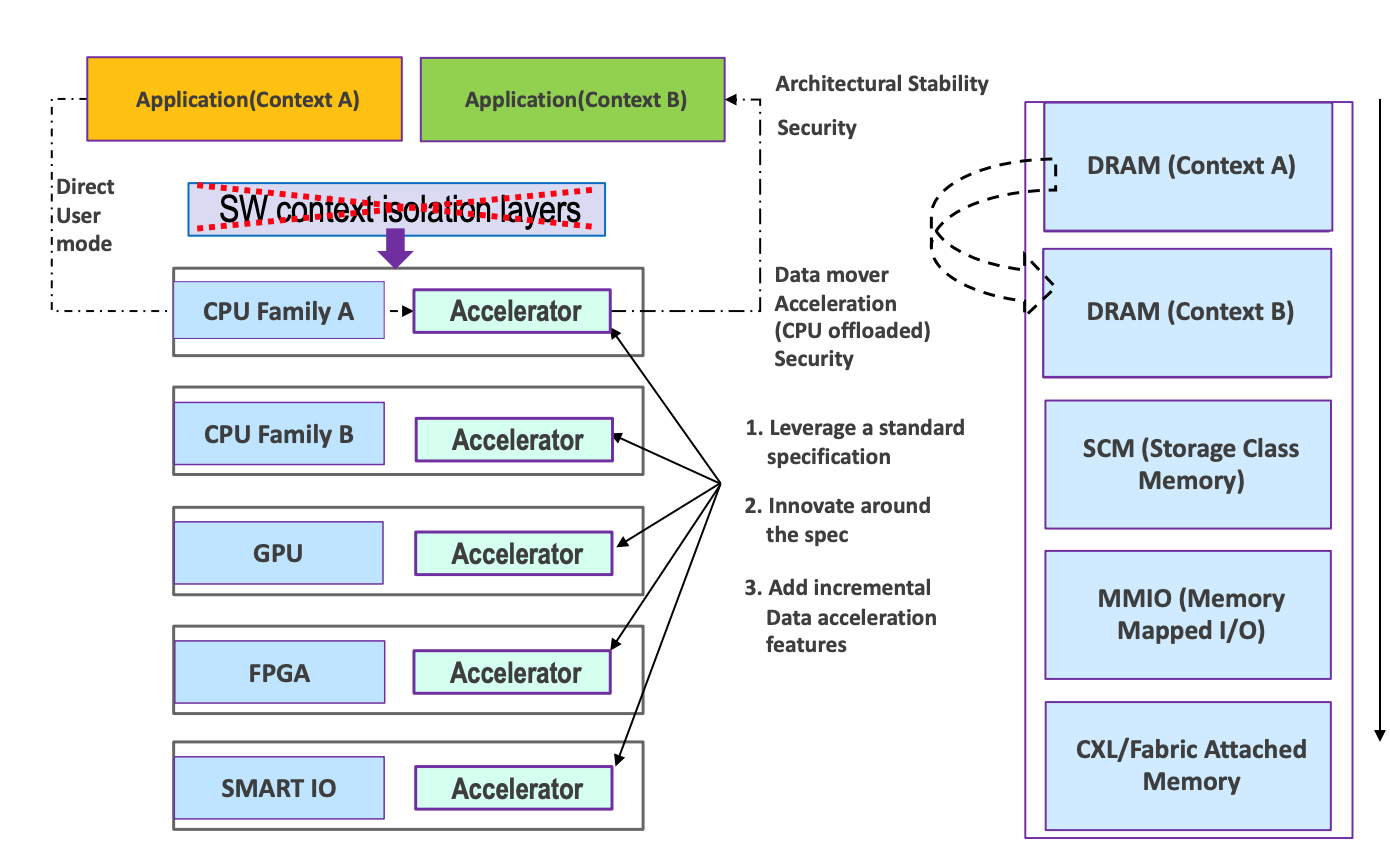

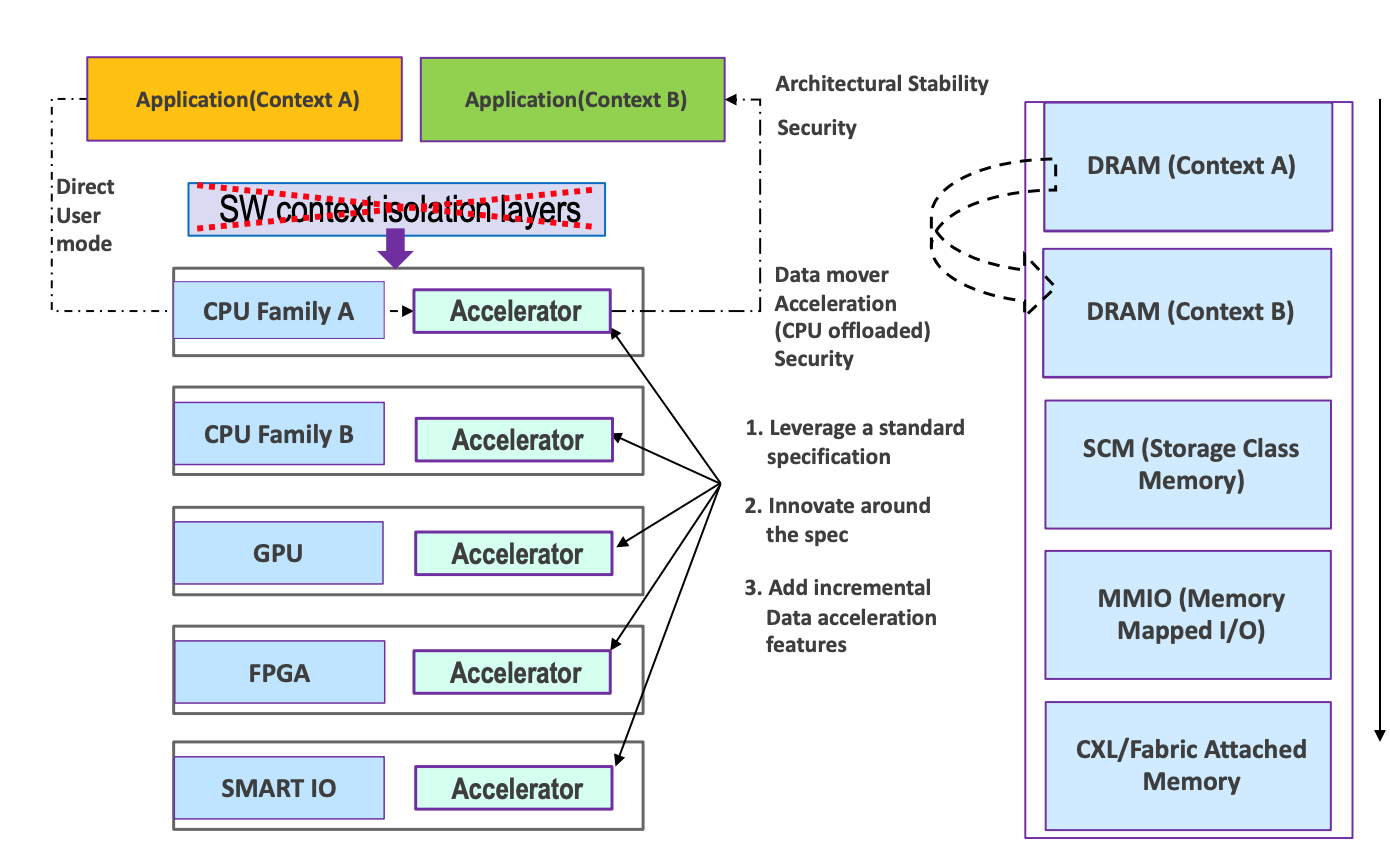

SDXI下的內存間數據移動 / SNIA

SDXI作為一個標準化方案,不僅要兼容DRAM、SCM、MMIO、CXL和Gen-Z這些不同的內存,也要為CPU、GPU、FPGA、智能I/O等提供標準的加速器接口。如此一來,SDXI可以在不同的地址空間實現數據移動,包括用戶地址空間和不同的虛擬機等。而且一旦連接建立,數據移動再也不需要特權軟件作為中介。從戴爾在PCIe 3.0 FPGA上的原型測試上來安,改用SDXI可以實現超過memcpy兩倍以上的線性拷貝速度。

截至目前,不少內存廠商和服務器廠商都已經加入了對SDXI的貢獻行列中來,比如AMD、Arm、戴爾、HPE、IBM,以及美光、三星、SK海力士等。他們也在考慮在1.0標準之后,繼續從QoS、延遲、RAS上加以改進,在實現未來版本前向與后向兼容的同時,一起推動SDXI在CXL系統架構中的普及。

小結

在ARM、RISC-V紛紛入局數據中心,并推出百核、千核的CPU處理器后,更快的數據交換將成為一個必然的需求,未來的網絡與存儲技術也需要SDXI提供這樣的擴展性。何況SDXI提供的不僅僅是加速,還是一個標準化接口,在滿足數據移動性能的同時,支持軟件愛你的重復利用和虛擬化。

加速內部流量成為服務器性能的新關鍵

100GbE模塊的出現后,在網絡交換與傳輸性能如此發達的當下,遠程存儲已經成了越來越多企業的首選。但本地存儲也在經歷一輪性能的革命,NVMe、NVDIMM等技術演進進一步降低了存儲的網絡延遲,解決了一路走高的內部帶寬需求。

那么服務器內部數據的移動要如何跟上呢?在復雜的服務器基礎架構中,內部數據的交換往往由多個內存緩沖拷貝組成,比如內核到I/O、I/O到特定硬件,實現方式主要靠不同層級的軟件棧,但軟件到軟件間的數據交換仍靠的是CPU。

當下的內存數據移動的軟件標準為memcpu,雖然已經足夠穩定,但也限制了應用的性能。比如為了提供上下文隔離而招致更大的軟件開銷。所以大家開始嘗試DMA,這種用于卸載軟件復制循環的策略。雖說這樣做解放了CPU的部分負擔,但這種方案與特定設備的接口綁定,只適合專門的特權軟件和I/O用例,更別提前向兼容了,尤其是在公有云這種多人功用的虛擬環境中。

SDXI,新的數據加速器接口標準

這就引出了一系列痛點,比如既要從CPU執行周期中將I/O解放出來,又要保證架構的穩定性。提供虛擬機加速的同時,又能幫助開發者從已有軟件棧中遷移到新的方案上,還要考慮到當下新的內存互聯方案,比如CXL、Gen-Z等等。為了解決這些痛點,2020年起,SNIA(全球網絡存儲工業協會)成立了一個新的工作組并提出了SDXI(智能數據加速器接口)這一概念,為的就是提供一個可擴展、虛擬化且前向兼容的內存數據移動與加速接口規范。

SDXI下的內存間數據移動 / SNIA

截至目前,不少內存廠商和服務器廠商都已經加入了對SDXI的貢獻行列中來,比如AMD、Arm、戴爾、HPE、IBM,以及美光、三星、SK海力士等。他們也在考慮在1.0標準之后,繼續從QoS、延遲、RAS上加以改進,在實現未來版本前向與后向兼容的同時,一起推動SDXI在CXL系統架構中的普及。

小結

在ARM、RISC-V紛紛入局數據中心,并推出百核、千核的CPU處理器后,更快的數據交換將成為一個必然的需求,未來的網絡與存儲技術也需要SDXI提供這樣的擴展性。何況SDXI提供的不僅僅是加速,還是一個標準化接口,在滿足數據移動性能的同時,支持軟件愛你的重復利用和虛擬化。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

發布評論請先 登錄

相關推薦

熱點推薦

無線快充技術,國內首個統一標準發布

電子發燒友報道(文/李彎彎)近日,中國通信標準化協會與電信終端產業協會聯合宣布,《移動終端融合快速充電 無線充電技術要求》團體標準正式發布,該標準由中國信通院聯合國內主流終端與芯片企業

Aliro 1.0 全新統一標準發布 重塑智能門鎖及門禁生態系統

加利福尼亞州戴維斯市——2026 年2 月26 日—— 連接標準聯盟(聯盟)今日正式發布Aliro 1.0 規范。作為一套全新通信協議與憑證標準,Aliro 將徹底改變用戶在生活各類場景中與門禁設備

為什么原廠越來越需要一套自己的 Studio

外設怎么配

第一版工程如何快速跑起來

這些問題,已經很難只靠數據手冊解決。

二、手冊 + 示例工程,逐漸不夠用了

大多數原廠其實已經做了很

發表于 02-05 09:37

瀾起科技發布PCIe 6.x/CXL 3.x AEC解決方案

瀾起科技今日宣布,率先在國內推出基于PCIe 6.x/CXL 3.x標準的高性能有源電纜(AEC,Active Electrical Cable)解決方案。該方案面向數據中心從單機架向多機架復雜架構

Penguin Solutions SMART Modular CXL NV-CMM E3.S 2T 內存模塊通過 CXL 兼容性認證

失性內存模塊已成功通過 CXL? 兼容性測試。此項里程碑不僅代表產品符合行業標準,也進一步確立 Penguin Solutions 在 CXL

借助CXL和壓縮技術實現高效數據傳輸

AI、科學計算、海量內存處理……這些硬核工作負載正在不斷挑戰系統極限。而 FPGA 異軍突起,成為了實現高效數據傳輸的“關鍵推手”。想知道怎么在不改變整體架構的前提下,讓帶寬和能效實現“雙飛躍”?答案就藏在壓縮 IP 與基于 CXL(Compute Express Lin

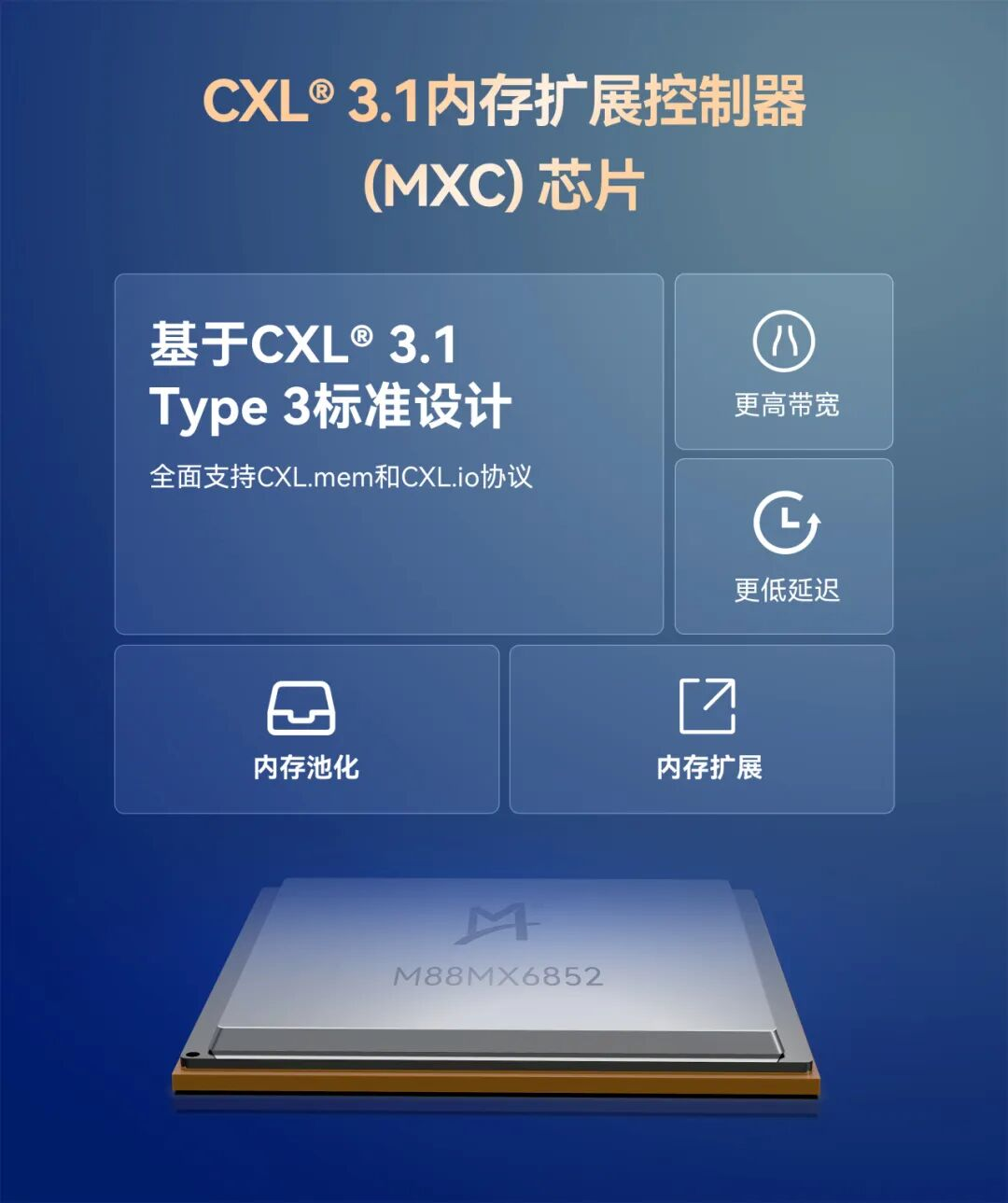

64GT/s+8000MT/s:瀾起CXL 3.1芯片破解數據中心內存瓶頸

。 ? ? M88MX6852:性能卓越,滿足多元需求 ? M88MX6852芯片全面支持CXL.mem和CXL.io協議,其核心使命是為下一代數據中心服務器打造更高帶寬、更低延遲的內存擴展和池化解決方案。在

瀾起科技推出CXL? 3.1內存擴展控制器,助力下一代數據中心基礎設施性能升級

下一代數據中心服務器提供更高帶寬、更低延遲的內存擴展和池化解決方案。 瀾起科技CXL 3.1內存擴展控制器采用PCIe? 6.2物理層接口,支持最高64 GT/s的傳輸速率(x8通道),并具備多速率

第二代AMD Versal Premium系列SoC滿足各種CXL應用需求

第二代 AMD Versal Premium 系列自適應 SoC 是一款多功能且可配置的平臺,提供全面的 CXL 3.1 子系統。該系列自適應 SoC 旨在滿足從簡單到復雜的各種 CXL 應用需求

新思科技解讀CXL 3.1標準

Compute Express Link(CXL)于2019年首次發布,是處理器與AI加速器、內存緩沖區、智能網絡接口卡、持久性存儲器和固態驅動器等設備之間的開放式行業標準互連技術。作為一種行業

只靠CXL還不夠,數據移動也需要統一標準

只靠CXL還不夠,數據移動也需要統一標準

評論