本應用筆記給出了MAX2395的優化環路濾波器設計,具有80kHz比較頻率,以支持WCDMA/UMTS系統。參考頻率為 13MHz 或 26MHz。還顯示了 EVM 結果。

介紹

MAX2395為全單芯片準直接變頻調制器IC,用于WCDMA/UMTS發送器。由于其內部架構,RF輸出頻率為RF LO頻率的5/6,RF頻率由片內整數N分頻PLL產生。由于WCDMA系統中的光柵頻率為200kHz,MAX2395 PLL需要提供240kHz步長(即6的5/200倍)。對于WCDMA用戶終端應用中最常用的參考頻率,例如19.2MHz和15.36MHz,內部PLL整數分頻器(分別為240和80)可以輕松生成64kHz比較頻率。模擬評估板在設計時考慮了19.2MHz基準電壓源。

在UMTS系統中,通常使用13MHz或26MHz的參考頻率,它不是240kHz的整數倍。因此,MAX2395的PLL使用的比較頻率需要降低到倍數為240kHz和13/26MHz。對于26MHz晶體,常用的比較頻率為80kHz,通過使用三個240kHz步進允許80kHz通道光柵。對于相同的LO,80kHz PLL頻率的“N分頻”值高出3倍,導致近載波相位噪聲(10logN)增加20dB。

EVM(誤差矢量幅度)也會降低,因為PLL對EVM的貢獻大致與其積分相位誤差成正比。比較雜散從環路濾波器獲得的衰減較低,因此需要重新設計環路濾波器,以平衡積分相位誤差、建立時間和比較雜散衰減。

環路濾波器組件

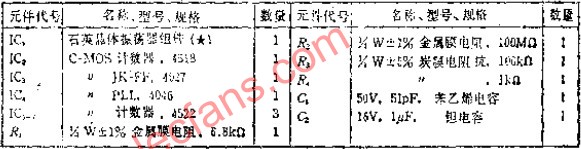

在240kHz比較頻率下使用的環路濾波器帶寬約為12kHz,對于7kHz比較頻率情況,帶寬約為80kHz。下表顯示了相應的環路過濾器組件值:

| 帶寬 = 12kHz, 240kHz 比較頻率 | 帶寬 = 7kHz, 80kHz 比較頻率 |

| C1 = 2.2nF | C1 = 1nF |

| C2 = 22nF | C2 = 10nF |

| R2 = 3.3kΩ | R2 = 7.5kΩ |

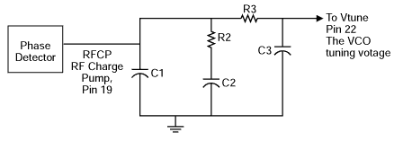

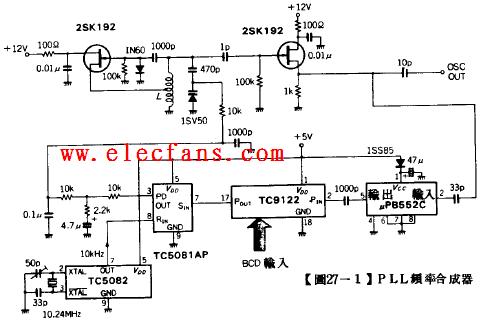

參見下面的原理圖(圖1),了解無源環路濾波器拓撲。

圖1.

測量數據

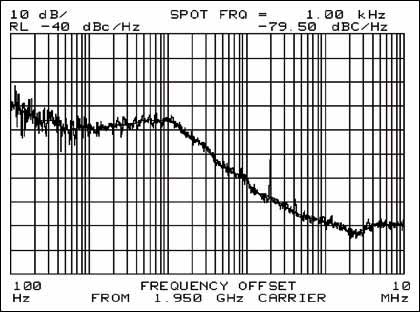

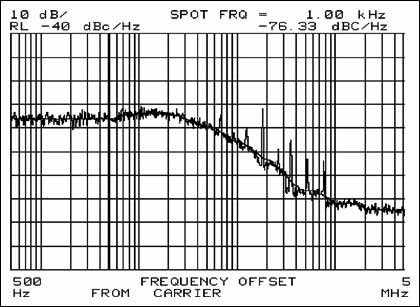

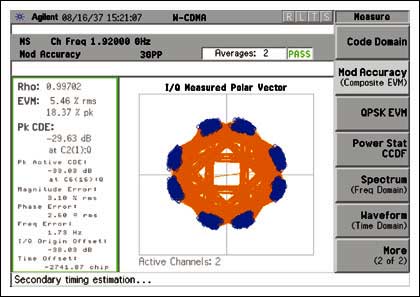

MAX2395的性能分別在模擬WCDMA參考設計板上使用19.2MHz和26MHz晶體進行測量。所有測量的圖如圖2至圖7所示。

圖2.19.2MHz基準晶體處的相位噪聲圖。

圖3.26MHz參考晶體處的相位噪聲圖。

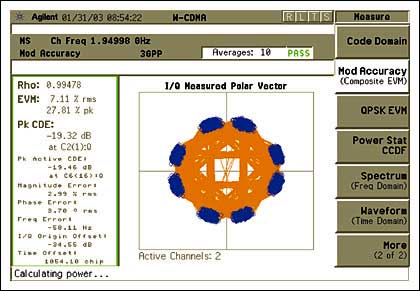

圖4.射頻輸出時的 EVM,頻率為 19.2MHz 參考晶體。

圖5.26MHz 參考晶體時射頻輸出時的 EVM。

圖6.超過 60MHz 的 PLL 建立時間在 19.2MHz 晶體處跳躍。

圖7.PLL建立時間超過60MHz,在26MHz晶體時跳躍。

500Hz至1.92MHz的積分相位誤差在1kHz比較頻率下為98.240度,在2kHz比較頻率下為75.80度。前者在RF輸出為5.5%時產生EVM結果,而后者產生7.2%的EVM。對于采用720.60MHz晶體的19MHz步進頻率,環路建立時間為2μs,對于820MHz晶體,環路建立時間為26μs。兩種情況下的比較雜散衰減相似,約為-40dBc。

審核編輯:郭婷

-

RF

+關注

關注

66文章

3201瀏覽量

171820 -

調制器

+關注

關注

3文章

975瀏覽量

48503 -

發送器

+關注

關注

1文章

261瀏覽量

27728

發布評論請先 登錄

TLV320AIC3101測試音頻的儀器不用80KHZ的低通濾波器時,輸出信號失真度很大,為什么?

LMK04808 PLL1為什么不能正常鎖定?

AD7767主時鐘由STM32提供80KHz時,DRDY信號產生異常是什么問題?

基于FPGA的PLL頻率合成器

80M~1.2G頻帶PLL頻率合成器

MAX2395 WCDMA準直接調制器,帶有VGA和PA驅動

MAX2395ETI+ RF 其它 IC 和模塊

MAX2395ETI+T RF 其它 IC 和模塊

MAX2395輸出與SAW濾波器匹配,實現最佳的級聯增益平坦度

MAX2395鎖相環(PLL)在鑒相頻率為80kHz時的性能

MAX2395 PLL在80kHz比較頻率下的性能

MAX2395 PLL在80kHz比較頻率下的性能

評論