使用always_ff和在靈敏度列表中指定一個時鐘邊沿并不意味著過程中的所有邏輯都是時序邏輯。綜合編譯器將推斷出每個被非阻塞賦值的變量的觸發器。阻塞賦值也可能推斷出觸發器,這取決于賦值語句相對于程序中其他賦值和操作的順序和上下文。

然而,在有些情況下,組合邏輯數據流行為將從時序邏輯程序中推斷出來。

時序賦值右側的操作符將綜合為組合邏輯,其輸出成為觸發器的D輸入。

如果時序分配的右側調用一個函數,該函數將綜合為組合邏輯,其輸出成為觸發器的D輸入。

圍繞著賦值語句的決策語句可能會綜合為組合式多路復用邏輯,選擇那個表達式作為觸發器的D輸入。

在begin-end語句組中對臨時變量的阻塞賦值,將綜合為組合邏輯,其中臨時變量成為在begin-end中后續非阻塞賦值推斷出的觸發器的輸入。

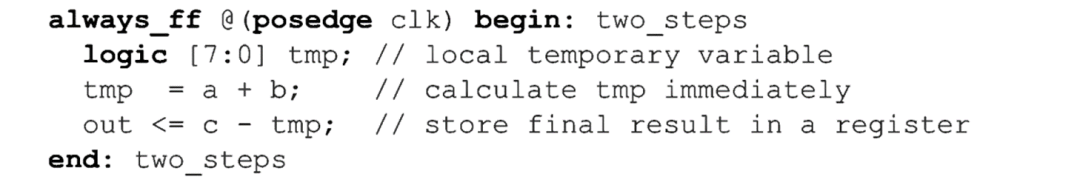

下面非例子說明了在begin-end語句組中對臨時變量的阻塞賦值,將綜合為組合邏輯。

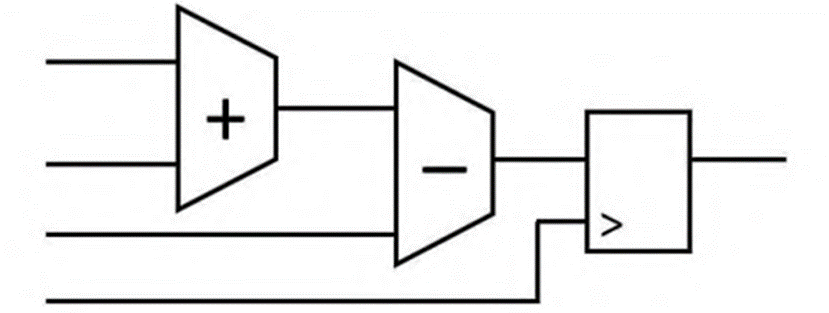

下面就是上面的例子中推斷的示意圖。

對中間臨時變量的阻塞賦值

審核編輯 :李倩

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

邏輯

+關注

關注

2文章

834瀏覽量

30138 -

觸發器

+關注

關注

14文章

2056瀏覽量

63407 -

時序

+關注

關注

5文章

406瀏覽量

38862

原文標題:【數字實驗室】時序邏輯程序中推斷組合邏輯?

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

FPGA之組合邏輯與時序邏輯、同步邏輯與異步邏輯的概念

數字電路根據邏輯功能的不同特點,可以分成兩大類:一類叫做組合邏輯電路,簡稱組合電路或組合邏輯;另

發表于 12-01 09:04

?1514次閱讀

如何避免組合邏輯程序中的意外鎖存

組合邏輯描述了門級電路,其中邏輯塊的輸出直接反映到該塊的輸入值的組合,例如,雙輸入AND門的輸出是兩個輸入的邏輯與。如果輸入值發生變化,輸出

【技巧分享】時序邏輯和組合邏輯的區別和使用

一般要求是時序邏輯)。在實際設計中,為了便于操作,我們可以首先考慮用時序邏輯,看是否能滿足設計要求。如果無法滿足目標要求,需要湊

發表于 03-01 19:50

在FPGA中何時用組合邏輯或時序邏輯

的。話不多說,上貨。 在FPGA中何時用組合邏輯或時序邏輯 在設計FPGA時,大多數采用Verilog HDL或者VHDL語言進行

發表于 03-06 16:31

基于位串編碼的遺傳歸納邏輯程序設計

歸納邏輯程序設計是基于一階邏輯的數據挖掘新方法。一階規則挖掘是目標謂詞和背景知識謂詞對應的各種原子的復雜組合優化問題。該文根據Occam’s razor原理提出原子的位串編碼

發表于 03-31 09:48

?11次下載

時序邏輯電路有哪些 時序邏輯電路和組合邏輯電路區別

時序邏輯電路是一種能夠存儲信息并根據時鐘信號按照特定順序執行操作的電路。它是計算機硬件中非常重要的一部分,用于實現存儲器、時序控制器等功能。與之相對的是組合

時序邏輯程序中推斷組合邏輯?

時序邏輯程序中推斷組合邏輯?

評論