點擊藍字關注我們

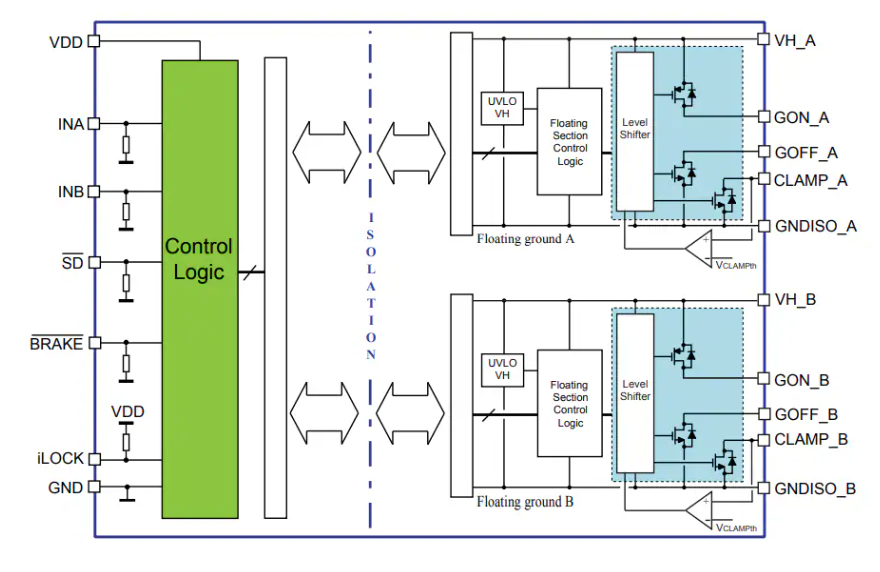

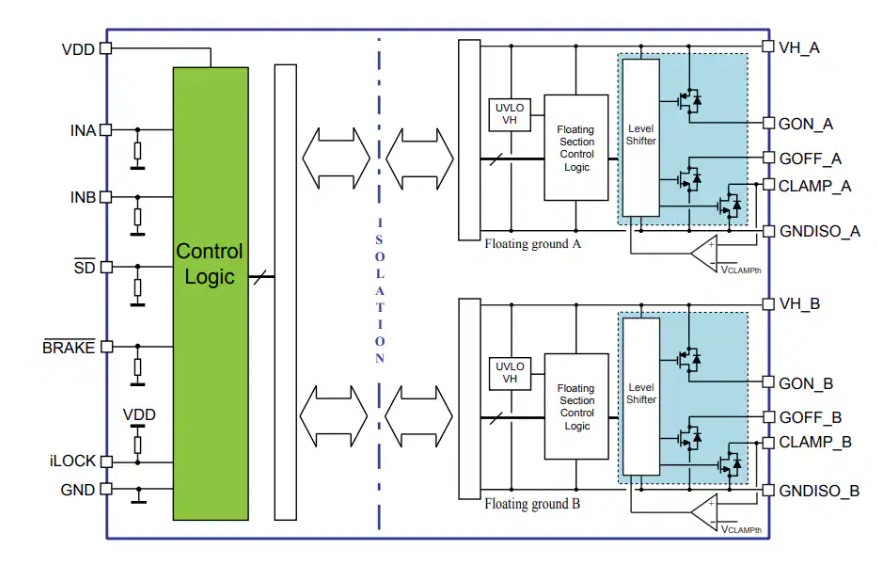

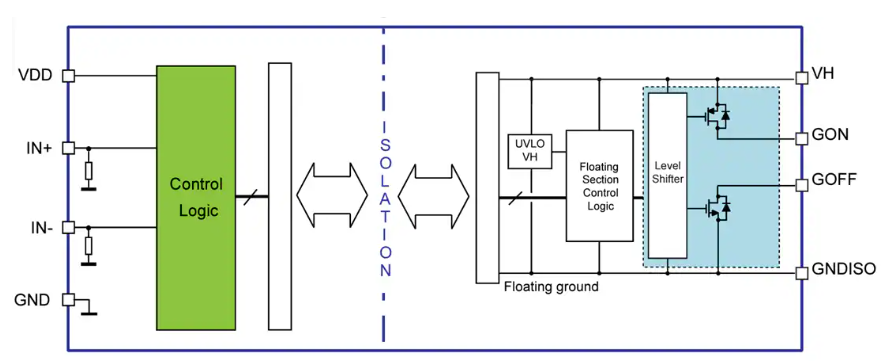

本設計指南分為三部分,將講解如何為電力電子應用中的功率開關器件選用合適的隔離柵極驅動器,并介紹實戰經驗。上次為大家梳理了隔離式柵極驅動器的介紹和選型指南(詳情可點擊查看),本文為第二部分,將帶大家全面了解使用安森美(onsemi)隔離式柵極驅動器的電源、濾波設計以及死區時間控制。

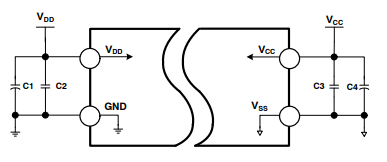

以下是使用隔離式柵極驅動器電源時應注意的一些建議。VDD 和 VCC 的旁路電容對于實現可靠的隔離式柵極驅動器性能至關重要。

建議選擇具有適當電壓額定值、溫度系數和電容容差的低 ESR 和低 ESL 表面貼裝多層陶瓷電容 (MLCC)。柵極驅動器的輸出偏置電源引腳需要旁路電容,其值至少應為開關器件柵極電容的 10 倍,并且不小于 100 nF;此電容應位于盡可能靠近該器件的地方,以用于解耦。建議使用 2 個電容:一個 100 nF 陶瓷表面貼裝電容和一個并聯的幾微法電容,如圖 1 所示。

同樣,輸入側的 VDD 和 GND 引腳之間也應放置一個旁路電容。考慮到輸入側的邏輯電路會消耗少量電流,此旁路電容的最小建議值為 100 nF。

圖 1. 電源示意圖

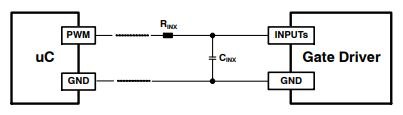

為了獲得良好的信號質量和抗擾度,可以在微控制器和柵極驅動器輸入之間放置一個輸入濾波器 RC 網絡,如圖 2 所示。

電力電子應用中經常使用的濾波方法有兩種:

控制輸入端的 RC 濾波器;

具有較短延遲時間的 RC 濾波器與柵極驅動器本身集成的精密濾波器的組合。

RC 值將取決于系統要求的輸入頻率范圍、占空比和時間延遲。

由最大 100 pF 電容和最多 100Ω 電阻構成的小容性濾波器可抑制驅動器輸入端的高頻噪聲。濾波器電容抑制共模噪聲。

濾波器電阻有助于保護控制器。串聯電阻會限制接地反彈期間流入流出控制器的電流,減弱柵極驅動線的寄生電感(它可能導致振鈴),并有助于抑制任何由長輸入走線吸收的 EMI。

此 RC 濾波器需要放在盡可能靠近柵極驅動器引腳引線的地方。高壓輸出電路的共模瞬變噪聲可能會干擾低壓輸入側。數字控制輸入應使用低阻抗信號源以防止出現毛刺或造成意外開關。

圖 2. 用于輸入信號的 RC 網絡示例

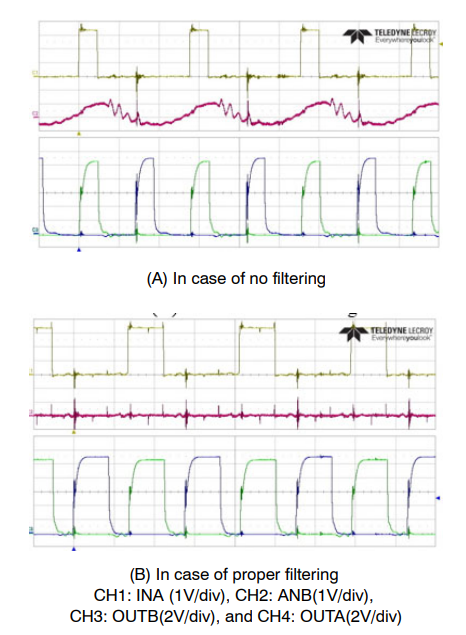

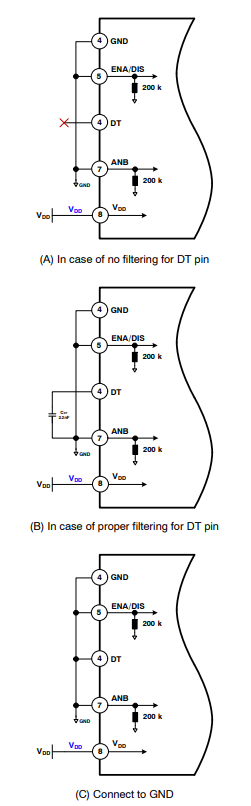

其他輸入引腳(如 ANB、DT 和 ENA/DIS)也需要適當濾波,以使系統穩健。由于功率級瞬變電壓和電流的電磁干擾 (EMI),輸入濾波不當可能導致各種不良影響。

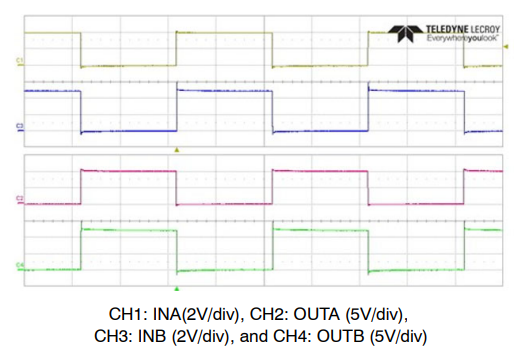

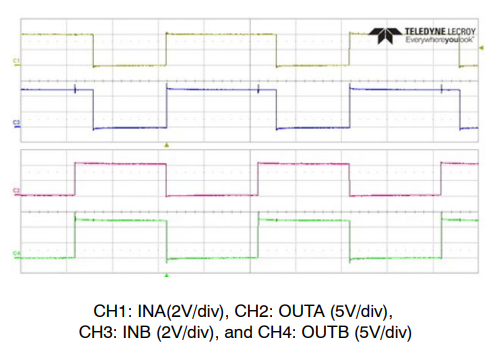

例如,圖 3 顯示了 ANB 引腳浮空時的工作波形,上方圖片沒有濾波,下方圖片則使用了適當濾波。如實驗結果所示,在沒有旁路電容的情況下觀察到噪聲信號,而當靠近此引腳使用 1 nF 以上的旁路電容時,噪聲信號消失。

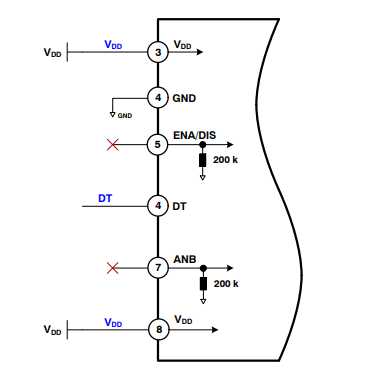

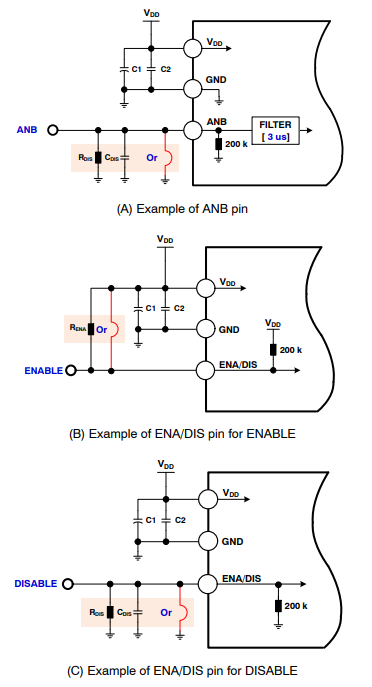

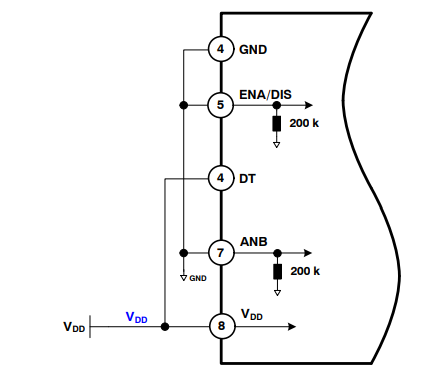

輸入信號引腳的阻抗通常為 200 kΩ;禁用 (DISABLE) 時,ANB 和 ENA/DIS 引腳被拉到 GND 引腳,如圖 4 所示。但使能 (ENABLE) 時,ENA/DIS 引腳被拉到 VDD 引腳,如圖 5 (B) 所示。

圖 3. 元件濾波對 ANB 引腳的影響

驅動器引腳的噪聲可能會耦合到輸入引腳(ANB 和 ENA/DIS)上,導致驅動器對瞬變作出反應,而不是對輸入 PWM 信號作出響應。這可能會造成驅動器輸入和輸出出現不良行為,并且可能會降低系統性能。

此外,如果驅動器的 ANB 和 ENA/DIS 引腳之間的距離較長,那么需要更加注意驅動器的布局和濾波,以避免這種不良行為。

圖 4. AND 示例,ENA/DIS 引腳浮空

如果需要 ENA/DIS DISABLE 和 ANB 功能,應使用約 1nF 的低 ESR/ESL 電容,以改善整體系統性能。以下總結了 ENA/DIS 和 ANB 引腳浮空時的注意事項。

ENA/DIS 引腳:如果不使用 ENA/DIS 引腳,應將其直連 VDD 或 GND 引腳以分別實現 ENABLE 或 DISABLE 功能。當使用 ENA/DIS 引腳提供 ENABLE 或 DISABLE 功能時,如果無法將 ENA/DIS 引腳連接到 VDD 或 GND,那么建議將數十 kΩ(如 10 kΩ ~ 47 kΩ)的外部上拉或下拉電阻連接到 VDD 或 GND 引腳,以實現更好的抗擾度,分別如圖 5 (B) 和 (C) 所示。

當使用控制器驅動幾英寸或更長距離外的 ENA/DIS 引腳時,需要將低 ESR/ESL 的 1 nF 電容放置在引腳附近。

在需要快速禁用響應時間的情況下,應使控制器更靠近驅動器,使用高驅動強度輸出,并最大程度地減少柵極驅動環路中的雜散電感。

ANB 引腳:如果不使用 ANB 引腳,應將其直連 GND 引腳,或使用 1 nF 電容。如果無法將 ANB 引腳連接到 GND,那么建議使用數十 kΩ(如 10 kΩ ~ 47 kΩ)的外部下拉電阻,以防止外部干擾導致 ANB 功能意外激活(盡管其內部有 3.3μs 濾波器),如圖 5 (A) 所示。

圖 5. ANB、ENA/DIS 引腳適當濾波的示例

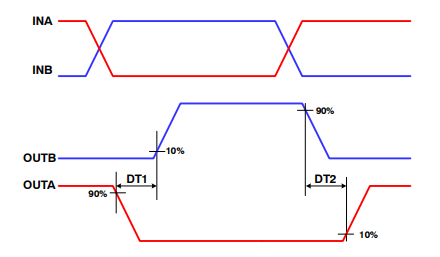

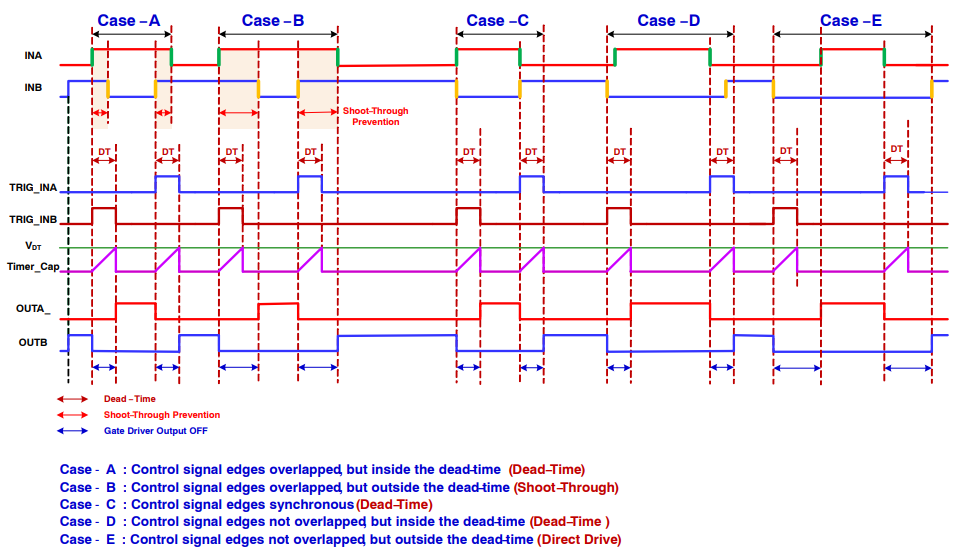

只要兩個外部輸入信號的死區時間(INA 和 INB 信號之間)比內部設置的死區時間(DT1 和 DT2)短,系統就會自動插入死區時間。否則,如果外部輸入信號死區時間大于內部死區時間,則柵極驅動器不會修改死區時間。內部死區時間定義如圖 6 所示。

圖 6. 內部死區時間定義

圖 7 顯示了輸入信號同時施加時內部死區時間和防止擊穿的定義。

圖 7. 內部死區時間定義

圖 7. 內部死區時間定義

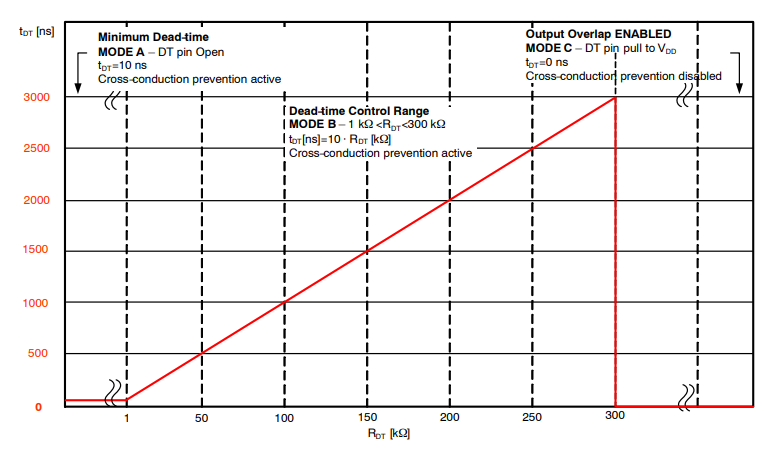

在模式 A 下,當 DT 引腳開路時,最小死區時間 (tDTMIN) 典型值為 10 ns,不允許驅動器兩個輸出(OUTA 和 OUTB)之間交叉導通。在模式 B下,當 DT 引腳電阻在 1 k 和 300 k 之間時,外部電阻 (RDT) 控制死區時間。

當激活死區時間 (DT) 控制模式時,不允許重疊。

兩路輸出之間的死區時間 (DT) 根據下式設置:DT(單位為 ns)= 10 × RDT(單位為 kΩ)。

在模式 C下,當 DT 引腳被拉至 VDD 時,允許兩個輸出重疊,如圖 8 所示。

圖 8. 死區時間模式控制的時序圖

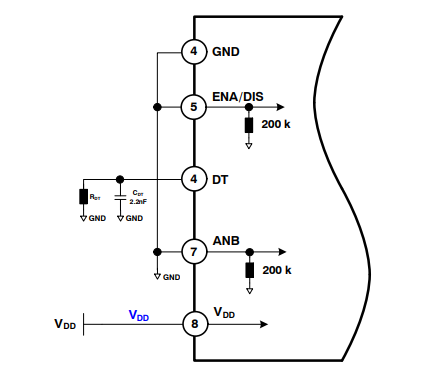

當 DT 引腳浮空時,建議將 DT 引腳直連 GND 引腳,或使用 2.2 nF 電容,分別如圖 9 的中間和下方圖形所示。

圖 9. ANB、ENA/DIS 引腳適當濾波的示例

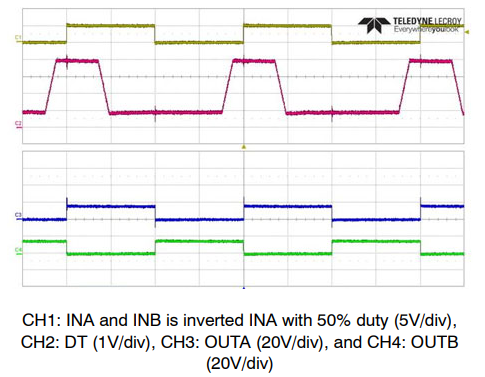

如圖 10 所示,當 DT 引腳浮空時,最小死區時間 (tDTMIN) 典型值為 10 ns,不允許驅動器兩個輸出(OUTA 和 OUTB)之間交叉導通。

圖 10. DT 引腳浮空時的實驗波形

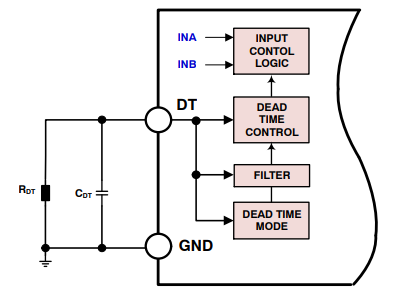

如果通過死區時間控制電阻對死區時間進行編程,應并聯放置一個值大于 2.2nF 的電容,以提高快速開關瞬變期間的抗擾度,如圖 11 所示。

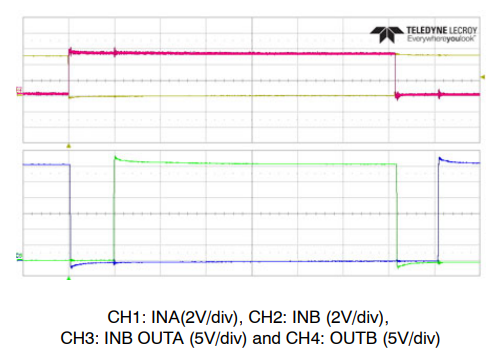

當 DT 引腳電阻在 1 kΩ 和 300 kΩ 之間時,外部電阻 (RDT) 控制死區時間。圖 12 顯示了 DT 引腳具有 100 kΩ 電阻時的實驗結果。

圖 11. 死區時間引腳適當濾波的示例

圖 12. DT 引腳具有 100 kΩ 電阻時的實驗波形

如果無需死區時間,應將死區時間引腳連接到 VDD 以停用 DT 電路,如圖 13 所示,實驗結果如圖 14 所示。

圖 13. 將 DT 引腳連接到 VDD 引腳以停用 DT 電路的示例

圖 14. DT 引腳短接 VDD 時的實驗波形

死區時間控制功能根據 DT 引腳電壓提供三種工作模式。

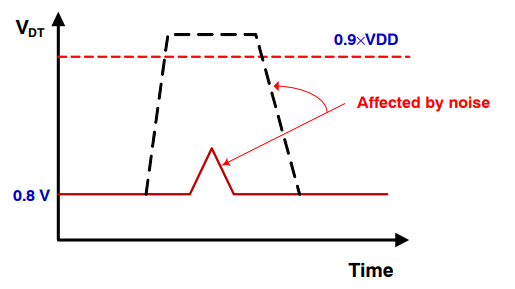

當 DT 引腳浮空時,在浪涌測試期間(如雷擊浪涌)DT 引腳上可能有異常噪聲。盡管 DT 引腳內部對于開路和短路檢測分別有 3μs 和 2μs 的濾波時間,但如果 DT 引腳電壓受噪聲信號影響而超過額定電壓電平,死區時間控制模式仍會變為模式 C,因為死區時間控制模式變更取決于 DT 引腳電壓。

例如,如果 DT 引腳電壓低于 0.9 × VDD,則當 DT 引腳浮空時,死區時間具有最小值(典型值 10 ns),DT 引腳的穩態電壓約為 0.8 V。

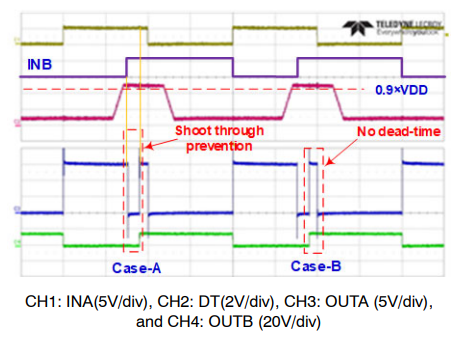

如果噪聲導致 DT 引腳電壓超過 0.9 × VDD 且持續 3μs 以上,死區時間控制模式會被禁用,這意味著兩個通道之間沒有死區時間,如圖 15 所示。

圖 15. DT 引腳浮空時的異常波形

因此,建議為 RDT 增加一個 2.2nF 或以上的陶瓷電容 (CDT),并使其靠近芯片,以實現更好的抗擾度和兩個通道之間更好的死區時間匹配,如圖 16 所示。

主要考量是通過 RDT 的電流用于設置死區時間,此電流隨著 RDT 值的增大而減小。

圖 16. 死區時間的更詳細框圖

測試結果顯示,對于 5 V 情況的 VDD,當 DT 引腳浮空且外部施加的電壓低于 0.9 × VDD 時,死區時間控制模式不變,即仍為模式 A,如圖 17 所示。

圖 17. DT 引腳浮空且外部施加的電壓低于 0.9 × VDD 時的實驗波形

但是,對于 5 V 情況的 VDD,當 DT 引腳浮空且外部施加的電壓高于 0.9 × VDD 并持續 3μs 以上時,死區時間模式從模式 A 變為模式 C,例如圖 18 中的情況 B 所示。如情況 A 所示,針對 DT 引腳開路檢測,其內部有 3μs 濾波時間,因此死區時間控制模式并未改變,防止擊穿功能仍在運行。

第三部分將于下周發布,敬請期待!

意猶未盡?

掃描下方二維碼填寫信息

獲取英文原版完整應用筆記

點個星標,茫茫人海也能一眼看到我

原文標題:使用隔離式柵極驅動器的設計指南(二):電源、濾波設計與死區時間

文章出處:【微信公眾號:安森美】歡迎添加關注!文章轉載請注明出處。

-

安森美

+關注

關注

33文章

2076瀏覽量

95776

原文標題:使用隔離式柵極驅動器的設計指南(二):電源、濾波設計與死區時間

文章出處:【微信號:onsemi-china,微信公眾號:安森美】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

使用隔離式柵極驅動器的設計指南(二):電源、濾波設計與死區時間

使用隔離式柵極驅動器的設計指南(二):電源、濾波設計與死區時間

評論