》nameWhenByFile

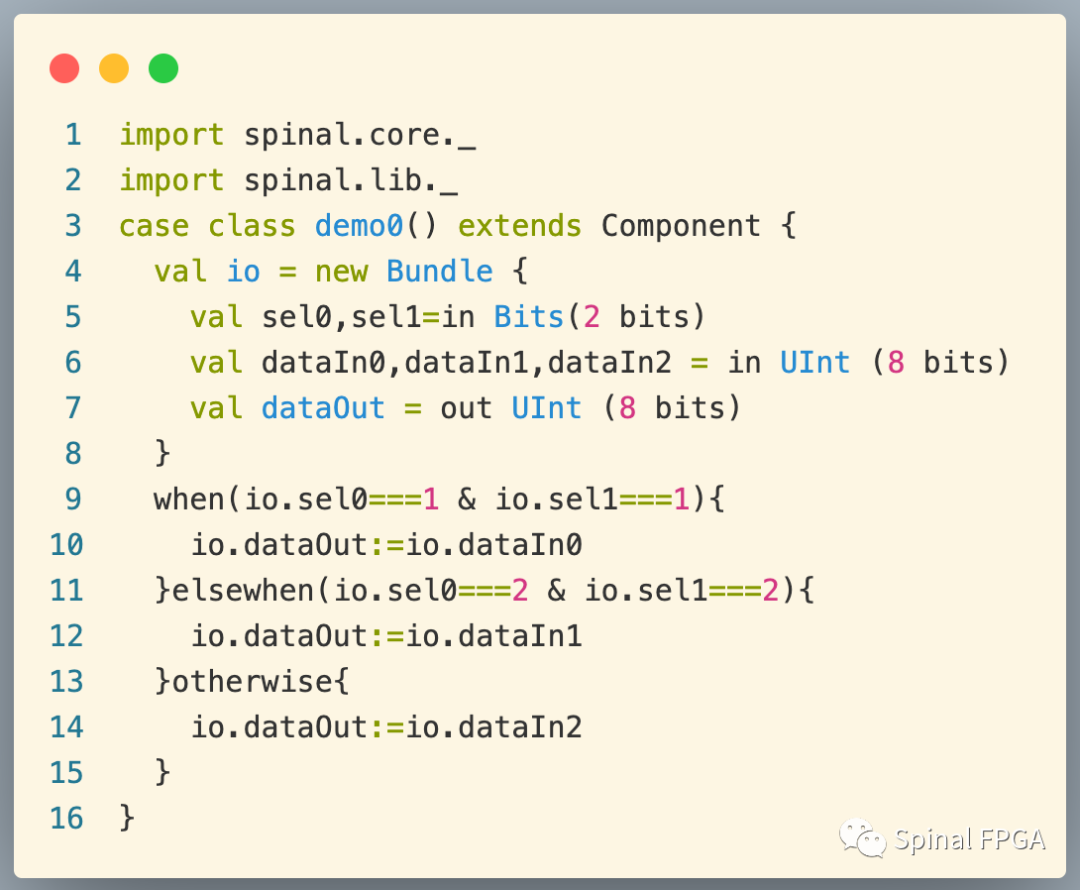

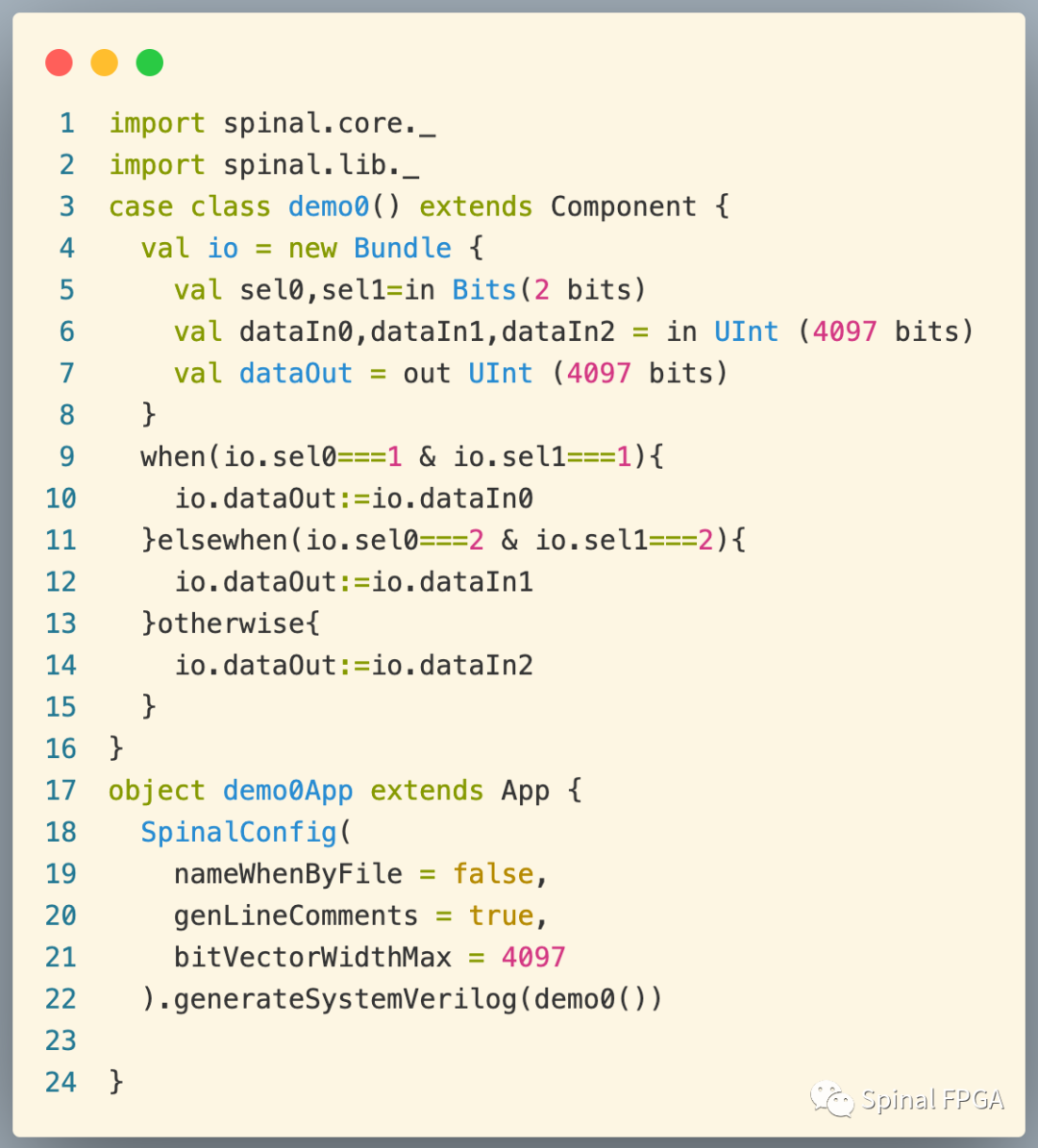

測(cè)試代碼如下:

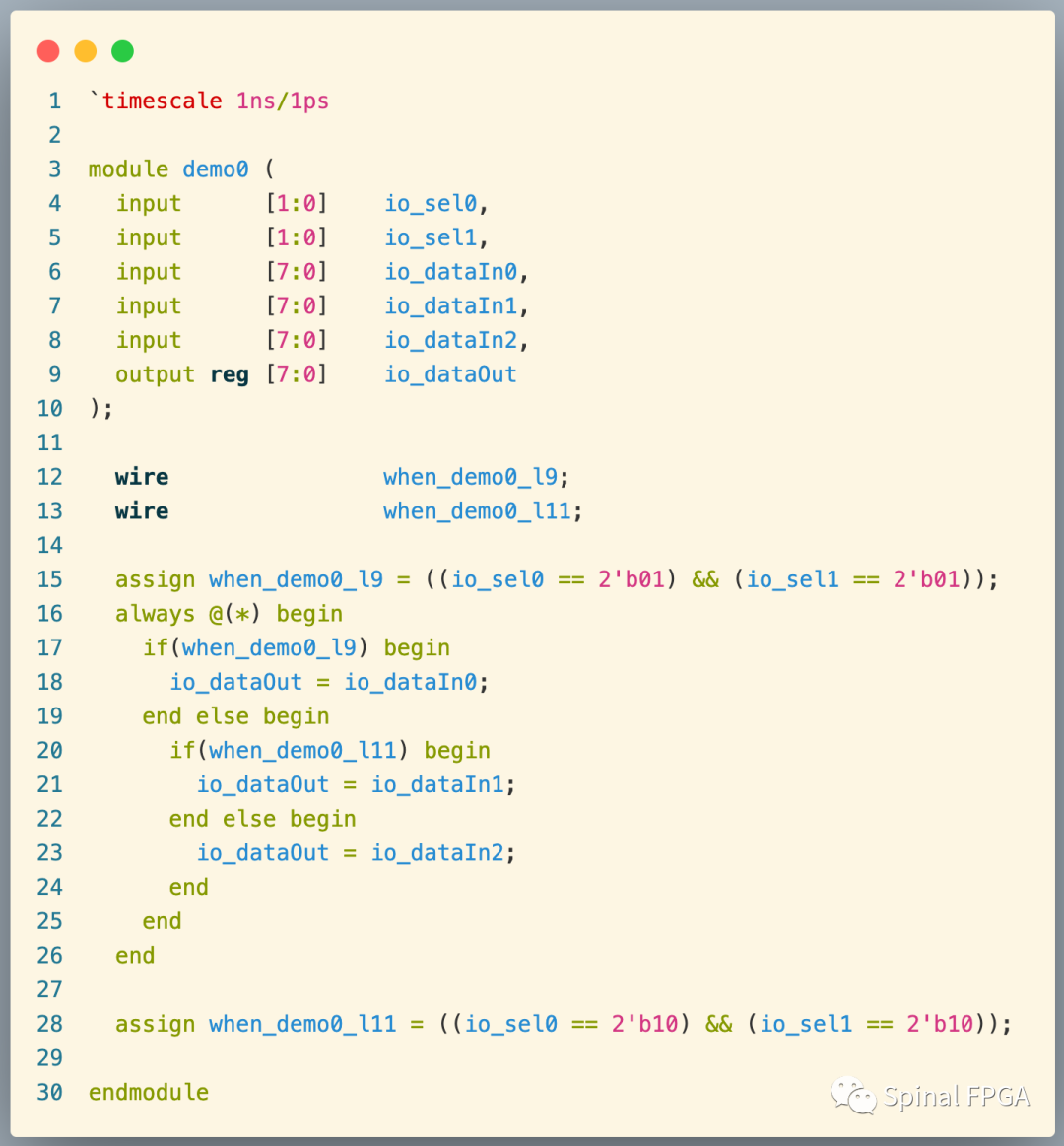

當(dāng)我們采用SpinalSystemVerilog(demo0())的方式生成RTL代碼時(shí)其生成的代碼風(fēng)格如下:

在SpinalHDL中對(duì)于when的使用,when中所包含的條件往往會(huì)生成以一個(gè)when+fileName+行號(hào)的變量來替代,看起來無非代碼多了幾行,并不影響功能。

因?yàn)橛行刑?hào)的引入,我們一旦對(duì)SpinalHDL代碼中這部分代碼哪怕是添加了幾行注釋也會(huì)引起生成代碼的部分修改,雖然不影響功能,但對(duì)于那些喜歡看RTL代碼的人就顯得略顯得不爽了。

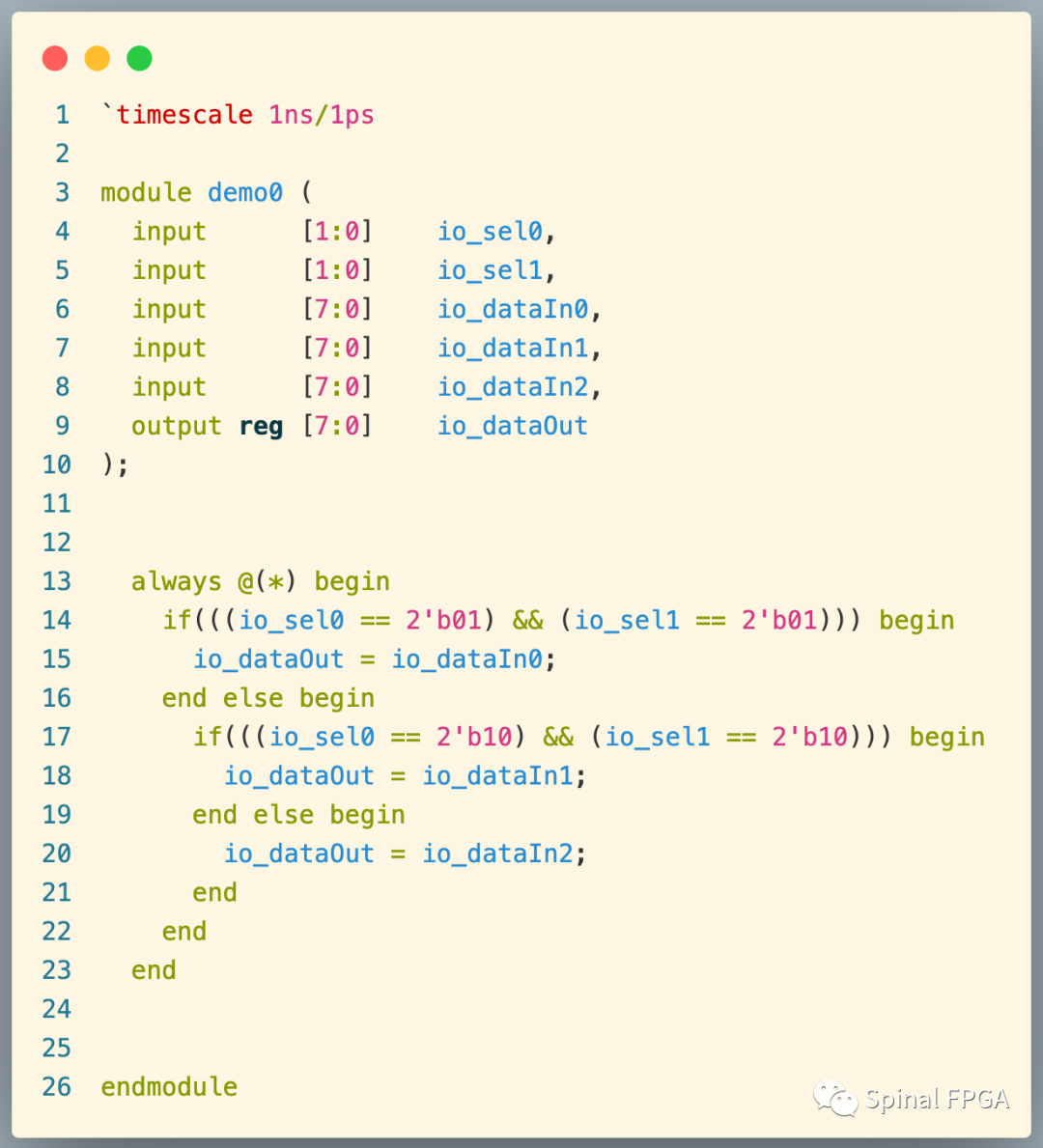

對(duì)于when的使用,可以在生成RTL代碼時(shí)采用下面的形式來生成:

SpinalConfig( nameWhenByFile=false ).generateSystemVerilog(demo0())

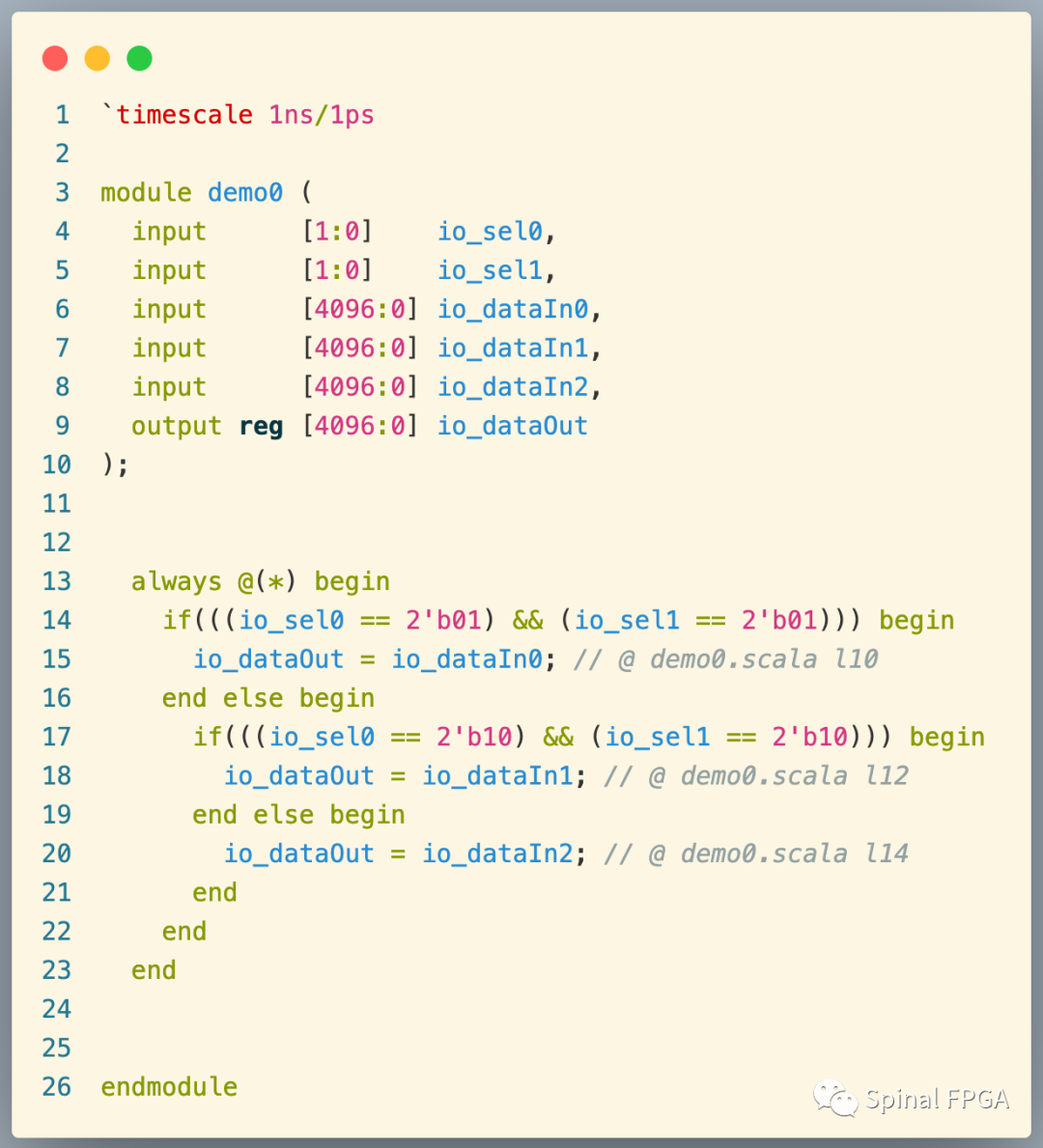

生成代碼如下:

如此生成的代碼不會(huì)再對(duì)when語句聲明單獨(dú)的變量,代碼看起來和那些采用Verilog寫代碼的人毫無差異吧~

這對(duì)于生層的RTL盡可能減少非必要的信號(hào)名稱變化。

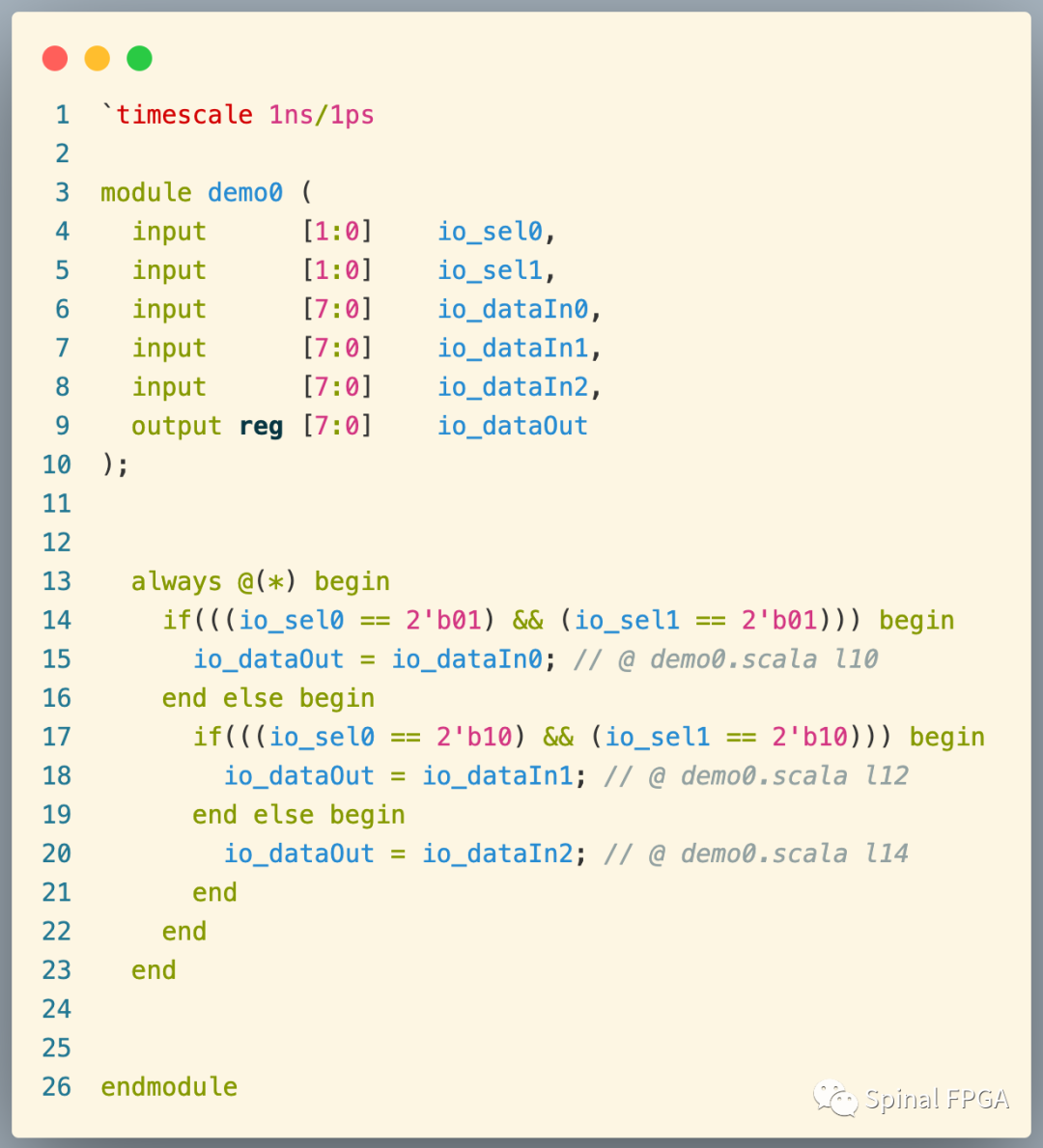

》genLineComments

更近一步,對(duì)于代碼生成時(shí)采用下面的形式生成:

SpinalConfig(

nameWhenByFile = false,

genLineComments = true

).generateSystemVerilog(demo0())

此時(shí)生成的代碼風(fēng)格如下:

當(dāng)genLineComments聲明為true時(shí),在生成RTL代碼中會(huì)標(biāo)注映射對(duì)應(yīng)的SpinalHDL代碼行號(hào),這對(duì)于初學(xué)者在對(duì)比生成的RTL代碼學(xué)習(xí)SpinalHDL還是非常的有幫助~

》bitVectorWidthMax

SpinalHDL中對(duì)于信號(hào)位寬默認(rèn)是最大不超過4096(Intel DDR校準(zhǔn)控制IP里面就有信號(hào)位寬就是4096 bit位寬),當(dāng)設(shè)計(jì)里定義了信號(hào) 位寬超過4096,則會(huì)在生成RTL代碼時(shí)報(bào)錯(cuò),可通過SpianlConfig中的bitVectorWidthMax對(duì)最大位寬進(jìn)行修改:

審核編輯:劉清

-

DDR

+關(guān)注

關(guān)注

11文章

754瀏覽量

69121 -

Verilog

+關(guān)注

關(guān)注

30文章

1374瀏覽量

114526 -

RTL

+關(guān)注

關(guān)注

1文章

394瀏覽量

62656

原文標(biāo)題:SpinalConfig Tips——讓代碼優(yōu)雅點(diǎn)兒

文章出處:【微信號(hào):Spinal FPGA,微信公眾號(hào):Spinal FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

在SpinalHDL中如何快速地實(shí)現(xiàn)總線連接

安規(guī)三項(xiàng)

關(guān)于SpinalHDL中的驗(yàn)證覆蓋率收集簡(jiǎn)單說明

在SpinalHDL中關(guān)于casez的使用

在SpinalHDL中的代碼組織結(jié)構(gòu)如何實(shí)現(xiàn)Component參數(shù)化設(shè)計(jì)呢

如何在SpinalHDL里啟動(dòng)一個(gè)仿真

三項(xiàng)閃聯(lián)國(guó)際標(biāo)準(zhǔn)文本明年2月公布

iOS 14和tvOS 14系統(tǒng)更新,HomeKit迎來三項(xiàng)重要功能

在SpinalHDL中的對(duì)應(yīng)關(guān)系及聲明形式

SpinalHDL中Bundle數(shù)據(jù)類型的轉(zhuǎn)換

針對(duì)電子設(shè)備中基于MEMS顯示的三項(xiàng)預(yù)測(cè)

國(guó)際認(rèn)證三項(xiàng)電池CTL決議最新動(dòng)態(tài)

不同型號(hào)的三項(xiàng)電容可以串聯(lián)嗎?

分享下SpinalHDL中SpinalConfig中的三項(xiàng)參數(shù)

分享下SpinalHDL中SpinalConfig中的三項(xiàng)參數(shù)

評(píng)論