目錄預覽

1ICACHE 和 DCACHE 概述

2ICACHE 和 DCACHE 主要特性

3 ICACHE 和 DCACHE 的性能與功耗

4 結論

1.ICACHE 和 DCACHE 概述

本節概述了嵌入在基于 STM32 Arm Cortex內核的微控制器中的 ICACHE 和 DCACHE 接口。詳細介紹了 ICACHE 和 DCACHE 框圖架構以及在系統架構中的集成。

1.1 STM32L5 系列智能架構

此架構基于總線矩陣,允許多個主設備(Cortex-M33、DMA1/2 和 SDMMC1)訪問多個從設備(如Flash 存儲器、SRAM1/2、OCTOSPI1 或 FSMC)。

下圖描述了 STM32L5 系列智能架構。

由于將 8-Kb 的 ICACHE 接口引入其 C-AHB 總線,通過快速總線從內部存儲器(Flash 存儲器、SRAM1 或SRAM2)或通過慢速總線從外部存儲器(OCTOSPI1 或 FSMC)提取代碼或數據時,Cortex-M33 的性能有所提升。

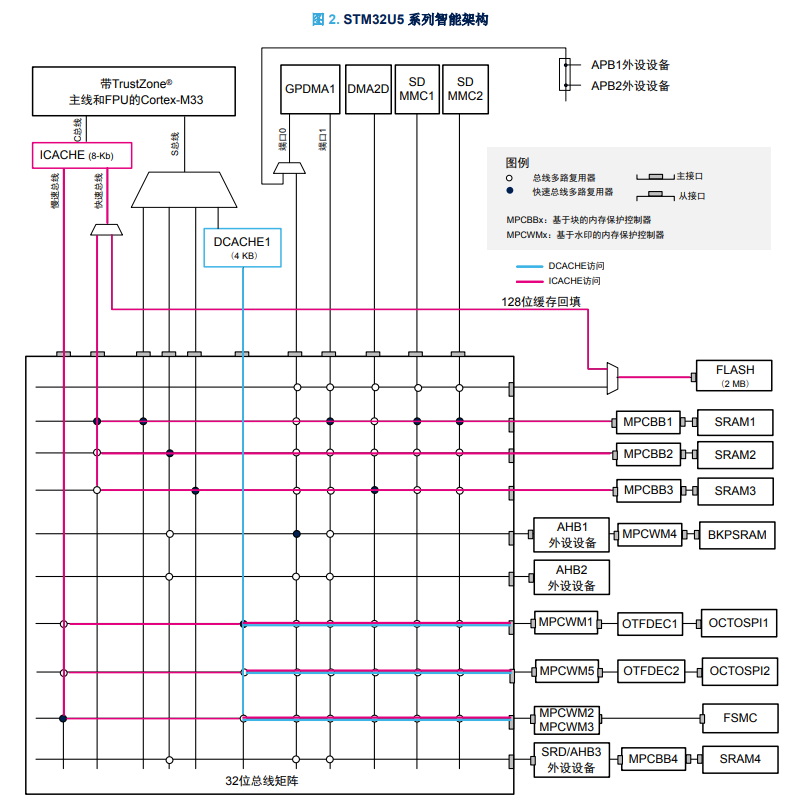

1.2 STM32U5 系列智能架構

此架構基于總線矩陣,允許多個主設備(Cortex-M33、GPDMA1、DMA2D 和SDMMC1/2)訪問多個從設備(如 Flash 存儲器、SRAM1/2/3/4、BKPSRAM、OCTOSPI1/2 或 FSMC)。

下圖描述了 STM32U5 系列智能架構。

其 C-AHB 總線引入了 8-Kb 的 ICACHE 接口,通過快速總線從內部存儲器(Flash 存儲器、SRAM1、SRAM2 或SRAM3)或通過慢速總線從外部存儲器(OCTOSPI1、OCTOSPI2 或 FSMC)提取代碼或數據時,Cortex-M33 的性能有所提升。其 S-AHB 總線引入了 4-Kb 的 DCACHE 接口,提高了外部存儲器(OCTOSPI1、OCTOSPI2 或 FSMC)的數據流量。

1.2 ICACHE 框圖

ICACHE 框圖如下圖所示:

ICACHE 存儲器包括:

? 具有以下元素的 TAG 存儲器:

– 指示將哪些數據包含在緩存數據存儲器中的地址標簽

– 有效位

? 數據存儲器,包含緩存的數據

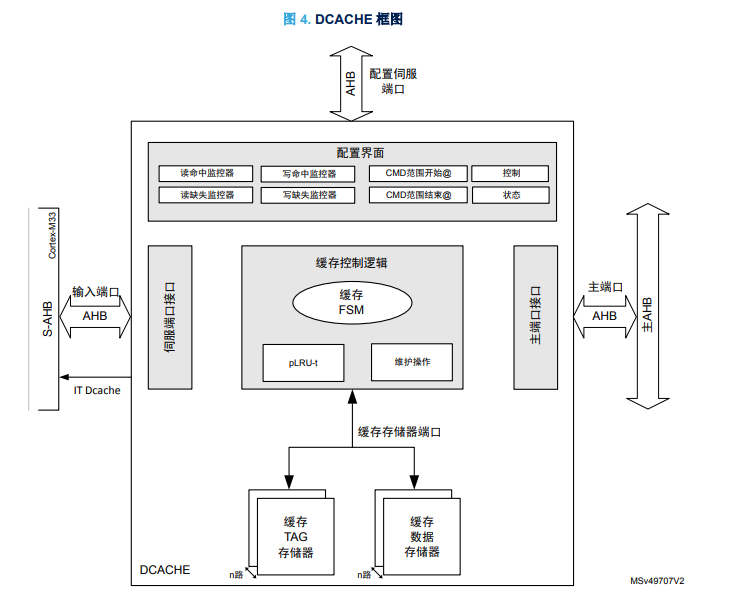

1.4DCACHE 框圖

DCACHE 框圖如下圖所示。

DCACHE 存儲器包括:

? 具有以下元素的 TAG 存儲器:

– 指示將哪些數據包含在緩存數據存儲器中的地址標簽

– 有效位 特權位

– dirty 位

? 數據存儲器,包含緩存的數據

長按掃碼關注公眾號

更多資訊,盡在STM32

▽點擊“閱讀原文”,可下載原文檔

原文標題:應用筆記|使用 STM32 緩存來優化性能與功率效率

文章出處:【微信公眾號:STM32單片機】歡迎添加關注!文章轉載請注明出處。

-

單片機

+關注

關注

6076文章

45495瀏覽量

670443 -

STM32

+關注

關注

2309文章

11162瀏覽量

373475

原文標題:應用筆記|使用 STM32 緩存來優化性能與功率效率

文章出處:【微信號:STM32_STM8_MCU,微信公眾號:STM32單片機】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

探秘CSD87351Q5D:高效同步降壓NexFET?功率模塊的卓越性能與應用

探秘DS2731:緩存內存電池備份管理IC的卓越性能與應用

n型TOPCon電池中通過氘化/氫化混合策略提升鈍化性能

通過優化代碼來提高MCU運行效率

蜂鳥E203內核優化方法

伺服電機編碼器安裝與維護最佳實踐:優化性能與延長系統壽命

n型背接觸BC電池:通過SiNx/SiON疊層優化減反射與表面鈍化性能

高性能緩存設計:如何解決緩存偽共享問題

鴻蒙5開發寶藏案例分享---長列表性能優化解析

HarmonyOS優化應用內存占用問題性能優化一

快手上線鴻蒙應用高性能解決方案:數據反序列化性能提升90%

MCU緩存設計

Ringbuffer的性能優化方法

應用筆記|使用 STM32 緩存來優化性能與功率效率

應用筆記|使用 STM32 緩存來優化性能與功率效率

評論