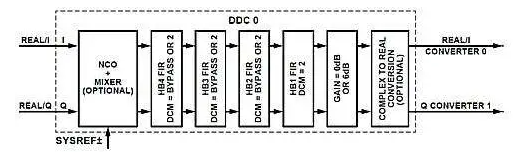

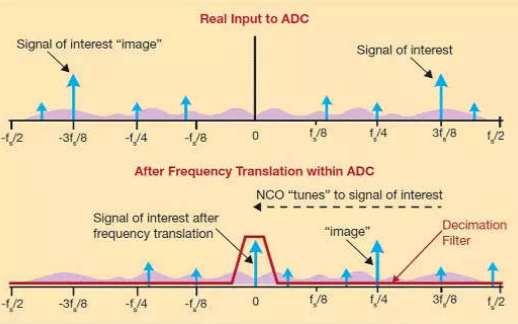

DDC包括一個抽取濾波器,可以避免傳統(tǒng)的輸入抗混疊濾波要求,同時以數(shù)字方式濾除目標基帶信號,同時處理的數(shù)據(jù)有效載荷凈降低。您透露您正在測試頻率計劃,并希望看到DDC通帶和過渡帶之外的輸入頻率確實衰減了>100 dB(見下圖)。您在啟用抽取濾波器的情況下運行ADC輸出數(shù)據(jù)的FFT,結(jié)果發(fā)現(xiàn)輸出頻譜中的雜散僅下降90 dB,而不是預期下降的>100 dB。如果刪除輸入信號,雜散就會消失。你問它從哪里來?進入阻帶的信號怎么會在通帶中引起雜散?

當您開始考慮ADC的板載DSP選項時,有時很容易停止考慮模數(shù)轉(zhuǎn)換器的行為。因此,雖然上圖準確地描述了抽取濾波器在基帶奈奎斯特區(qū)的響應,但它沒有涵蓋轉(zhuǎn)換器中其他奈奎斯特區(qū)的響應。在這種情況下,濾波器的響應將混疊到所有高階奈奎斯特區(qū)。在下圖中,您可以看到前五個奈奎斯特區(qū)域的響應。還注意到神秘雜散,它是帶外輸入音的混疊二次諧波。

您指出,在測試設(shè)置中,不存在模擬輸入抗混疊濾波器。因此,神秘雜散的根本原因有了答案——數(shù)字濾波器無法消除模擬側(cè)的頻譜內(nèi)容。這很有趣地說明了更高的采樣速率轉(zhuǎn)換器如何降低模擬輸入濾波要求,但您仍然不能忽視采樣系統(tǒng)中的混疊規(guī)律。高采樣速率和DDC允許在前端不使用激進的模擬濾波器來處理fS/4和fS/2之間的阻塞信號,而一個不太激進的濾波器將消除3fS/4及以后的雜散。

審核編輯:郭婷

-

濾波器

+關(guān)注

關(guān)注

162文章

8412瀏覽量

185715 -

變頻器

+關(guān)注

關(guān)注

256文章

7283瀏覽量

155423 -

adc

+關(guān)注

關(guān)注

100文章

7511瀏覽量

555977

發(fā)布評論請先 登錄

數(shù)字下變頻器的發(fā)展和更新(第一部分)

寬頻ADC中的數(shù)字下變頻研究

級聯(lián)型高壓變頻器輸出諧波研究

基于FPGA的數(shù)字下變頻器的設(shè)計與實現(xiàn)

數(shù)字上/下變頻器簡介:VersaCOMM?可重構(gòu)數(shù)字轉(zhuǎn)換器

基于FPGA的數(shù)字下變頻器(DDC)的設(shè)計

數(shù)字下變頻器是怎么回事

下變頻器輸入信號幅度對下變頻的影響

如何通過下變頻器幫助抑制高頻干擾

ADC數(shù)字下變頻器:復雜抽取示例

數(shù)字下變頻器功能的高速ADC的輸出頻譜研究

數(shù)字下變頻器功能的高速ADC的輸出頻譜研究

評論