驗證和testbench

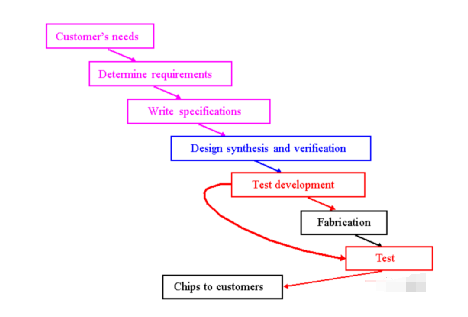

Design Verication(DV)是任何產品開發中必不可少的步驟。 作為質量測試的一部分,DV確保設計的產品是與預期的產品spec相同。 不幸的是,許多設計項目沒有完成徹底的DV導致產品不符合客戶要求期望并需要昂貴車成本去修改設計。

可以和DV結合使用的質量測試手段:Requirements Management、Configuration Management、FMEA(Function Safety)、Formal(形式驗證)、DFT。

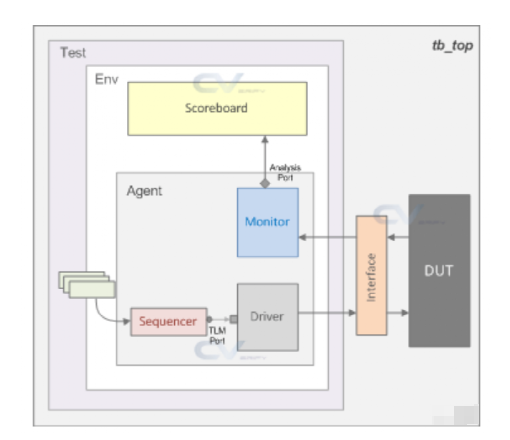

testbench是一種驗證的手段。 首先,任何設計都是會有輸入輸出的。 但是在軟環境中沒有激勵輸入,也不會對你設計的輸出正確性進行評估。 那么此時便有一種,模擬實際環境的輸入激勵和輸出校驗的一種“虛擬平臺”的產生。 在這個平臺上你可以對你的設計從軟件層面上進行分析和校驗,這個就是testbench的含義。

testbench里面包含了兩個東西。 1激勵生成:這個只用來生成輸出,他自己沒有輸入,只是按照一定的規律去給你的設計激勵,激勵通過設計的輸入端口送到你的設計中。 其余的事情不管。 這里的激勵,都是預先設想好的,比如根據某個協議,或者某種通信方式傳遞。 2輸出校驗:校驗你的輸出。 他所管的事情就是,接收你設計的輸入,然后通過校驗輸出,找出對應的問題。

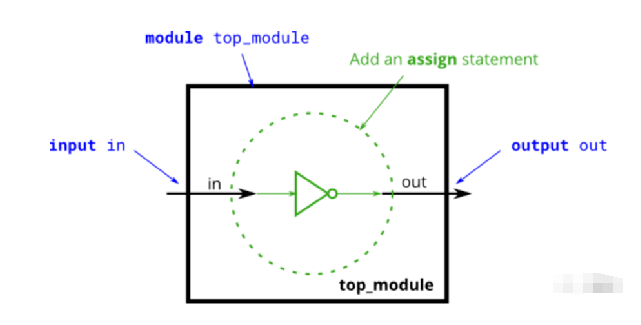

如大家所知,verilog是模塊化設計,設計的時候我們首先需要考慮:模塊名、模塊的功能、端口數量和端口的input/output/inout屬性。 然后需要思考:用什么語句和命令實現該模塊。

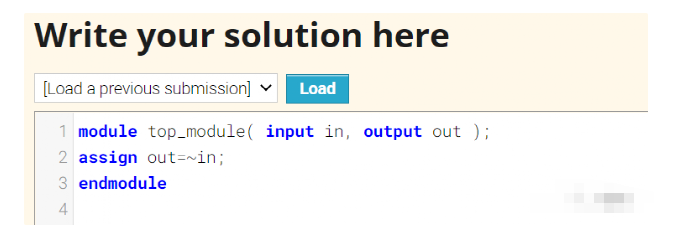

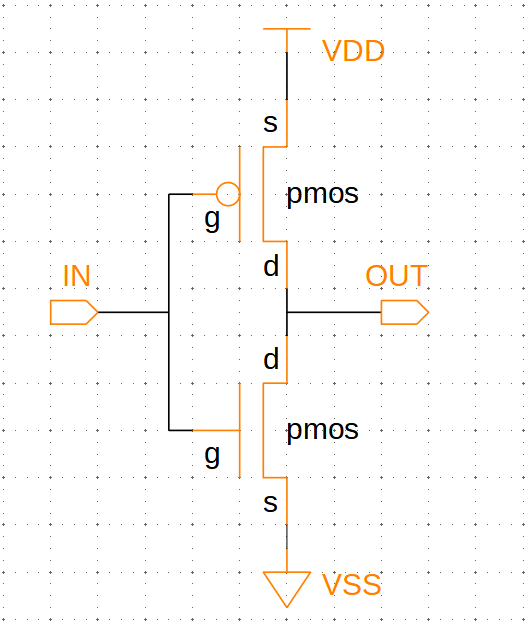

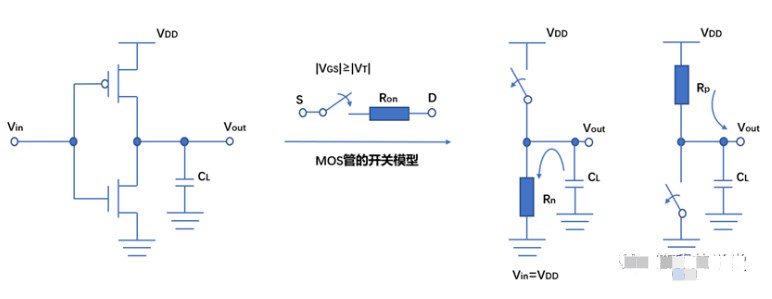

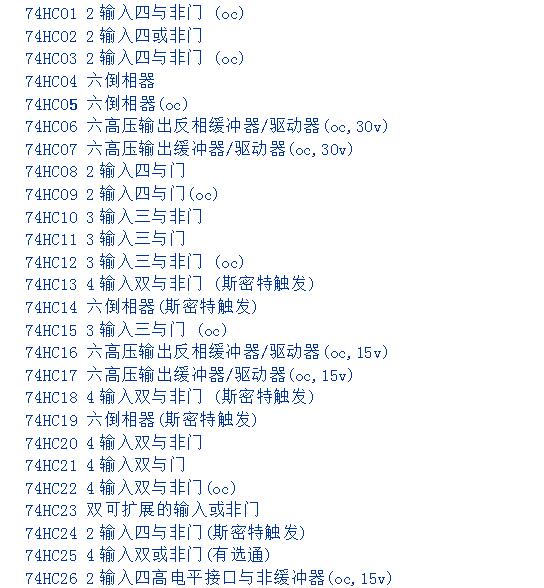

對于反相器,一共只有兩個端口,分別是輸入和輸出,輸入和輸出之間就是一個單純的取反關系,可以用數據流描述語句assign對其進行描述,用取反運算符“~”對其進行數據運算。

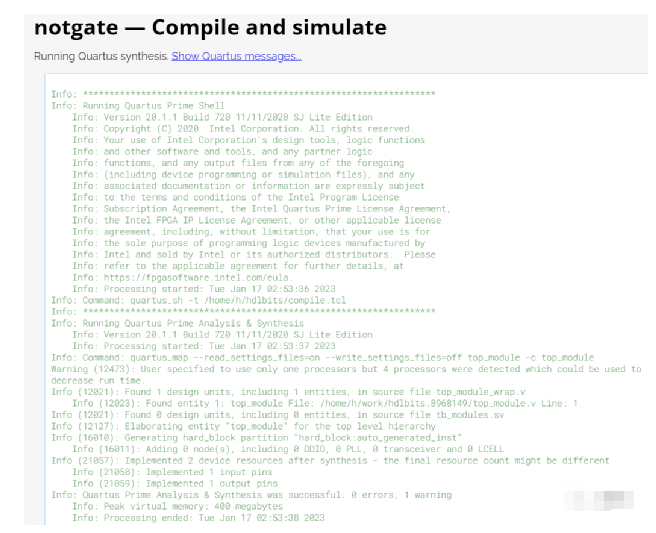

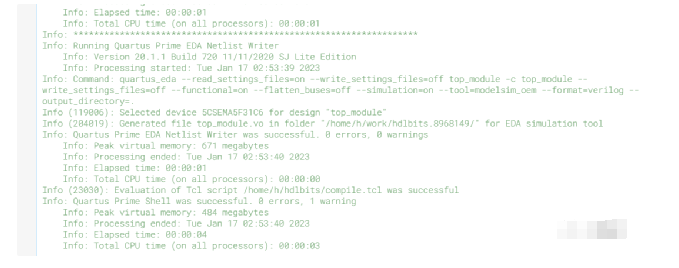

使用在線綜合器對其進行綜合

使用在線仿真器對其進行仿真

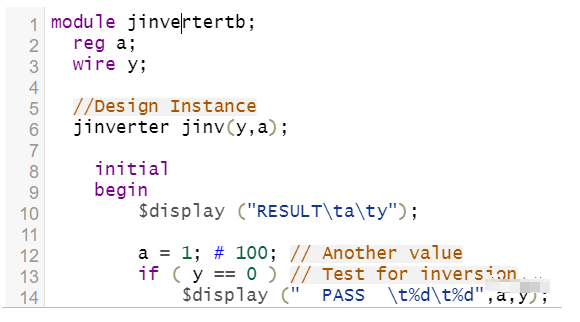

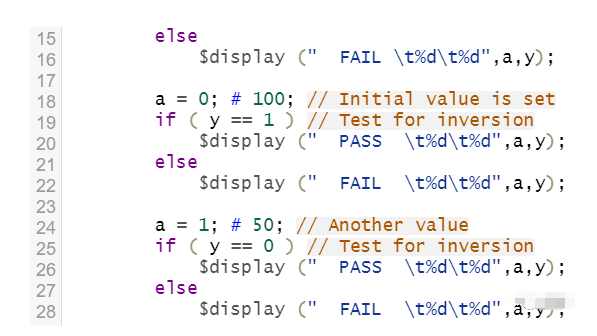

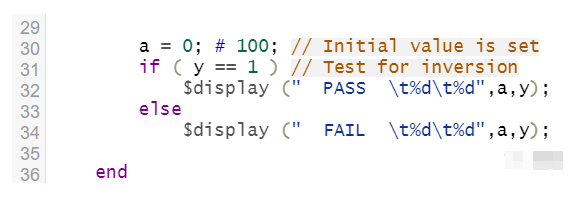

一種反相器testbench示例:

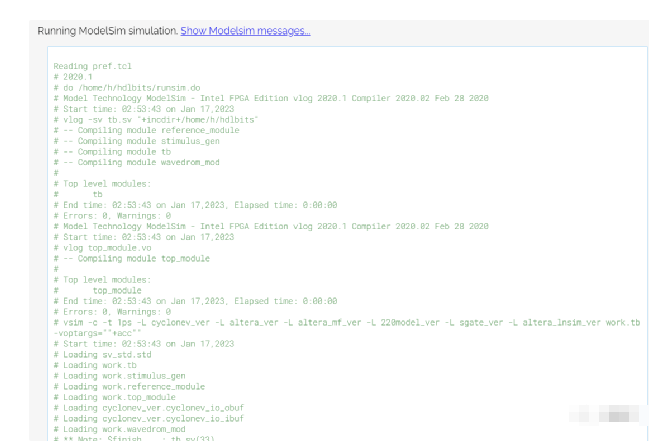

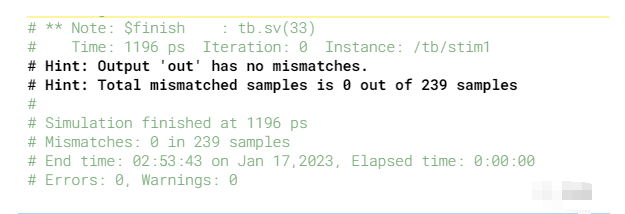

在線仿真器使用的是其內置的testbench進行仿真:

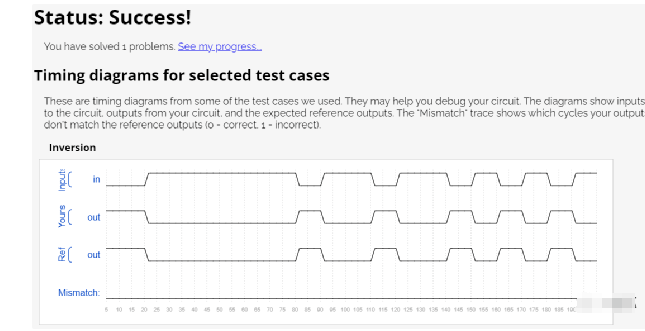

仿真波形

-

反相器

+關注

關注

6文章

332瀏覽量

45244 -

仿真

+關注

關注

55文章

4505瀏覽量

138493 -

DV

+關注

關注

0文章

27瀏覽量

34493 -

Verilog

+關注

關注

30文章

1374瀏覽量

114597 -

design

+關注

關注

0文章

165瀏覽量

47578

發布評論請先 登錄

窗口電壓比較器和反相器連接問題

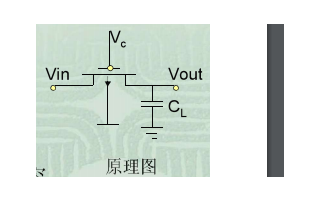

virtuoso中進行CMOS反相器和靜態寄存器的電路設計

反相器的輸出不對!

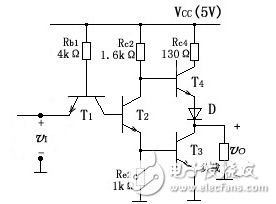

TTL反相器的基本電路(六款TTL反相器的基本電路設計原理圖詳解)

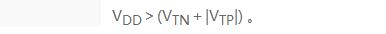

cmos反相器設計電路圖

MOS反相器和CMOS反相器的詳細資料說明

反相器的verilog設計和仿真

反相器的verilog設計和仿真

評論