Address collision 指的是RAM的兩個port同時訪問相同的地址可能導致數據發生錯誤的情況。在Xilinx中,不同的RAM,不同的RAM配置會導致address collision時不同的數據結果。

Distributed RAM

對于DRAM,寫數據是 synchronous write,需要一個時鐘周期, 讀數據是 asynchronous read,當前時鐘周期就能讀出數據。因此當在某一個cycle讀寫同時訪問同一地址時,讀數據是 old data,即該地址原存放的數據而不是新要寫入的數據。

Block RAM

BRAM的讀寫都是 synchronous。BRAM的兩個Port分別為 PortA 和 PortB。

我們可以將 BRAM address collision 分為以下三類。

PortA 和 PortB 同時讀數據

兩個Port都會正確讀出該地址中的數據。

PortA 和 PortB 同時寫入數據

該地址最終被寫入的數據是 non-deterministic。因此設計中要避免兩個port同時寫數據的address collision。

PortA 寫數據同時 PortB 讀數據,或者是 PortA 讀數據同時 PortB 寫數據

在這種情況下,數據總是會被正確寫入到RAM中,但是讀出的數據內容則依賴于BRAM的配置。BRAM的write mode可以配置為三種模式,write first,read first 和 no change。

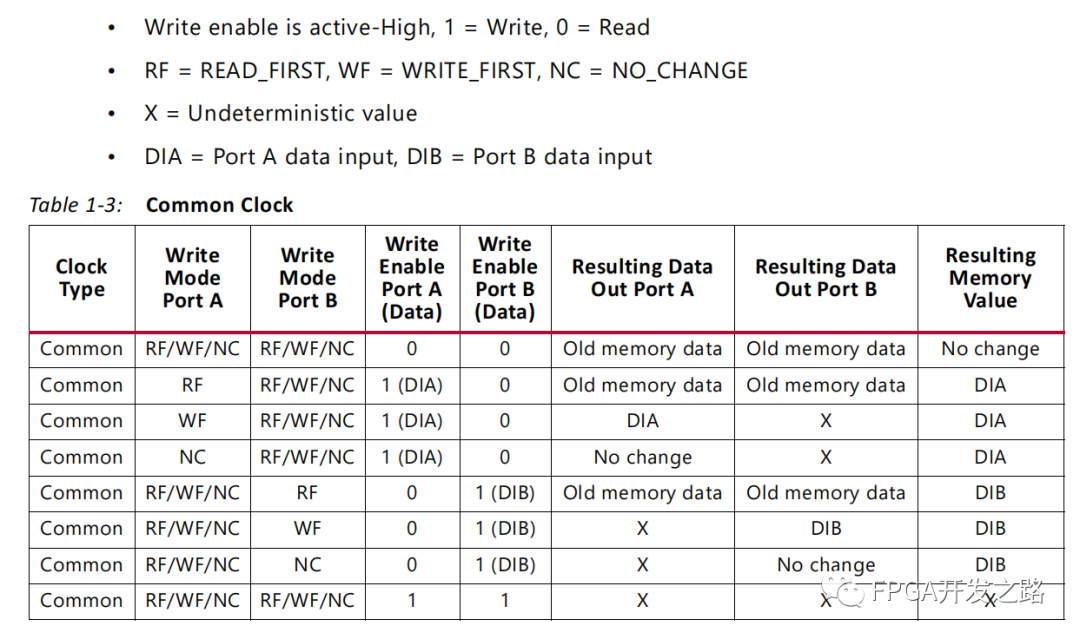

下圖為不同配置下的數據讀寫結果。可以看到當 write port 配置為 READ_FIRST時,不管 read port 如何配置,都會讀出 old data。而當 write port 配置為 WRITE_FIRST 或 NO_CHANGE時,不管 read port 如何配置,讀數據都是 X,即 undeterministic。因此在可能發生address collision 的BRAM,一般將兩個 port都配置為 READ_FIRST,以確保數據讀出的正確。

Ultra RAM

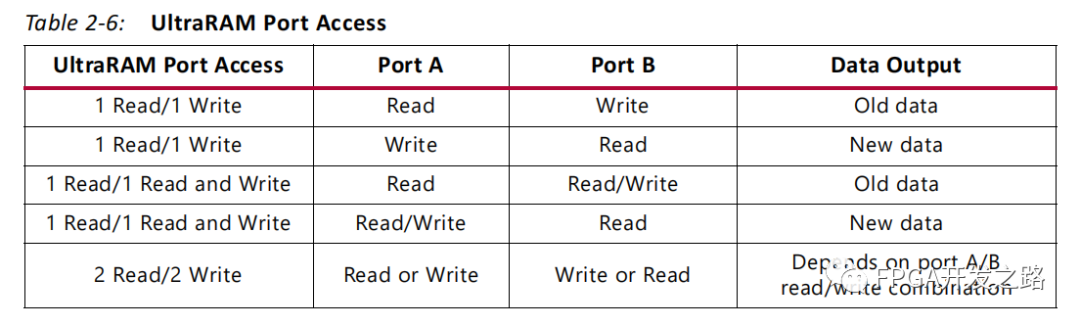

URAM的讀寫也都是 synchronous。URAM比較有意思的一點是,PortA 總是先于 PortB 執行操作,因此在 address collision 我們會看到不同于BRAM的結果。

PortA寫,PortB讀。PortB 會讀出new data。(因為PortA先執行,所以在PortB讀執行時,new data已經寫入RAM中了)

PortA讀,PortB寫。PortA 會讀出old data。(同樣的,這也是因為PortA先執行)

PortA寫,PortB寫。最終該地址寫入的值是PortB的值。(PortB因為后執行會覆蓋PortA寫的值)

Reference

《UltraScale Architecture Configurable Logic Block》

《UltraScale Architecture Memory Resources》

審核編輯 :李倩

-

數據

+關注

關注

8文章

7335瀏覽量

94774 -

RAM

+關注

關注

8文章

1399瀏覽量

120568 -

Xilinx

+關注

關注

73文章

2200瀏覽量

131147

原文標題:Xilinx RAM Address Collision

文章出處:【微信號:FPGA開發之路,微信公眾號:FPGA開發之路】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Linux如何防止內存沖突?

CW32F030 RAM存儲器的介紹

顯存讀寫沖突造成花屏解決方案

如何高效修改西門子PLC的相同IP地址

芯源MCU的RAM存儲器的操作

工業NAT網關實現PLC、機床等設備IP地址沖突的解決方案

ram ip核的使用

國外老舊設備出現IP沖突無法上網如何解決

N9H30如何從SPI閃存將應用程序加載到RAM地址0x0?

IP地址沖突導致德國站群服務器斷網的解決方法?

編程軟件連接PLC出現IP沖突時如何解決?

CNC的IP地址相同沖突如何解決?

國外PLC出現IP相同沖突如何解決

Xilinx RAM地址沖突

Xilinx RAM地址沖突

評論