同步設計和異步設計的特點

同步邏輯是時鐘之間有固定的因果關系。異步邏輯是各時鐘之間沒有固定的因果關系。

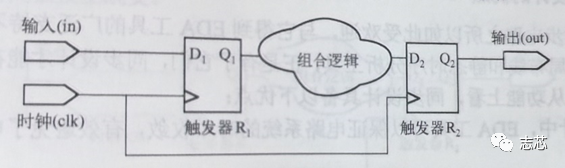

同步電路特點:時鐘個數只有一個,電路中觸發器的時鐘輸入端連接同一個時鐘脈沖源,所有觸發器的狀態變化都與所加的時鐘脈沖信號同步;由于只有一個時鐘,所以整個電路所有時鐘應該是同源同相的;一般會濾掉毛刺,不需要特別考慮競爭與冒險;有利于靜態時序分析;設計的電路具有強耦合關系,不利于面積優化與低功耗優化,不靈活;存在時鐘偏斜問題。

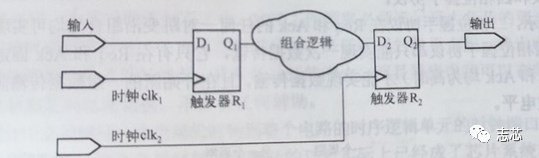

異步電路特點:電路中沒有統一的時鐘(可以有多個時鐘),有些觸發器的時鐘輸入端與時鐘脈沖源相連(與時鐘脈沖源同步),其余觸發器狀態變化不與時鐘脈沖源同步;由于有多個時鐘,因此有些時鐘是同源不同相的,有些是不同源的;很大概率存在競爭與冒險;一般無法對異步電路進行靜態時序分析;電路耦合關系很弱,設計比較靈活,相同條件下比同步電路功耗低;不存在時鐘偏斜問題。

做模塊劃分時應該考慮哪些問題

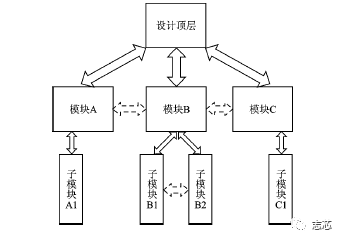

結構層次化是設計的一種基本思想,需要注意:結構不宜太深,否則綜合時面積過大,綜合工具會默認做扁平化處理;頂層設置不宜過于復雜,主要完成諸如輸入輸出,模塊調用與實例化,全局時鐘,三態總線,全局復位等等簡單的功能;雙向的信號最好只在頂層出現;子模塊之間最好不要有跨層次的接口;合理考慮子模塊的功能、結構、時序等。

模塊劃分的技巧:對每個同步時序設計的子模塊的輸出使用寄存器處理;將相關的邏輯或者可以復用的邏輯寫在一起;將不同優化目標的部分分開,時序的和面積的分開處理;將時序寬松的分到同一個模塊;將存儲器件獨立劃分;合理規劃模塊的規模。

圖1模塊劃分示意圖

組合邏輯設計有哪些考慮點

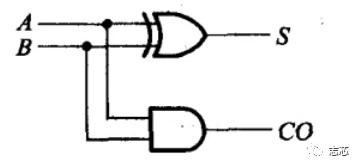

根據邏輯功能的不同特點,可以將數字電路分成兩大類,一類稱為組合邏輯電路(簡稱組合電路),另一類稱為時序邏輯電路(簡稱時序電路)。

常見組合邏輯電路包括編碼器、譯碼器、數據選擇器、數值比較器、加法器、函數發生器、奇偶校驗器/發生器等。

圖2組合邏輯之半加器

組合邏輯設計注意事項包括:避免組合邏輯反饋環路(容易毛刺、振蕩、時序違規等);替換延遲鏈,用倍頻、分頻或者同步計數器完成;替換異步脈沖產生單元(毛刺生成器),用同步時序設計脈沖電路;慎用鎖存器,鎖存器容易產生毛刺。

RTL代碼優化有哪些技巧

Pipelining,即流水線時序優化方法,其本質是調整一個較長的組合邏輯路徑中的寄存器位置,用寄存器合理分割該組合邏輯路徑,從而降低了對路徑的Clock-To-Output和Setup等時間參數的要求,達到提高設計頻率的目的。但是必須要注意的是,使用Pipelining優化技術只能合理地調整寄存器位置。

模塊復用與Resource Sharing,Sharing模塊復用和Resource Sharing是一種節約面積的思想,在設計電路中,在不影響性能的情況下,實現最少的邏輯資源開銷。

邏輯復制是一種通過增加面積而改善時序條件的優化手段。邏輯復制最常使用的場合是調整信號的扇出。如果某個信號需要驅動后級的很多單元,換句話說,也就是其扇出非常大,那么為了增加這個信號的驅動能力,必須插入很多級Buffer,這樣就在一定程度上增加了這個信號路徑的延時。這時可以復制生成這個信號的邏輯,使多路同頻同相的信號驅動后續電路,平均到每路的扇出變低,不需要加Buffer也能滿足驅動能力的要求,這樣就節約了該信號的路徑時延。

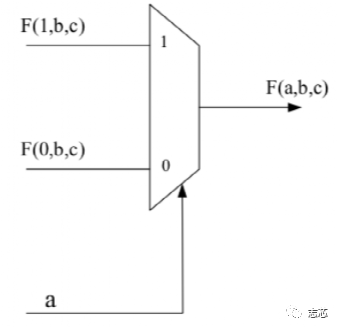

香農擴展(Shannon Expansion)也是一種邏輯復制、增加面積、提高頻率的時序優化手段。香農擴展通過邏輯復制、增加MUX(多路選擇器)來縮短某個優先級高但組合路徑長的信號的路徑延時(信號a),從而提高該關鍵路徑的工作頻率,以增加面積換取電路時序性能的優化。其擴展運算公式為:Fa,b,c=aF1,b,c+aF(0,b,c)。

END

審核編輯 :李倩

-

編碼

+關注

關注

6文章

1039瀏覽量

56992 -

RTL

+關注

關注

1文章

394瀏覽量

62676 -

同步電路

+關注

關注

1文章

61瀏覽量

13759

原文標題:RTL設計編碼原則

文章出處:【微信號:IC學習,微信公眾號:IC學習】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

請問誰有 RTL9210B RTL9210C 的sheet pdf 呀?

RTL8723DS天線引腳焊接問題

絕對值編碼器與增量式編碼器相比有哪些優勢?

高速PCB布局/布線的原則

知識點積累——什么是3W原則和20H原則?

優先編碼器:高效數據選擇與編碼的解決方案

英諾達推出RTL功耗優化工具

軸編碼器與無軸承編碼器,到底如何選擇?

伺服電機編碼器怎么選型

RTL設計編碼原則

RTL設計編碼原則

評論