前面幾篇文章講到了串行總線的預加重與均衡理論,概念性的東西比較多,大家如果不是從事信號完整性仿真等相關工作人員,理解起來會有一定的困難。很多關注高速先生公眾號的都是從事高速PCB 設計(Layout)的小伙伴,信號處理的理論可能對這些朋友日常工作幫助不是太大,這些朋友可能更多關注的是與布線相關的話題。

經常會有PCB設計的同事問我,板子上PCIe或者10G光口這類走線最長不能超過多少?速率不是那么高的信號,例如USB2.0,是不是就可以走很長的線了?速率到達多高,就要特別注意走線的損耗的問題?這些問題核心還是涉及到高速信號速率與傳輸線損耗之間的關系,如果我們對不同速率的信號通過傳輸線后的衰減有一個基本認識,就可以對布線長度做一個基本的評估了。

在回答這些問題之前,我們應該對不同頻率的信號經過一段長度的傳輸線后損耗程度有一定的了解。大家覺得傳輸速率為5Gbps的數字信號(不經過任何預加重或者均衡處理),經過一段15inch的傳輸線后(普通板材),眼圖還可以打開嗎,8G呢?為了解開大家的疑惑,我做了如下仿真,如下圖所示:

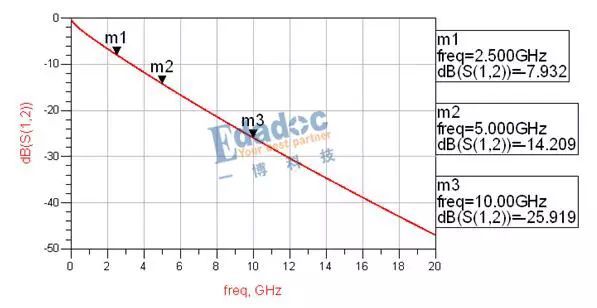

我們假設這個通信系統的驅動和接收器件都是理想模型,理想模型就意味著驅動和接收都是匹配較好,除了傳輸線的損耗之外,信號不受其他干擾項的影響。假設該傳輸線的介質為普通FR4,線寬為5mil,阻抗為50ohm,線長為15inch。首先我們來看下通道的插損曲線,如下圖:

通過插損曲線我們可以看出,通道的損耗還是很大的,在2.5G的時候就達到了-7.9dB,轉化成幅度,大概為0.4,也就是這個頻率下,信號的幅度損耗了60%。我們來看看不同速率的信號在穿過這個通道后會變成什么樣子。

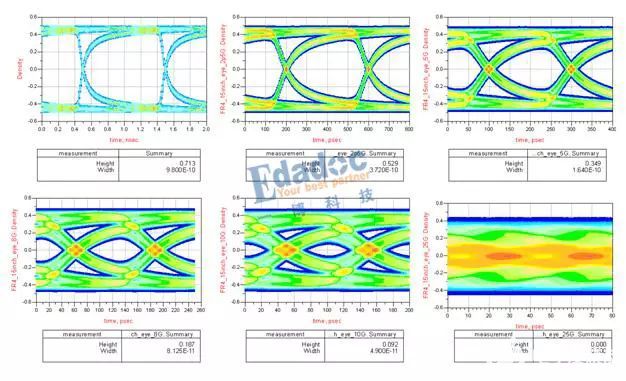

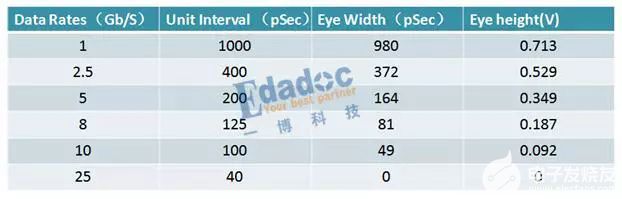

發送端為理想PRBS信號,發送端信號峰峰值為1V,上升和下降時間為10ps,我們分別仿真了速率為1G,2.5G,5G,8G,10G,25G的信號,通過15inch的傳輸線后,眼圖對比如下:

眼高和眼寬數據統計對比如下:

由上表我們可以看出,隨著信號頻率的提高,損耗的影響變得越來越大。至于這個影響到底有多大,我們可以參考上面的表格做一個大概的評估。

比較較真的網友可能又有疑惑了,你說了這么多,我只想知道我在布線的時候高速線到底最長可以走多長,你能不能給個準確的數值。遇到這些問題,高速先生也不能明確的給出答案。我只能說,it depends…..從傳輸通道來說,線長只是影響損耗的因素之一,還有很多關鍵的因素影響著通道的損耗,比如說我們選用的板材,換層孔的類型,數量,使用的銅箔類型,線寬線厚等等。對于高速串行信號來說,不同的芯片信號處理能力也不一樣,也就是所謂的預加重和均衡能力不一樣,既然芯片的性能有差異,我們對傳輸通道的評估也就不能一概而論了。最好的方法就是拿到芯片的模型進行仿真評估,綜合考慮這些因素對信號的影響,這也是SI工程師存在的價值。

審核編輯 :李倩

-

PCB設計

+關注

關注

396文章

4921瀏覽量

95267 -

PCIe

+關注

關注

16文章

1461瀏覽量

88419

發布評論請先 登錄

【解決方案】新能源園區投資,如何讓每一分錢都“心中有數”?

PCB設計與打樣的6大核心區別,看完少走3個月彎路!

從入門到精通:PCB設計必須遵守的5大核心原則

高速PCB板DDR5數據信號的長STUB要背鉆嗎?

光伏收益心中有數:安科瑞ADL雙向計量電表,準確記錄自發用電與上網電量

PCB設計:直觀信號眼圖,衰減心中有數

PCB設計:直觀信號眼圖,衰減心中有數

評論