RTL頂層自動連線聽說過嗎?想學嗎?我們今天就來介紹自動連線的神器——emacs verilog-mode。

emacs是什么?

江湖流傳版:傳說中神的編輯器。

維基百科版:Emacs(Editor MACroS,宏編輯器),最初由Richard Stallman于1975年在MIT協同Guy Lewis Steele Jr.共同完成。

verilog-mode是什么

官網的介紹:

Verilog-mode.el is the extremely popular free Verilog mode for Emacs which provides context-sensitive highlighting, auto indenting, and provides macro expansion capabilities to greatly reduce Verilog coding time. It supports AUTOs and indentation in Emacs for traditional Verilog (1394-2005), the Open Verification Methodology (OVM) and SystemVerilog (1800-2005/1800-2009).

Recent versions allow you to insert AUTOS in non-AUTO designs, so IP interconnect can be easily modified. You can also expand SystemVerilog ".*" port instantiations, to see what ports will be connected by the simulators.

簡單點說就是支持Verilog、SystemVerilog(包括UVM)的emacs語法高亮文件。其中提到Verilog-mode支持Autos——這就是今天的重點。

Verilog-mode是由Michael McNamara mac@verilog.com和Wilson Snyder wsnyder@wsnyder.org編寫。難能可貴的是,這個verilog-mode保持著每月都有更新。

值得一提的是Wilson Snyder就是SystemVerilog開源仿真器Verilator的作者。

verilog-mode Autos有哪些功能

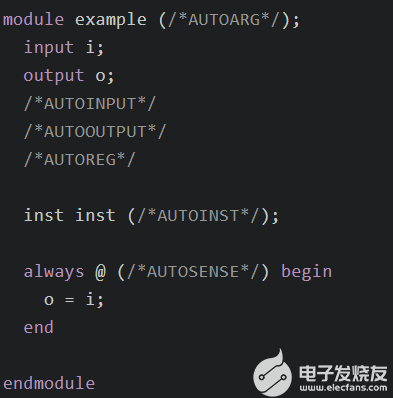

手動編寫的verilog代碼:

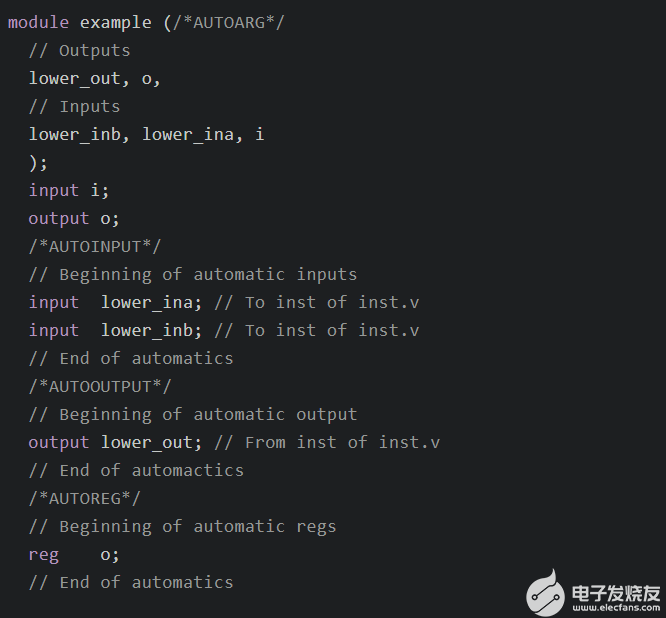

由Autos處理后的Verilog代碼:

大家可以看到,verilog-mode自動分析出:

· 模塊的端口輸入和輸出

· 內部變量

· 敏感信號列表

· 提取子模塊的端口定義

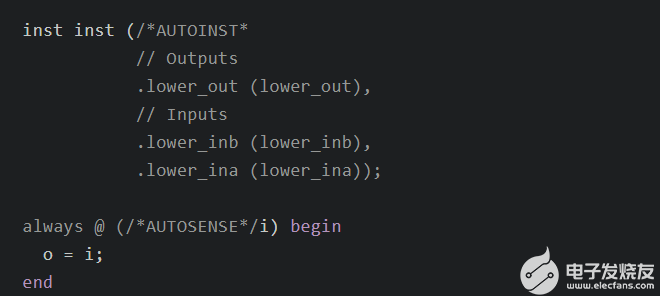

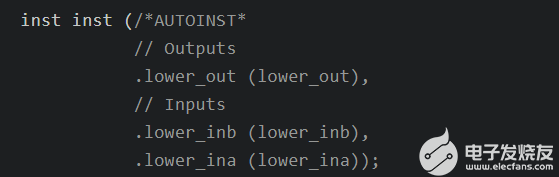

自動提取子模塊的端口定義來連線是今天的重點中的重點。一般來講,我們實例化模塊時大部分的信號名與子模塊定義的名字一致即可。如上面代碼中的:

特殊連接關系的處理

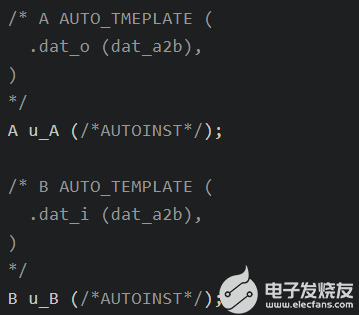

但常常我們頂層連接時會換一個名字。比如module A有一個輸出端口dat_o,module B有一個輸入端口dat_i,這兩者怎么連?定義模版AUTO_TEMPLATE,如下:

手動編寫的verilog:

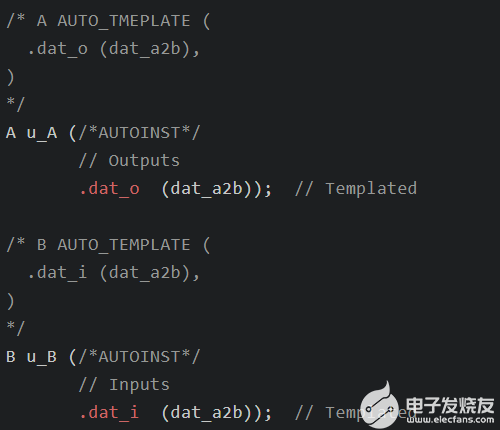

由Autos處理后的verilog代碼:

在哪里找子模塊定義?

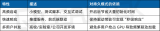

默認規則:

· 當前文件夾下找

· 當前找不到怎么辦,指定搜索路徑(與verilog仿真器的參數-y一樣)

使用方法:在頂層endmodule后面指定verilog-library-directories,如下:

除了寫模版還需要做什么?

只需要Ctrl-C Ctrl-A,僅此而已。

如果修改了子模塊或者模版,再按一次Ctrl-C Ctrl-A。

更多功能

verilog-auto-arg for AUTOARG module instantiations

verilog-auto-ascii-enum for AUTOASCIIENUM enumeration decoding

verilog-auto-assign-modport for AUTOASSIGNMODPORT assignment to/from modport

verilog-auto-inout for AUTOINOUT making hierarchy inouts

verilog-auto-inout-comp for AUTOINOUTCOMP copy complemented i/o

verilog-auto-inout-in for AUTOINOUTIN inputs for all i/o

verilog-auto-inout-modport for AUTOINOUTMODPORT i/o from an interface modport

verilog-auto-inout-module for AUTOINOUTMODULE copying i/o from elsewhere

verilog-auto-inout-param for AUTOINOUTPARAM copying params from elsewhere

verilog-auto-input for AUTOINPUT making hierarchy inputs

verilog-auto-insert-lisp for AUTOINSERTLISP insert code from lisp function

verilog-auto-insert-last for AUTOINSERTLAST insert code from lisp function

verilog-auto-inst for AUTOINST instantiation pins

verilog-auto-star for AUTOINST .* SystemVerilog pins

verilog-auto-inst-param for AUTOINSTPARAM instantiation params

verilog-auto-logic for AUTOLOGIC declaring logic signals

verilog-auto-output for AUTOOUTPUT making hierarchy outputs

verilog-auto-output-every for AUTOOUTPUTEVERY making all outputs

verilog-auto-reg for AUTOREG registers

verilog-auto-reg-input for AUTOREGINPUT instantiation registers

verilog-auto-reset for AUTORESET flop resets

verilog-auto-sense for AUTOSENSE or AS always sensitivity lists

verilog-auto-tieoff for AUTOTIEOFF output tieoffs

verilog-auto-undef for AUTOUNDEF =`undef of local =`defines

verilog-auto-unused for AUTOUNUSED unused inputs/inouts

verilog-auto-wire for AUTOWIRE instantiation wires

verilog-read-defines for reading =`define values

verilog-read-includes for reading =`includes

verilog-mode下載、安裝

新版的GNU Emacs自帶verilog-mode,如果需要最新的verilog-mode可以在官網下載

VIM用戶咋辦?

可以用VIM調動shell命令執行(emacs批處理模式),例如:

:!emacs --batch <filenames.v> -f verilog-batch-auto

是不是很簡單!

審核編輯 :李倩

-

Verilog

+關注

關注

30文章

1371瀏覽量

114217 -

代碼

+關注

關注

30文章

4947瀏覽量

73291 -

編輯器

+關注

關注

1文章

826瀏覽量

32699

發布評論請先 登錄

請問測試用例.verilog文件是怎么生成的呢?

使用NucleiStudio生成tb仿真需要的.verilog文件

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

verilog模塊的調用、任務和函數

PIN_MODE_0工作模式是什么

FPGA Verilog HDL語法之編譯預處理

Nexperia擴展E-mode GaN FET產品組合

一文詳解Verilog HDL

尋找verilog高手,有報酬

DLP6500FYE如何使用video mode?

Verilog中signed和$signed()的用法

淺談Verilog和VHDL的區別

Emacs的verilog-mode介紹

Emacs的verilog-mode介紹

評論