FPGA中有專門的ROM IP Core,如果按照規范用Verilog編寫的ROM文件可以被工具綜合成RAM資源,而ASIC在需要后端去做專門Memory,前端仿真可以自己編寫RAM/ROM/FIFO/RegFile IP。為了方便仿真這樣寫個ROM,方便初始化。

?

?

?

?

?將設計電路參數化可重復使用,構建自己的代碼庫,搭建起你的數字積木。

?

?

?

?

?將設計電路參數化可重復使用,構建自己的代碼庫,搭建起你的數字積木。

module single_port_rom(/*autoarg*/

Outputs

q,

Inputs

clk

);

parameter DATA_WIDTH = 8;

parameter ADDR_WIDTH = 8;

input [ADDR_WIDTH-1:0] addr;

input clk;

output reg [DATA_WIDTH-1:0] q;

reg [DATA_WIDTH-1:0] rom[2**ADDR_WIDTH-1:0];

initial begins

rom);

rom);

end

always @ (posedge clk)begin

q <= rom[addr];

end

endmodule

系統函數$readmemh和$readmemb分別用來讀取十六進制文件和二進制文件。貌似沒有讀十進制的。txt中的數據每行一個不需要逗號和最后一個數據后面的分號,數據格式對應。更多使用可以查詢IEEE的Verilog語法手冊。例化方式和rom IP一樣可參數化配置任意大小

single_port_rom

#(

.DATA_WIDTH(DATA_WIDTH),

.ADDR_WIDTH(ADDR_WIDTH)

)

u_sin(/*autoinst*/

// Outputs

.q (dout[DATA_WIDTH-1:0]),

// Inputs

.addr (addra[ADDR_WIDTH-1:0]),

.clk (clk));

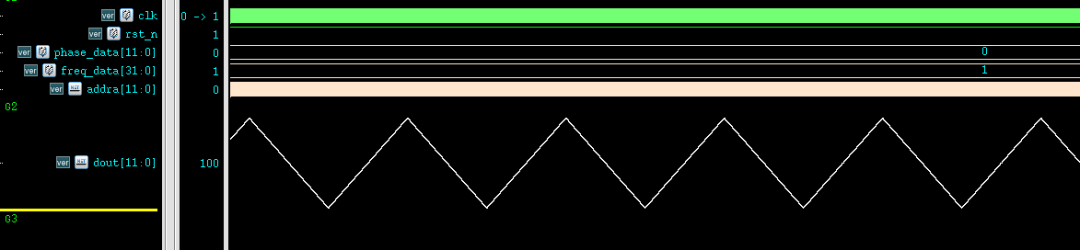

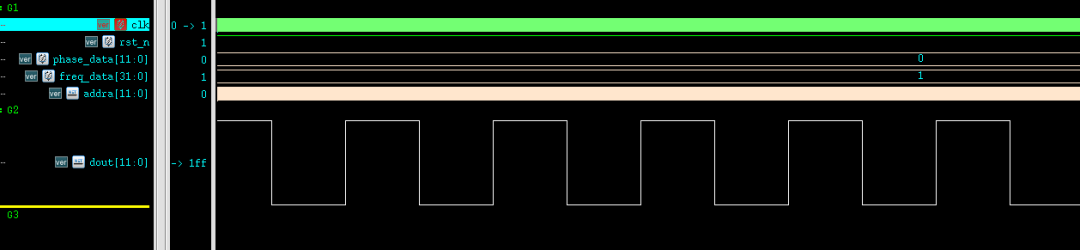

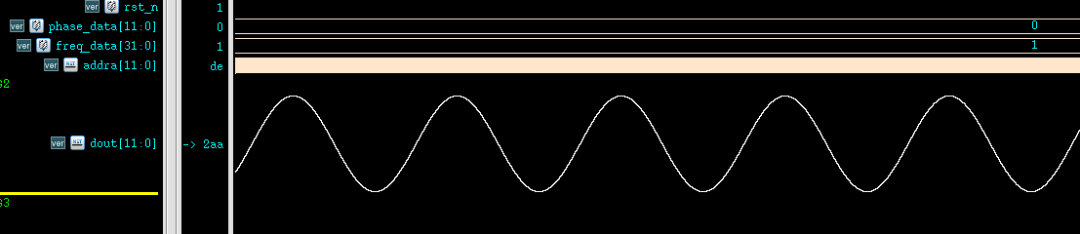

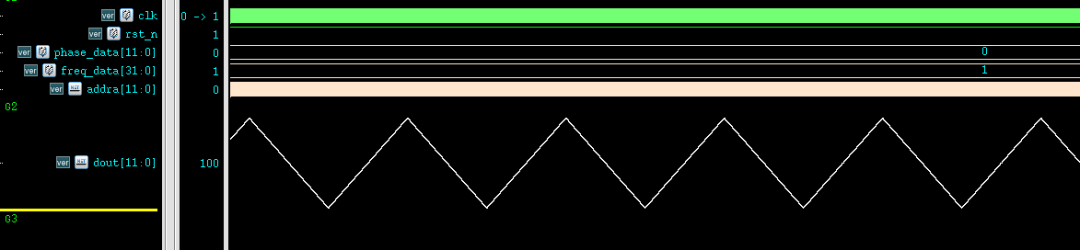

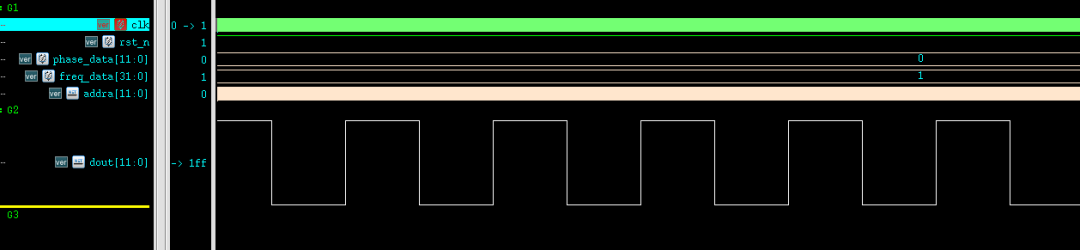

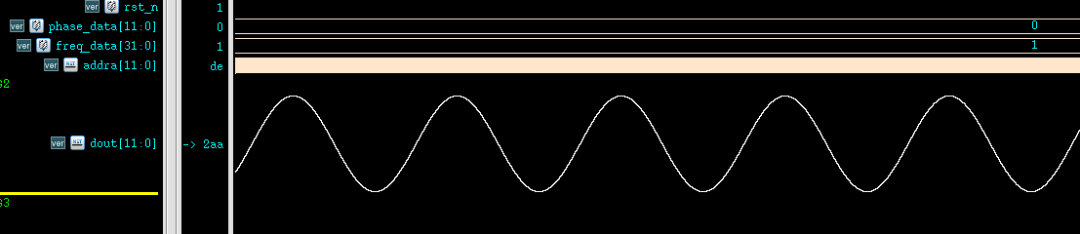

整了三個波形,仿真能跑起來。

?

?

?

?

?將設計電路參數化可重復使用,構建自己的代碼庫,搭建起你的數字積木。

?

?

?

?

?將設計電路參數化可重復使用,構建自己的代碼庫,搭建起你的數字積木。

審核編輯 :李倩

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

asic

+關注

關注

34文章

1271瀏覽量

124116 -

ROM

+關注

關注

4文章

579瀏覽量

88599 -

Verilog

+關注

關注

30文章

1371瀏覽量

114217

原文標題:為了方便仿真這樣寫個ROM

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

RISCV指令二進制編碼利用matlab生成E203仿真可用文件

鑒于nuclei studio IDE生成的.verilog難懂,為了方便對單條或者幾條指令進行測試,我們隊伍編寫了matlab代碼來實現E203仿真可以識別到的文件。

matlab代碼如下

發表于 10-22 07:06

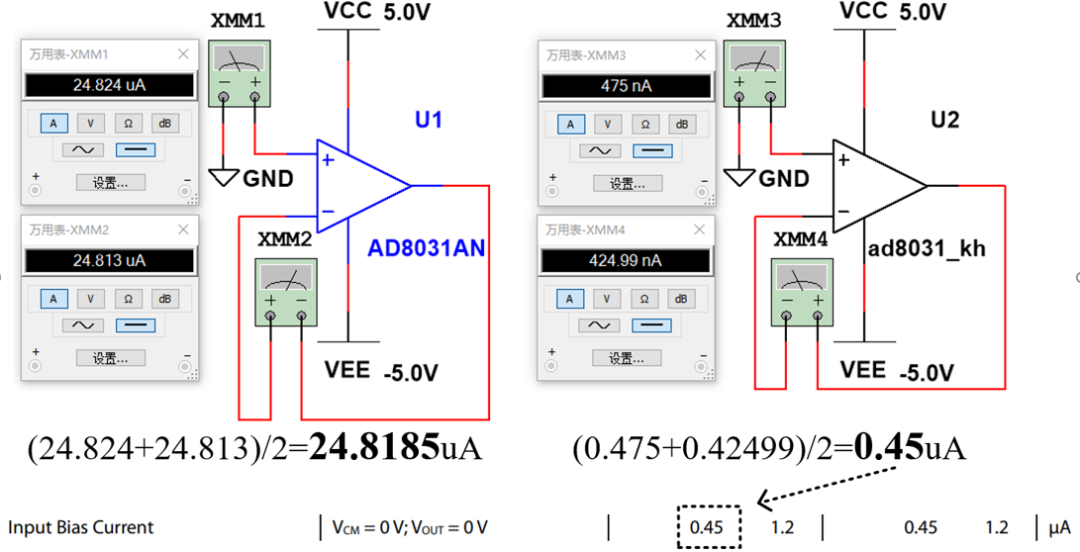

胡言亂語:Multisim仿真準不準?偏置電流錯的離譜?

這是很多同學都會問到的一個問題,Multisim仿真究竟準不準?很多同學在仿真時發現Multisim仿真結果和手冊的差距太大,然后說是Multisim這個軟件不行,其實不是這樣的,不管

Simcenter FLOEFD BCI-ROM和Package Creator模塊

優勢采用獨立于邊界條件的降階模型(BCI-ROM)加速執行瞬態熱仿真,同時采用PackageCreator輕松創建電子封裝熱模型。求解速度比完整的3D詳細模型快40,000倍,且不折損精度有效保持

Simcenter Flotherm BCI-ROM技術:與邊界條件無關的降階模型可加速電子熱設計

BCI-ROM可生成為矩陣類型、用于電路仿真的電熱模型(VHDL-AMS格式)、用于系統仿真(FMU格式)的模型,甚至用于3DCFD的嵌入式BCI-ROM從根據熱瞬態測試數

為了方便仿真這樣寫個ROM

為了方便仿真這樣寫個ROM

評論