Mini Circuits的RKK-4-252+倍頻器提供4倍的倍頻系數,將430至630 MHz的輸入頻率轉換為1720至2520 MHz的輸出頻率,支持應用包括合成器、本地振蕩器、衛星上下轉換器等。此模型提供輸入功率范圍為+16至+19 dBm、低轉換損耗和良好的諧波抑制。這個倍增器封裝在微型屏蔽表面安裝封裝(0.50 x 0.50 x 0.18“)中,帶有環繞式終端,具有優異的可焊性。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

原文標題:RKK-4-252+4X SMT乘法器,輸出頻率1720-2520 MHz

文章出處:【微信號:兆億微波,微信公眾號:兆億微波】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

CDCVF25084:高性能時鐘乘法器的深度剖析

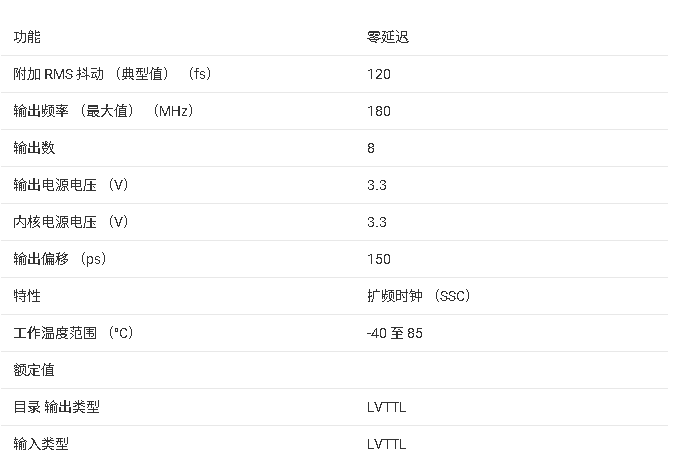

)的CDCVF25084——一款3.3 - V 1:8零延遲(PLL)x4時鐘乘法器。 文件下載: cdcvf25084.pdf 1. 產品概述 CDCVF25084是一款高性能、低偏斜、低抖動的鎖相環

低成本模擬乘法器AD633:特性、應用與設計指南

到各種應用場景,為大家呈現一個全面的設計指南。 文件下載: AD633.pdf 一、AD633 概述 AD633是一款功能完備的四象限模擬乘法器,它集成了高阻抗差分X和Y輸入,以及高阻抗求和輸入(Z)。其低阻抗輸出電壓由一個埋入

AD532:高性能單芯片乘法器/除法器的卓越之選

AD532:高性能單芯片乘法器/除法器的卓越之選 在電子設計領域,乘法器和除法器是實現復雜運算和信號處理的關鍵組件。而AD532作為一款預微調的單芯片

E203V2長周期乘法器核心booth算法解讀

低位部分和從第一次開始便從32位寄存器高位開始右移兩位,以此類推,進行16次加法運算后,高位部分和已經算出來了,而低位部分和剛好右移到寄存器的最低位,最后還需一個時鐘周期輸出乘法器的運算結果。

同時

發表于 10-24 09:33

改進wallance樹乘法器優化方法

首先,根據之前分享的乘法器的優缺點,我們針對17周期的乘法器進行優化,為乘法設計的專用數據通路,為了保持e203的低功耗、低面積的優點、我們仍采用基4booth算法進行部分積生成,而對

發表于 10-23 06:37

關于E203內核高性能乘法器優化(一)

多個CSA并行地對部分積求和,其中較為經典的結構就是Wallace樹形乘法器

下圖給出了比較經典的華萊士樹的結構:

以一級CSA壓縮為延時單位,對9個部分積進行壓縮需要4級CSA壓縮,共4個延時單位

發表于 10-23 06:09

蜂鳥乘法器設計分享

蜂鳥的乘法器主體設計在ALU模塊的子單元MDV模塊中,MDV模塊包括乘除法器邏輯設計,它只包含運算控制,但并不包含具體運算,它們都需要將部分積或者部分余數傳入數據通路(dpath模塊)中,從而實現

發表于 10-22 08:21

基4-Booth單周期乘法器的具體設計

的同時,門電路延遲也完全滿足要求。甚至在本隊嘗試將頻率提升至32MHz(原E203的2倍)時,該乘法器,包括后文將提到的改進后的除法器依然可以完美地工作。

發表于 10-22 08:07

蜂鳥E203乘法器改進

連續不斷的輸出,不會像循環移位那樣,需計算完才輸出,中間沒有等待時間。流水線乘法器

大大提高了計算效率,但是占用資源也隨即增加。因此將此乘法器用在蜂鳥E203,亦能提高數據計算效率。

發表于 10-22 07:28

蜂鳥E203內核乘法器的優化

乘法器的優化實現一般從兩個方面入手。第一是減少生成的部分積數量,另外就是減少部分積累加的延時。

在開源的E203源碼中,32*32乘法器是利用radix-4 booth編碼產生部分積,每個周期做一次

發表于 10-22 06:11

優化boot4的乘法運算周期

可以在不同的時鐘周期內完成,從而并行化運算流程,提高乘法器的運算性能。

采用多級壓縮:在Boot4乘法器中,使用了基于連乘算法的多級壓縮技術。可以通過增加多級壓縮,進一步降低管理乘法器

發表于 10-21 13:17

優化boot4乘法器方法

優化電路設計:在電路設計中,可以采用更快速的邏輯單元和存儲器元件,優化關鍵路徑和信號傳輸路線,從而降低延遲,縮短乘法器的運算周期。

固定位寬:Boot4乘法器可以處理不同位寬的數據,但是處理不同位寬

發表于 10-21 12:13

?CDCVF25084 3.3V 1:8零延遲(PLL)x4時鐘乘法器技術文檔總結?

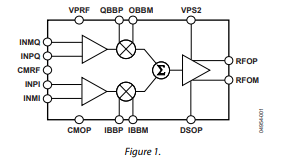

該CDCVF25084是一款高性能、低偏斜、低抖動、鎖相環時鐘乘法器。它使用 PLL 在頻率和相位上將輸出時鐘精確對齊輸入時鐘信號,包括 4 的乘法

ADL5390 RF矢量乘法器技術手冊

ADL5390矢量乘法器由一對匹配的寬帶可變增益放大器組成,二者輸出相加,每個放大器具有單獨的線性幅度增益控制。如果兩個輸入RF信號正交,則可以將該矢量乘法器配置為矢量調制器,或將增益控制引腳用作

RKK-4-252+4X SMT乘法器,輸出頻率1720-2520 MHz

RKK-4-252+4X SMT乘法器,輸出頻率1720-2520 MHz

評論