本文是一篇詳細介紹ISSCC2020會議上一篇有關亞穩(wěn)態(tài)解決方案的文章,該技術也使得FPGA在較高頻率下的時序收斂成為了可能。亞穩(wěn)態(tài)問題是芯片設計和FPGA設計中常見的問題,隨著FPGA的發(fā)展,時序問題已經(jīng)成為一個越來越難的挑戰(zhàn)。單bit線網(wǎng)和邏輯通路扇出在巨大的芯片上擴散,而布線資源有限,這使得傳統(tǒng)的時序收斂成為一場噩夢。

在同步設計上實現(xiàn)時序收斂的傳統(tǒng)技術一個接一個地碰壁,未能實現(xiàn)規(guī)模化。Xilinx和Achronix在其新一代FPGA中解決了這一問題,在傳統(tǒng)的邏輯和布線結構的基礎上增加了片上網(wǎng)絡(NoC)。NoC本質(zhì)上改變了游戲規(guī)則,因為整個芯片不再需要在一個巨大的神奇匯流中實現(xiàn)時序收斂。現(xiàn)在,更小的同步塊可以通過NoC傳遞數(shù)據(jù),減輕了傳統(tǒng)布線結構的負擔,并將原來巨大的設計自動化工具問題分解成更小的、可管理的塊。

在進行NoC布線的兩家供應商中,Xilinx和Achronix中,Achronix聲稱通過其二維跨芯片AXI實現(xiàn)了最快的NoC。NoC中的每一行或每一列都實現(xiàn)為兩個工作在2 Ghz的256位單向AXI通道,同時在每個方向上提供512 Gbps數(shù)據(jù)流量。Speedster的NoC總共有197個端點,產(chǎn)生27 Tbps的聚合帶寬,比FPGA的傳統(tǒng)按位布線資源少了很多。

本文從一篇芯片設計頂會(ISSCC2020)文章中設計的一款解決低電壓亞穩(wěn)態(tài)問題的同步器作為著眼點,試圖還原NoC架構引入FPGA芯片后對FPGA的時序收斂起到積極作用的全過程。報告視頻非常精彩,深入淺出,環(huán)環(huán)相扣,娓娓道來。歡迎大家留言討論。

昨天剛結束的ICAC2020線上會議,高峰期在線人數(shù)高達1.6萬人,筆者有幸抽空聽了半個下午,其中完整的聽完了本文中所提到的亞穩(wěn)態(tài)相關的一個會議。該報告是由上海交通大學的何衛(wèi)鋒博士做的,有關ICAC2020的詳細信息請搜索微信“ICAC Workshop”詳細了解。

報告相關文章的信息:

Chuxiong Lin, Weifeng He, Yanan Sun, Zhigang Mao, Bingxi Pei, Mingoo Seok, “A Near-Threshold-Voltage Network-on-Chip with a Metastability Error Detection and Correction Technique for Supporting a Quad-Voltage/Frequency-Domain Ultra-Low-Power System-on-a-Chip,” IEEE International Solid-State Circuits Conference (ISSCC), 2020.

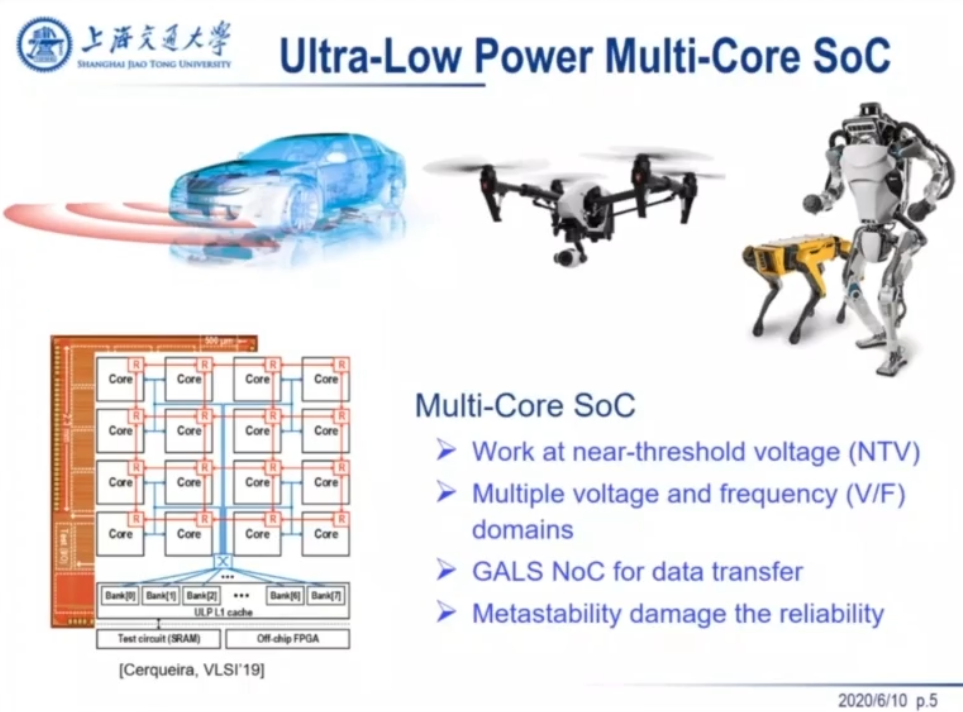

隨著物聯(lián)網(wǎng)、機器人、無人機、可穿戴/植入設備等低功耗便攜式設備越來越普及,超低功耗SoC芯片技術也面臨著越來越大的挑戰(zhàn)。為了降低這些SoC芯片的功耗,人們提出了如上圖所示的各種技術。其中,近閾值低電壓技術就是其中最受關注的一種。在超低電壓下,可以很大程度的降低芯片的功耗,但隨之帶來了可靠性降低的代價。在上述SoC芯片中,往往具有多個電壓頻率域。由于超低電壓下工藝等因素帶來的任意兩個時鐘之間相位關系的不確定性,導致芯片在正常工作狀態(tài)下經(jīng)常會出現(xiàn)亞穩(wěn)態(tài)問題。

什么是亞穩(wěn)態(tài)?

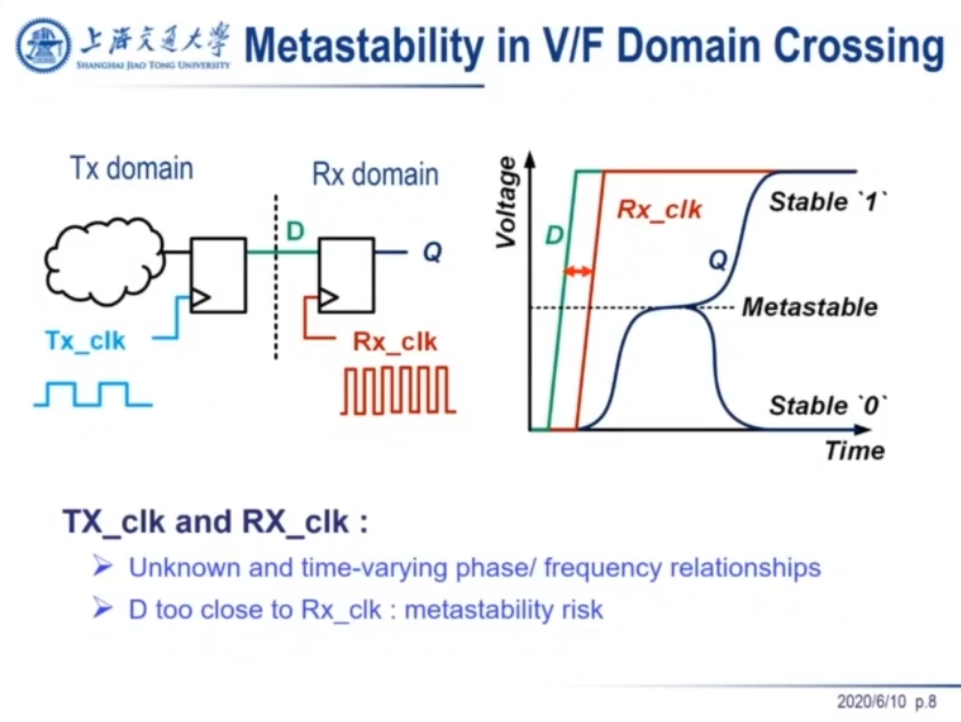

當一個信號從Tx時鐘域傳遞到Rx時鐘域時,因為Tx_clk和Rx_clk時鐘信號相位的不確定性,就有可能會造成數(shù)據(jù)信號D的上升沿會落在Rx_clk時鐘上升沿的變化范圍內(nèi),如果D信號的翻轉(zhuǎn)(上升沿或下降沿)和Rx_clk的上升沿(采樣沿)靠的足夠近的時候,就會造成了采樣出來的信號Q會出現(xiàn)非0非1的中間狀態(tài),如果信號Q這種非0非1的狀態(tài)持續(xù)時間超過了Rx_clk的時鐘周期,我們就稱Q信號的這種非0非1的狀態(tài)是亞穩(wěn)態(tài)。

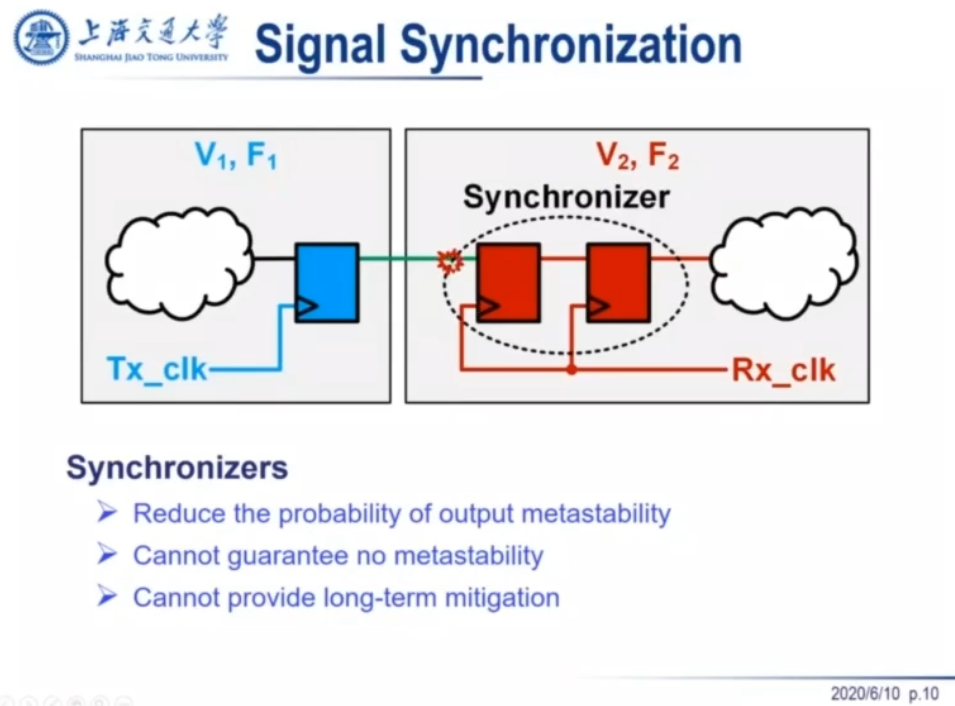

傳統(tǒng)解決亞穩(wěn)態(tài)的方法是采用上圖中“打兩拍”同步器的方法。這種方法可以有效的降低出現(xiàn)亞穩(wěn)態(tài)的幾率,但不能完全避免出現(xiàn)亞穩(wěn)態(tài)的情況。隨著電壓的降低,亞穩(wěn)態(tài)出現(xiàn)的幾率越來越大。而傳統(tǒng)的同步器無法解決上圖中同步器的輸入端出現(xiàn)亞穩(wěn)態(tài)的情況,因此文章就提出了一種能夠解決同步器輸入端出現(xiàn)亞穩(wěn)態(tài)情況的方案。

芯片中跨時鐘域信號的解決方法就是加同步器,一個同步器不行,那就再加一個。

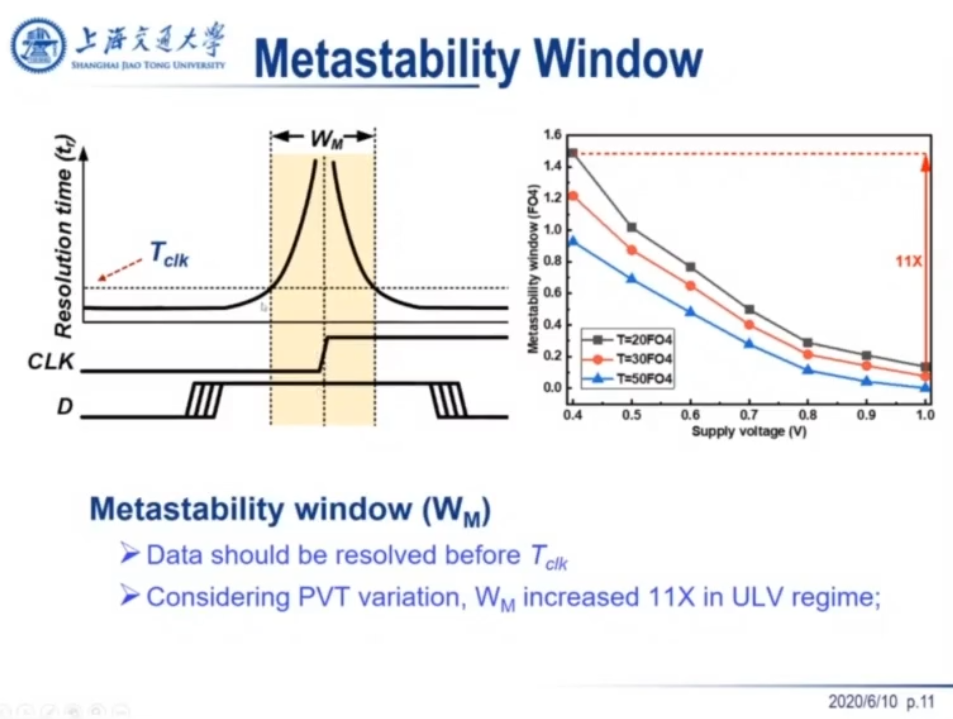

亞穩(wěn)態(tài)窗口

以接收時鐘沿為基準,以接收端時鐘Tclk的頻率作為將數(shù)據(jù)從亞穩(wěn)態(tài)到穩(wěn)定狀態(tài)的一個分辨時間。當數(shù)據(jù)D的翻轉(zhuǎn)在上圖中黃色的亞穩(wěn)態(tài)的窗口之內(nèi)時,意味著同步器是無法在一個時鐘周期內(nèi)將D信號從亞穩(wěn)態(tài)恢復為穩(wěn)定狀態(tài)。而對應的黃色區(qū)域的這個窗口,就稱為是亞穩(wěn)態(tài)窗口。

作者采用蒙特卡洛仿真了一下在65nm工藝下,電壓從1.5V降低到0.4V的過程中,亞穩(wěn)態(tài)問題出現(xiàn)的幾率增大了11倍。

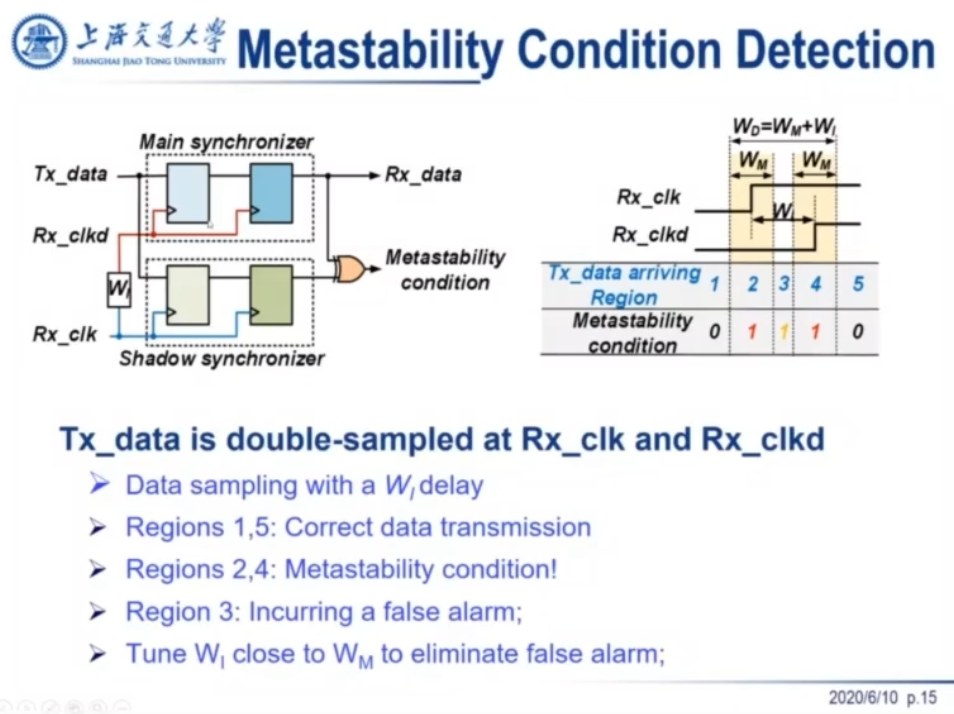

作者提出了上圖中雙采樣的比較電路,可通過調(diào)整Rx_clk和Rx_clkd中間的相位差Wi,分成了五種情況來說明是否出現(xiàn)了亞穩(wěn)態(tài)的情況。進而對如何控制亞穩(wěn)態(tài)的出現(xiàn)進行評估和分析。

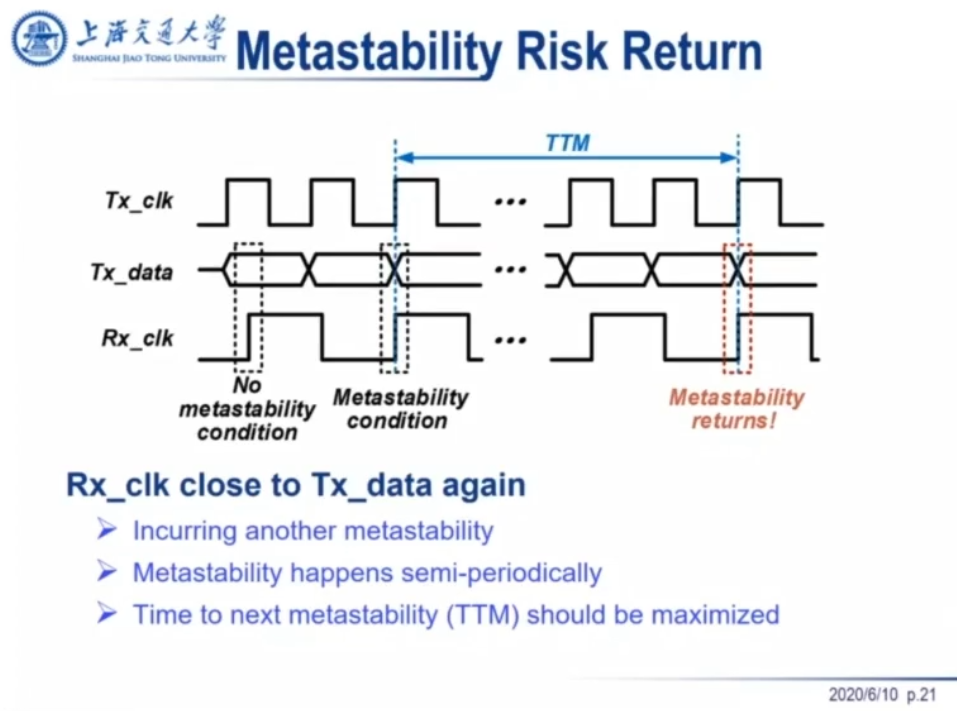

如果出現(xiàn)了亞穩(wěn)態(tài),可以要求發(fā)送端再重傳一次信號,但無法從根本上解決亞穩(wěn)態(tài)問題,亞穩(wěn)態(tài)問題還是會過一段時間后再次出現(xiàn)。為了從根本上解決出現(xiàn)亞穩(wěn)態(tài)的問題,定義了下圖中兩次亞穩(wěn)態(tài)出現(xiàn)的時間間隔TTM。降低電路中出現(xiàn)亞穩(wěn)態(tài)出現(xiàn)的概率,就相當于是增大TTM的值。

為了增大TTM的值,可以考慮采樣時鐘上升沿與被采樣數(shù)據(jù)翻轉(zhuǎn)沿的相位偏差,根據(jù)這個偏差可以將電路出現(xiàn)亞穩(wěn)態(tài)的概率分類為Class-A和Class-B,還得到一個這兩種狀態(tài)下相位偏差的閾值。這樣整個問題就轉(zhuǎn)換為想辦法當相位偏差處在Class-B的時候,想辦法將其相位偏差轉(zhuǎn)換到Class-A狀態(tài)。

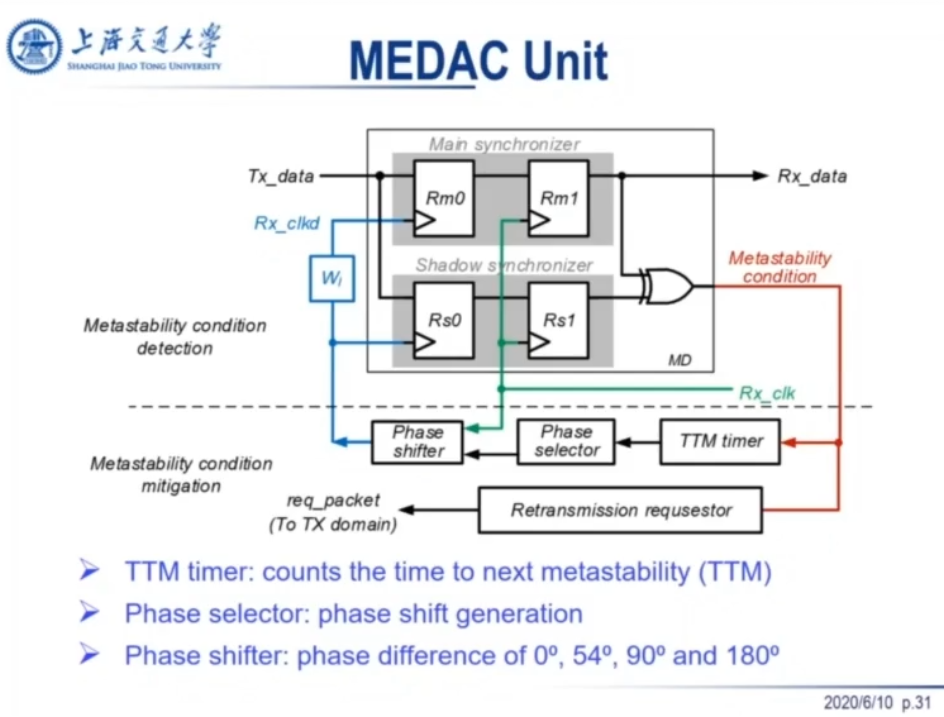

因此,解決辦法就是在同步器電路中添加移相器。始終保證采樣時鐘上升沿與被采樣數(shù)據(jù)翻轉(zhuǎn)沿的相位偏差處在Class-A的狀態(tài)。作者設計了一個叫MEDAC的同步器單元,可以自動檢測到是否即將出現(xiàn)亞穩(wěn)態(tài)并實時對相位偏差進行調(diào)整。

工作原理如下:當電路通過計數(shù)器TTM Timer發(fā)現(xiàn)該計數(shù)器的值小于了上圖中的TTM閾值時,Phase selector模塊就會驅(qū)動Phase shifter去調(diào)整Rx_clkd信號與Tx_data之間的相位偏差,使其相移偏差從Class-B狀態(tài)轉(zhuǎn)換到Class-A狀態(tài)。從而降低了電路出現(xiàn)亞穩(wěn)態(tài)的風險。

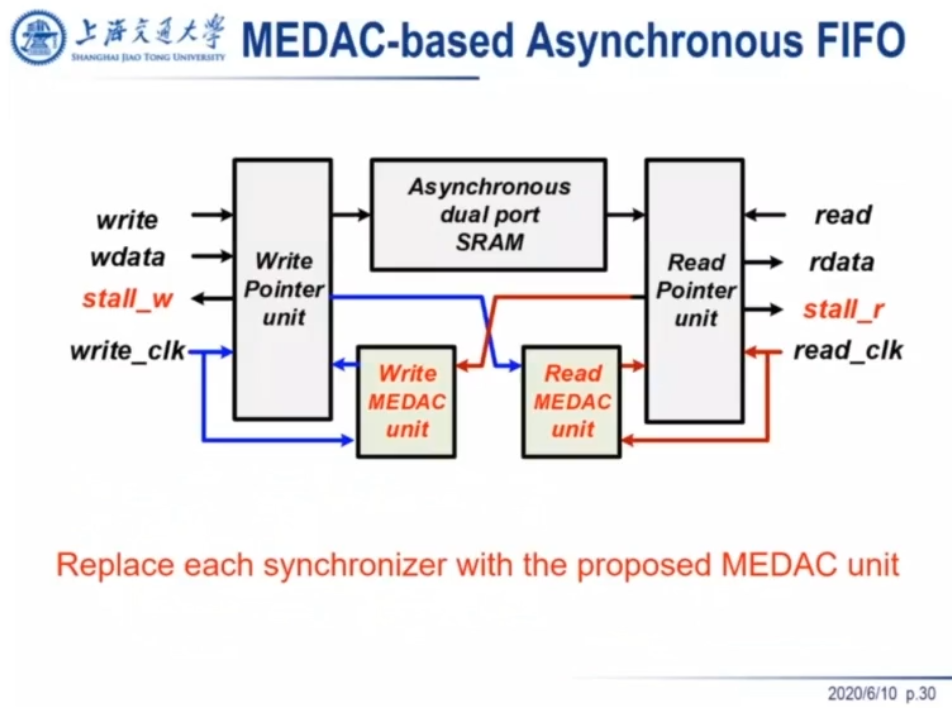

把MEDAC同步器單元應用于異步FIFO中。

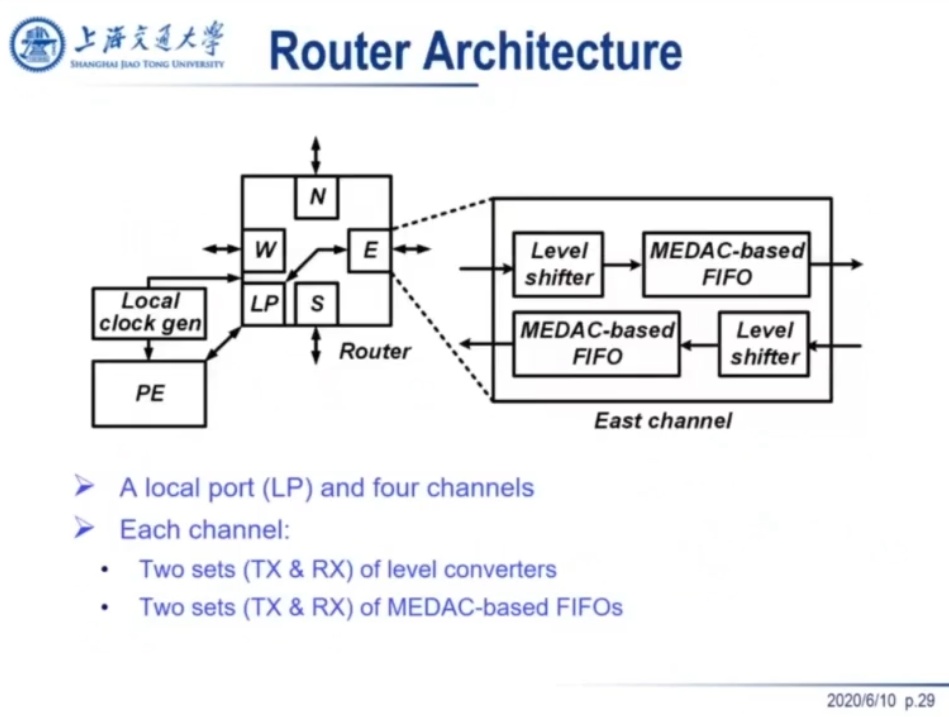

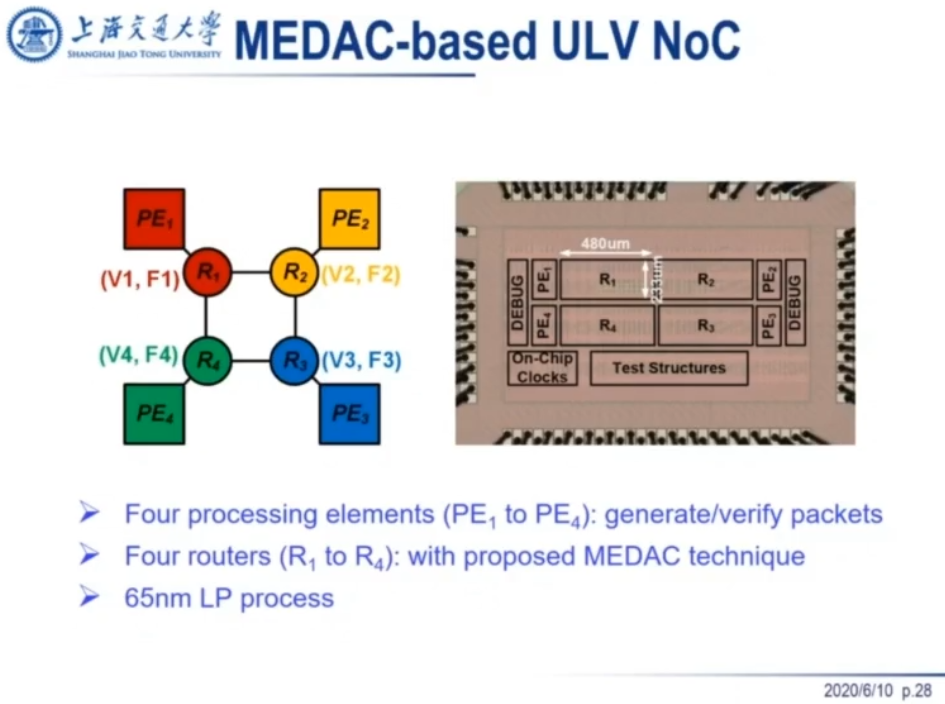

再把該異步FIFO應用于一款四個Router的NOC芯片中。

NoC芯片的結構和芯片圖如下:

在測試了4G個數(shù)據(jù)包后,得到了很好的測試結果。在1V電壓下,亞穩(wěn)態(tài)出現(xiàn)的概率下降了幾十倍,在0.4V電壓下,亞穩(wěn)態(tài)出現(xiàn)的概率下降幾千倍。很好的解決了亞穩(wěn)態(tài)問題。

審核編輯 :李倩

-

物聯(lián)網(wǎng)

+關注

關注

2945文章

47820瀏覽量

414994 -

SoC芯片

+關注

關注

2文章

669瀏覽量

37165

原文標題:帶有同步器的NoC結構是解決FPGA高速時序收斂的關鍵原因嗎?

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

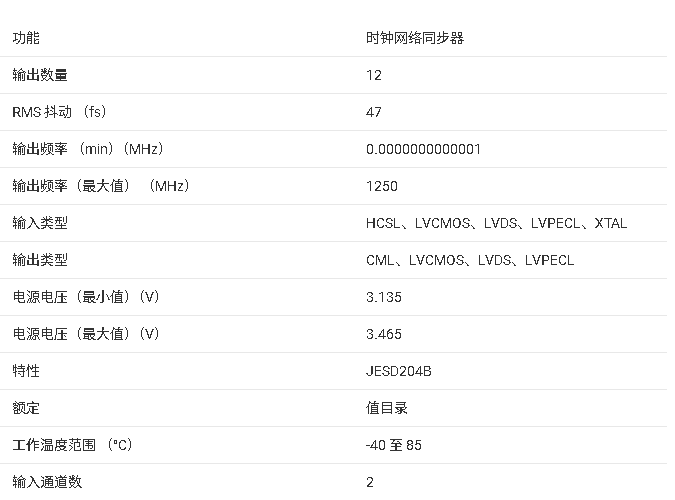

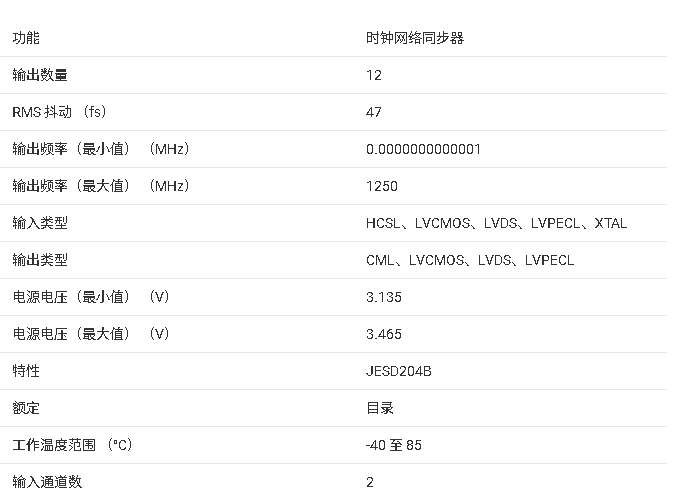

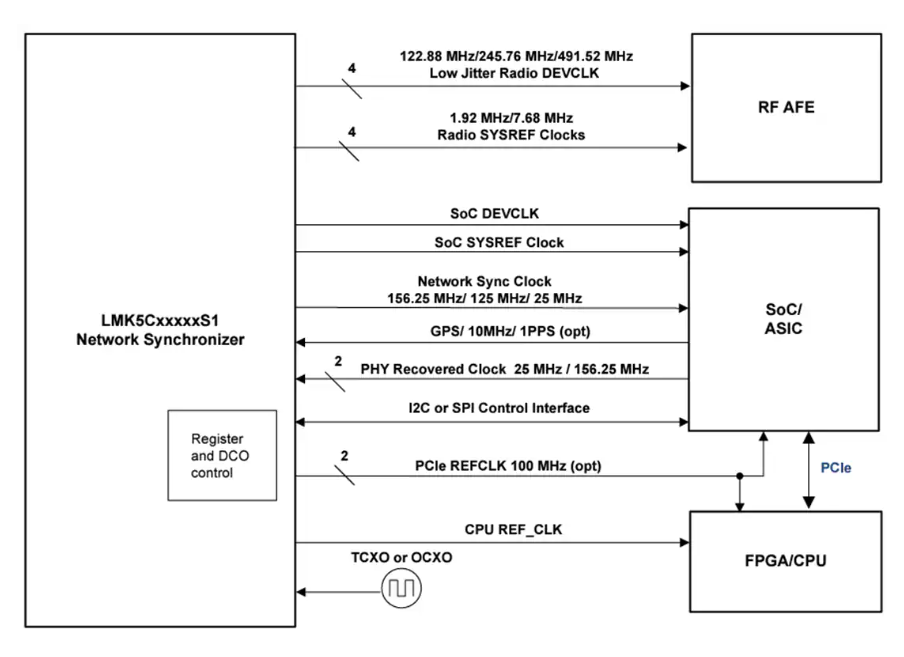

CDCM7005:高性能時鐘同步器與抖動清理器的深度解析

高性能時鐘同步器CDCE72010的全方位解析

深入解析LMK05318:高性能網(wǎng)絡同步器的強大功能與應用實踐

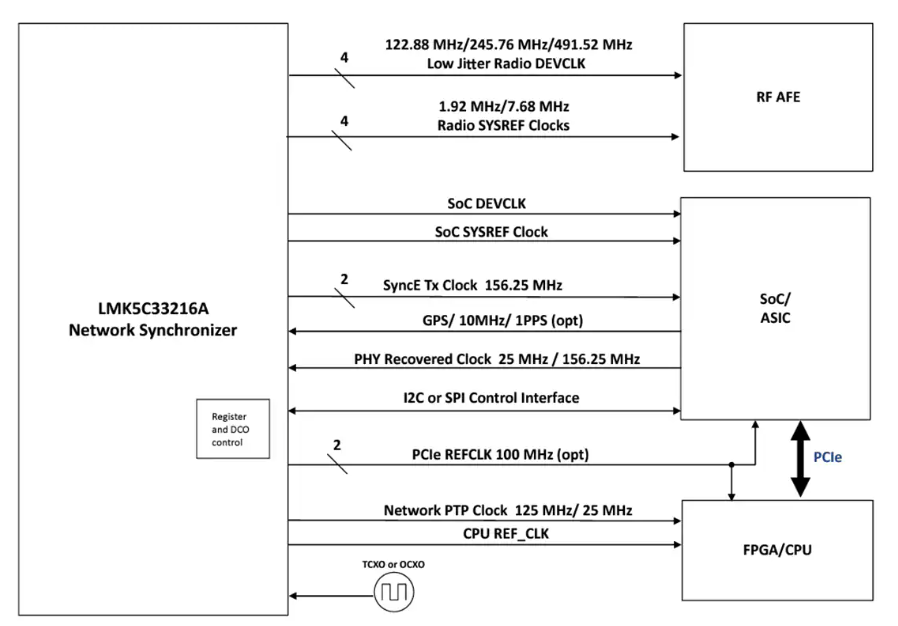

LMK5C33216:無線通信領域的高性能時鐘同步器

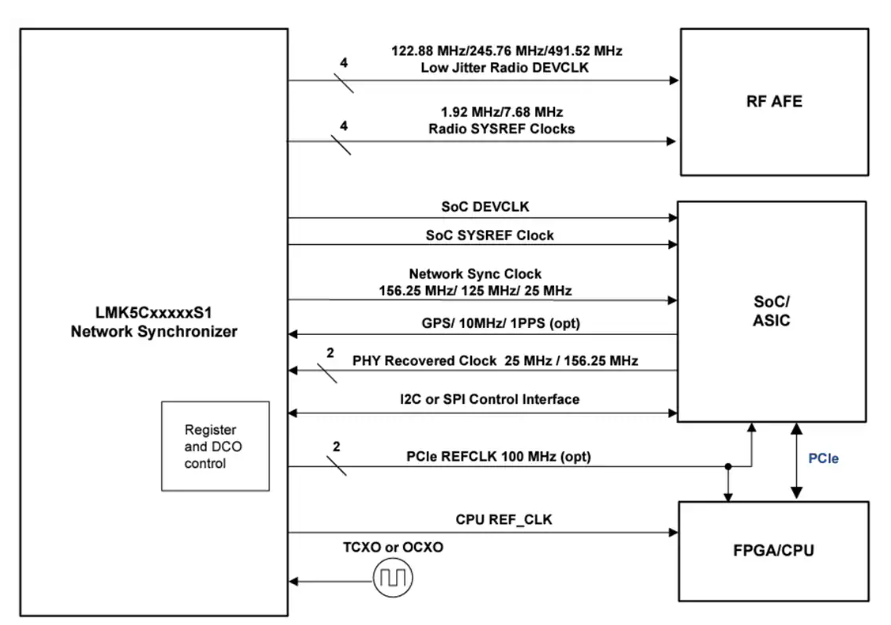

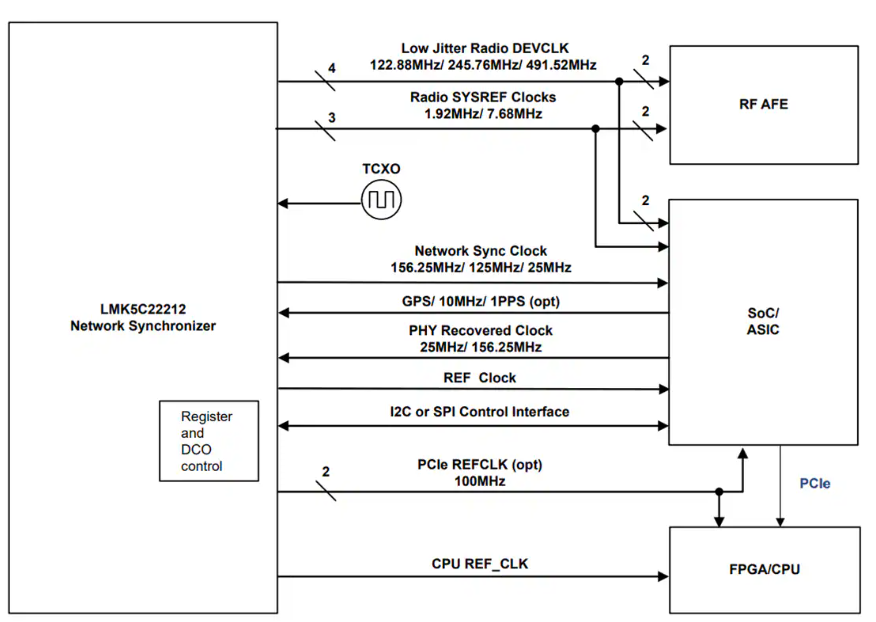

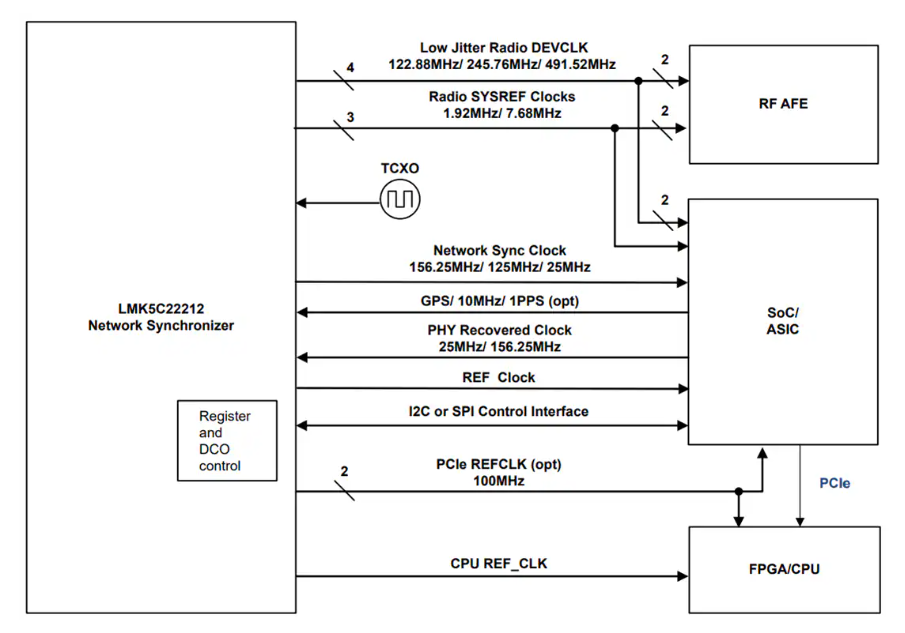

探索LMK5C22212A:高性能網(wǎng)絡同步器的卓越之旅

探索LMK5C22212AS1:高性能網(wǎng)絡同步器的卓越之選

?LMK05028 低抖動雙通道網(wǎng)絡同步器時鐘芯片總結

LMK05318 帶BAW的超低抖動單通道網(wǎng)絡同步器時鐘技術手冊

?LMK5C22212A網(wǎng)絡同步器技術文檔總結

?LMK5B12212網(wǎng)絡同步器與BAW VCO技術總結

高性能網(wǎng)絡同步器LMK5C33216A技術解析與應用

Texas Instruments LMK5C33414AS1網(wǎng)絡同步器數(shù)據(jù)手冊

Texas Instruments LMK5C33216AS1網(wǎng)絡同步器數(shù)據(jù)手冊

Texas Instruments LMK5C22212AS1網(wǎng)絡同步器數(shù)據(jù)手冊

Texas Instruments LMK5C22212A網(wǎng)絡同步器數(shù)據(jù)手冊

帶有同步器的NoC結構是解決FPGA高速時序收斂的關鍵原因嗎?

帶有同步器的NoC結構是解決FPGA高速時序收斂的關鍵原因嗎?

評論