當(dāng)然可以,最小化熱回路PCB ESR和ESL是優(yōu)化效率的重要方法。

對(duì)于功率轉(zhuǎn)換器,寄生參數(shù)最小的熱回路PCB布局能夠改善能效比,降低電壓振鈴,并減少電磁干擾(EMI)。本文討論如何通過(guò)最小化PCB的等效串聯(lián)電阻(ESR)和等效串聯(lián)電感(ESL)來(lái)優(yōu)化熱回路布局設(shè)計(jì)。本文研究并比較了影響因素,包括解耦電容位置、功率FET尺寸和位置以及過(guò)孔布置。通過(guò)實(shí)驗(yàn)驗(yàn)證了分析結(jié)果,并總結(jié)了最小化PCB ESR和ESL的有效方法。

開(kāi)關(guān)模式功率轉(zhuǎn)換器的熱回路是指由高頻(HF)電容和相鄰功率FET形成的臨界高頻交流電流回路。它是功率級(jí)PCB布局的最關(guān)鍵部分,因?yàn)樗遜v/dt和di/dt噪聲成分。設(shè)計(jì)不佳的熱回路布局會(huì)產(chǎn)生較大的PCB寄生參數(shù),包括ESL、ESR和等效并聯(lián)電容(EPC),這些參數(shù)對(duì)功率轉(zhuǎn)換器的效率、開(kāi)關(guān)性能和EMI性能有重大影響。

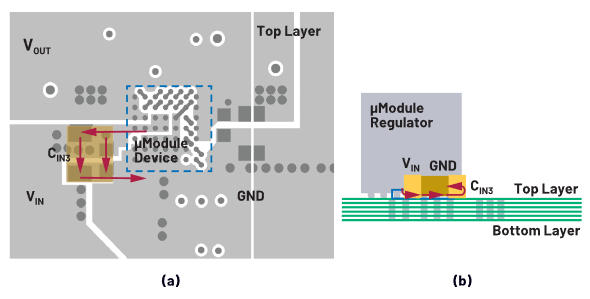

圖2.垂直熱回路1:(a)俯視圖和(b)側(cè)視圖

圖3.垂直熱回路2:(a)俯視圖和(b)側(cè)視圖

圖4.水平熱回路:(a)俯視圖和(b)側(cè)視圖

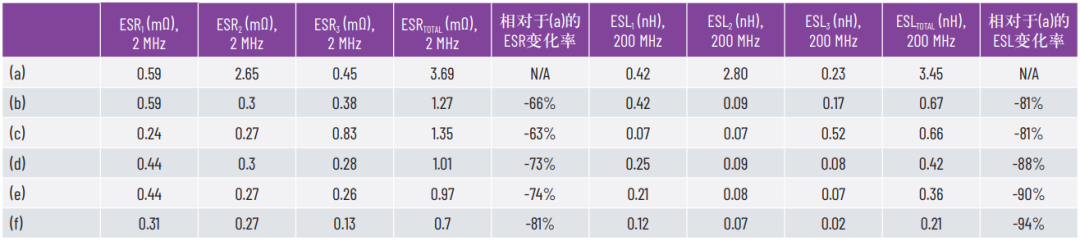

表1.使用FastHenry提取的不同熱回路的PCB ESR和ESL

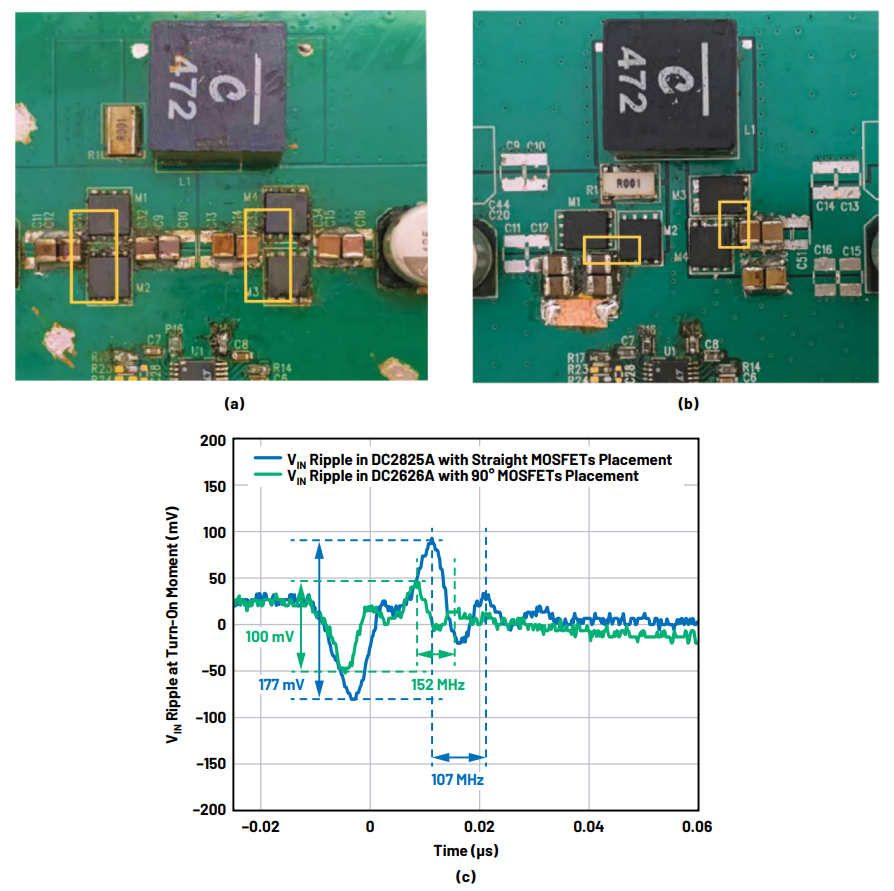

圖5.演示板測(cè)試結(jié)果:(a)效率,(b)水平回路與垂直回路1之間的損耗差異,(c)15A輸出時(shí)M1導(dǎo)通期間的VIN紋波

表2.對(duì)于不同器件形狀和位置,使用FastHenry提取的熱回路PCB ESR和ESL

圖6.熱回路PCB模型:(a)5mm×6mm MOSFET,直線布置;(b)5mm×6mm MOSFET,以90°形狀布置;(c)5mm×6mm MOSFET,以180°形狀布置;(d)兩個(gè)并聯(lián)的3.3mm×3.3mm MOSFET,以90°形狀布置;(e)兩個(gè)并聯(lián)的3.3mm×3.3mm MOSFET,以90°形狀布置,帶有接地層;(f)對(duì)稱的3.3mm×3.3mm MOSFET,位于頂層和底層,以90°形狀布置。

圖7.(a) LT8390/DC2825A熱回路,MOSFET以直線布置;(b) LT8392/DC2626A熱回路,MOSFET以90°形狀布置;(c) M1導(dǎo)通時(shí)的VIN紋波波形。

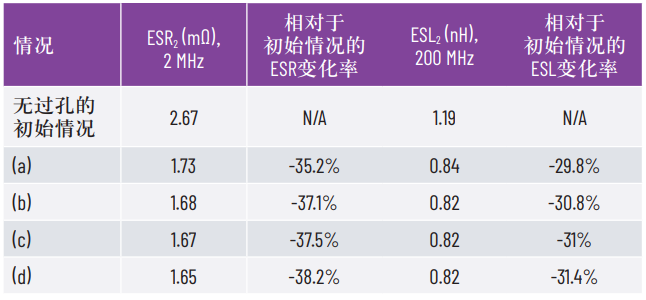

熱回路中的過(guò)孔布局對(duì)回路ESR和ESL也有重要影響。圖8對(duì)使用兩層PCB結(jié)構(gòu)和直線布置功率FET的熱回路進(jìn)行了建模。FET放置在頂層,第二層是接地層。CINGND焊盤和M2源極焊盤之間的寄生阻抗Z2是熱回路的一部分,作為示例進(jìn)行研究。Z2是從FastHenry提取的。表3總結(jié)并比較了不同過(guò)孔布置的仿真ESR2和ESL2。

原文標(biāo)題:如何通過(guò)最小化熱回路來(lái)優(yōu)化開(kāi)關(guān)電源布局?

文章出處:【微信公眾號(hào):亞德諾半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

亞德諾

+關(guān)注

關(guān)注

6文章

4680瀏覽量

16682

原文標(biāo)題:如何通過(guò)最小化熱回路來(lái)優(yōu)化開(kāi)關(guān)電源布局?

文章出處:【微信號(hào):analog_devices,微信公眾號(hào):analog_devices】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

開(kāi)關(guān)電源布局原則

模塊化開(kāi)關(guān)電源組合特性測(cè)試研究

如何通過(guò)最小化熱回路來(lái)優(yōu)化開(kāi)關(guān)電源布局?

如何通過(guò)最小化熱回路來(lái)優(yōu)化開(kāi)關(guān)電源布局?

評(píng)論