如今,市場被驅動在一個盒子中設計具有多種RF協議的產品,稱為網關。無線連接有許多不同的好處,可以提供更好的用戶體驗,而不同的協議則提供了互補的優勢。每個物聯網設備都可以通過不同的協議與互聯網通信,無論是Zigbee,藍牙,Z-Wave或Sub-1 GHz,還是某些專有協議。多協議(無線電)網關在物聯網基礎設施中起著至關重要的作用,因為它們從傳感器場收集數據,并通過Wi-Fi、蜂窩或其他有線和無線網絡將其推送到互聯網上。

多無線電和多協議解決方案的組合可容納兩個或多個無線電同時以相同或不同的頻譜運行不同的多個協議。這種方法通過利用不同的協議來利用更高效、更可靠的數據流。因此,最終用戶可以充分利用優勢,因為他們能夠通過單個單元連接在不同RF頻段和協議上運行的多個設備。

設計多協議緊湊型RF硬件的主要挑戰

多協議硬件的出現是對最近多種不同通信協議的普及的回應。因此,OEM在設計多射頻硬件時面臨著一些關鍵挑戰:

多無線電硬件在天線選擇、放置、仿真、內存估計、外殼設計、材料和現場測試方面需要大量時間。

控制精確的阻抗,以減少干擾、回波損耗、同地無線電之間的共存,使其符合 FCC 和 CE 等管理機構的要求

如果有兩個或多個無線電并發運行并共享相同的頻譜,那么就會共存,這可能會導致相互干擾

測量多無線電硬件的性能參數,如通信延遲、范圍、效率和可靠性

共存往往會影響設備的性能,從而導致數據包丟失或數據損壞、音頻中的爆裂和噼啪聲、工作范圍和覆蓋范圍減小

當多無線電硬件由于不同的標準適用性而出現時,對不同地理區域的法規遵從性也將具有挑戰性

開發多無線電硬件固件時要考慮的事項

當今的物聯網應用變得越來越復雜,它增加了對內存容量的需求。讓我們了解內存和固件附帶的硬件工程解決方案的挑戰:

開發用戶友好且靈活的嵌入式應用需要復雜的狀態機、出色的功耗優化、內存密度和 CPU 性能。RF SoC 或模塊需要更多的閃存和 RAM 優化才能獲得最佳性能

提供無線 (OTA) 固件更新功能需要足夠的閃存來存儲引導加載程序和兩倍的應用程序固件大小,以便在緩沖新固件的同時容納舊固件,如果產品要在當今蓬勃發展的物聯網市場中具有競爭力

在不損失性能的情況下同時管理具有各種網絡架構的多個無線電

在沒有電源的情況下,閃存還可以將用戶配置和安全密鑰內容保留多年,因為閃存中的信息可以在產品的生命周期內讀取和寫入數千次。在這種情況下,利用RAM信息可以快速寫入讀取,從而使處理器能夠以如此高的速度工作并實現邊緣處理。

基于上述挑戰,讓我們舉一個小例子,復雜的可穿戴設備/傳感器/自動化應用可能需要RF模塊提供的128 kB RAM和512 kB閃存。相對簡單的信標應用可能只需要 24 kB RAM 和 192 kB 閃存。

最佳實踐是否有助于克服硬件和固件挑戰?

為了解決上述多射頻硬件、內存和固件挑戰,讓我們了解如何利用其硬件專業知識來覆蓋OEM的痛點領域,以幫助提高產品的整體性能。

標準方法從了解所有RF要求和其他外設的產品開始,列出所有RF接口協議頻率,然后執行模塊/ SoC選擇,相對天線選擇等任務,識別外殼及其材料,模塊的位置和天線。PCB設計的早期階段將進行2D布局規劃,這有助于詳細了解所有RF模塊和參數的實際放置:

模塊/SoC 選擇:選擇標準包括射頻協議、調制技術、制造商、基于驅動程序代碼可用性的 MCU/處理器要求、RAM、閃存、操作系統、監管批準、最大發射功率、接收器靈敏度、電源和數據速率,以提供顯著的性能

內存預算:內存預算對于任何RF模塊來說都是一個非常重要的參數,它純粹是根據RF堆棧大小、對設備數量的支持和應用業務邏輯來定義或計算的。在最終確定模塊/ SoC之前,應充分計算并明確與內存相關的要求

天線選擇和放置:天線選擇是多無線電硬件中最重要的因素,因為選擇取決于頻率范圍、極化、輻射方向圖、增益、饋電點阻抗、VSWR 和功率處理能力用例,如范圍覆蓋范圍和空間。例如,芯片天線與PCB走線天線與外部天線

為了減少兩個相同頻率模塊之間的共存和干擾,天線放置起著至關重要的作用。在這種情況下,天線應彼此垂直放置。我們正嘗試根據法規要求在 2 個 RF 之間建立適當的隔離,2 個天線之間的隔離應等于或大于 30 dB。有時,由于空間限制,不可能實現這種隔離,在此框架中,我們需要注意所有RF天線和輻射方向圖的干擾。我們還需要根據應用需求和性能來調整射頻模塊/SoC的發射功率

射頻仿真:仿真是在產品開發的早期階段預測無線電問題的有效策略。有多個模擬器軟件,如HFSS,CST,AD等,應根據問題類型明智地使用。Volansys等公司幫助執行早期天線仿真,如果由于外殼材料導致任何頻率偏移,則可以在天線放置位置,范圍改進和RF路徑調整方面提供結果和信心

外殼設計及其材料:為了達到最佳效果,請嘗試使用可以平衡環境、可靠性和射頻性能需求的材料最終確定塑料外殼。有時,由于已經預定義的尺寸和結構,COTS 外殼可能會導致放置挑戰,而在定制設計中,我們在 PCB 放置方面具有靈活性,可以獲得更好的隔離和天線放置選項。外殼材料的介電常數/介電常數選擇在射頻性能中起著至關重要的作用。一些在2.4GHz下表現良好的好塑料材料是PC,ABS,PC + ABS,PVC。有時我們也需要為戶外和工業應用選擇金屬外殼,在這種情況下,外部天線選擇將是關鍵點

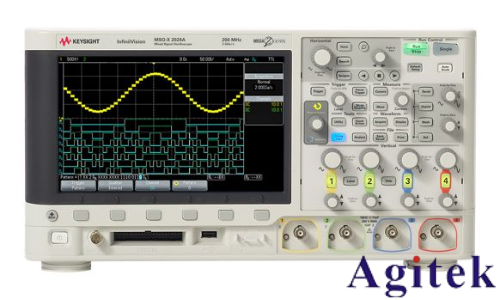

設計驗證測試:RF接口的設計驗證非常重要。需要定義一組驗證測試用例,如天線匹配阻抗和回波損耗、射頻輸出功率測量、接收靈敏度、室內和室外范圍測試、交通繁忙場景的最壞情況射頻環境,并使用分析儀進行監控。要執行一些驗證測試,需要VNA,頻譜分析儀,DSO和RF室類型的實驗室儀器。

審核編輯:郭婷

-

射頻

+關注

關注

106文章

6007瀏覽量

173483 -

ZigBee

+關注

關注

158文章

2305瀏覽量

249859

發布評論請先 登錄

TE Connectivity推出QP 6.5多色電源連接器

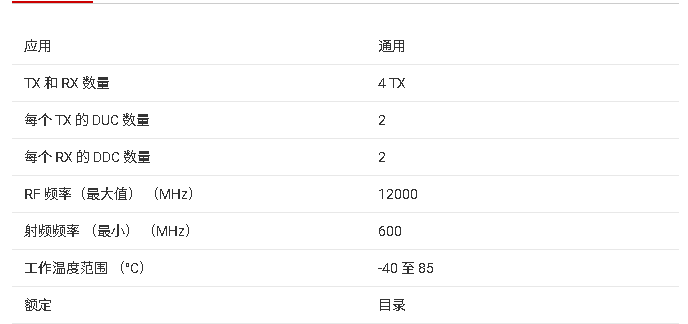

AFE7951 高精度多通道射頻采樣模擬前端(AFE)技術文檔總結

是德示波器DSOX1202射頻干擾抑制的實用方法

如何判斷射頻模塊的硬件是否損壞?

RF SoC技術構建高性能雷達信號收發系統丨應對多通道、高速度與同步挑戰

射頻收發儀 解鎖多衛星信號同步采集的“核心引擎”

LitePoint如應對UWB測試挑戰

阿普奇AK系列憑什么成為機器視覺硬件選型優選?

淺談辰達MOSFET在USB PD快充電源中的應用挑戰與應對

使用基于GaN的OBC應對電動汽車EMI傳導發射挑戰

應對多射頻硬件設計挑戰的方法

應對多射頻硬件設計挑戰的方法

評論