作者:一博科技高速先生成員 孫宜文

上期高速線生簡(jiǎn)單介紹了反射原理也提到了源端串聯(lián)端接,筆者借此篇文章再深入探討下,本文使用Sigrity Topology Explorer 17.4仿真軟件。

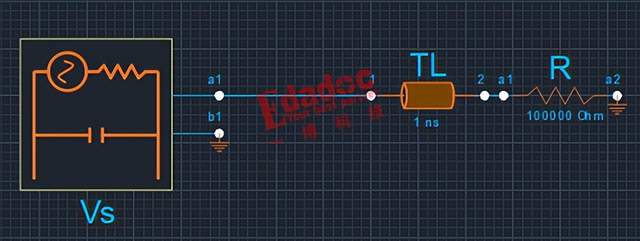

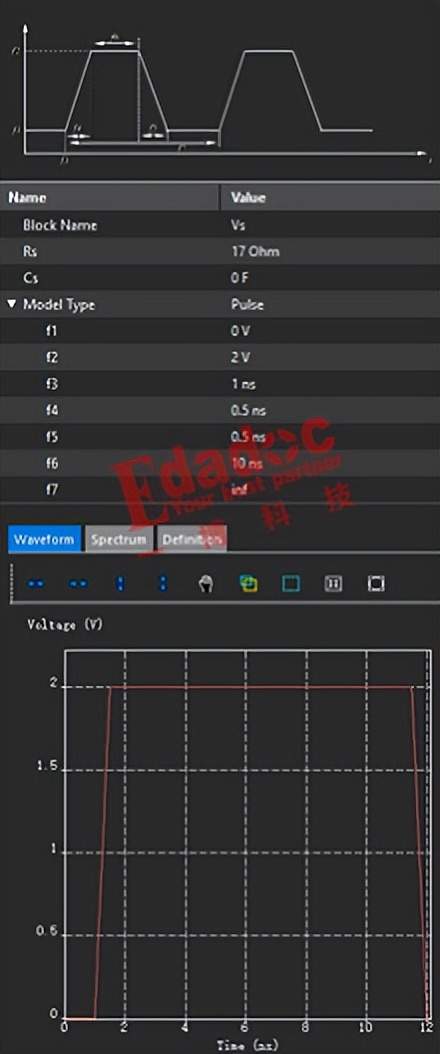

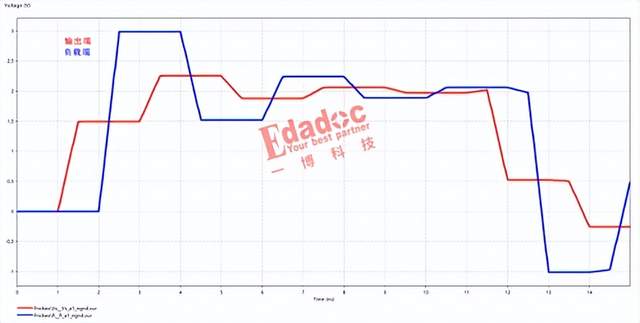

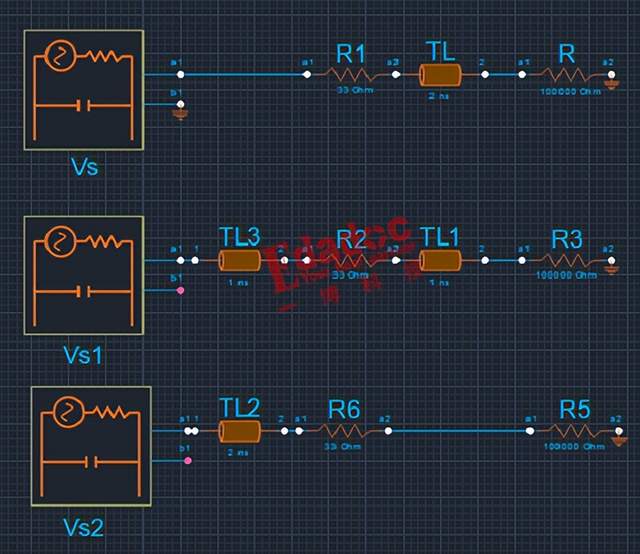

搭建一個(gè)簡(jiǎn)單的電路模型,給一個(gè)上升沿和下降沿均為0.5ns的脈沖波形,電壓跳變?yōu)?V-2V-0V,高電平持續(xù)時(shí)間為10ns,假定芯片內(nèi)部驅(qū)動(dòng)17ohm,路徑中傳輸線的時(shí)延為1ns,一起看下這個(gè)鏈路的接收端和發(fā)送端波形:

仿真結(jié)果:

傳輸線阻抗50ohm,通道末端開路。實(shí)際電路在工作的時(shí)候,末端通常是高阻狀態(tài),也就是和開路差不多。信號(hào)到達(dá)末端全反射,每個(gè)時(shí)間階段觀測(cè)點(diǎn)的電壓值這里就不做解釋了,感興趣的讀者可以結(jié)合反射系數(shù)計(jì)算。

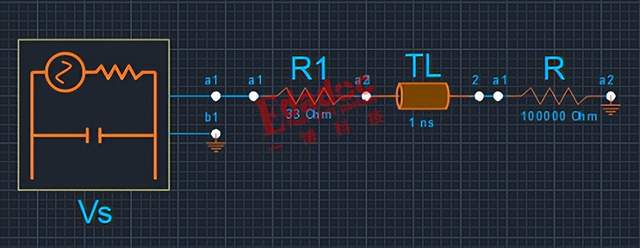

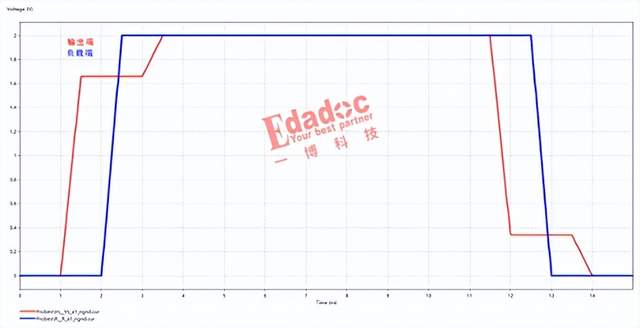

負(fù)載端接收到信號(hào)過(guò)沖很大,當(dāng)在靠近源端的地方加上33ohm的電阻后仿真結(jié)果如下:

源端阻抗得到匹配

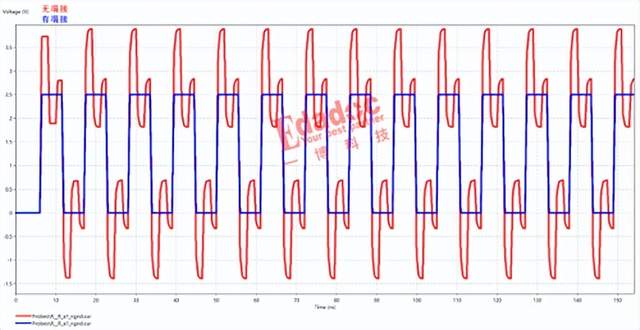

接下來(lái)我們用實(shí)際情況做例子,模擬一個(gè)33Mbps的local bus信號(hào),發(fā)現(xiàn)無(wú)端接時(shí)候的信號(hào)波形,只有一點(diǎn)小小的過(guò)沖,是一個(gè)還不錯(cuò)的信號(hào)波形。

但我們把速率調(diào)到200Mbps,大概是DDR1的速率,發(fā)現(xiàn)不端接會(huì)有很大的過(guò)沖。

看來(lái)隨著速率的提高,阻抗不匹配的鏈路中,源端串聯(lián)還是有必要的。那么我們?cè)撊绾闻袛嗪螘r(shí)需要端接?

這里和信號(hào)的上升時(shí)間Tr及傳輸線延時(shí)TD有關(guān),下面有個(gè)經(jīng)驗(yàn)公式可提供參考:

TD=20%Tr

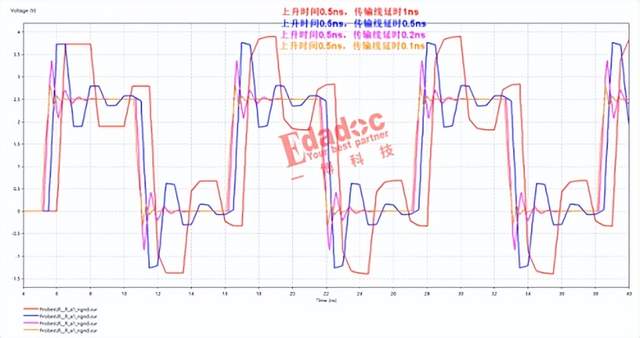

我們來(lái)驗(yàn)證下公式,拿剛才的示例繼續(xù)仿真,調(diào)整參數(shù),上升時(shí)間是0.5ns,傳輸線延時(shí)是1ns,遞減傳輸線延時(shí),從1ns逐漸減小至0.1ns(20%Tr),觀察負(fù)載端的信號(hào)質(zhì)量。

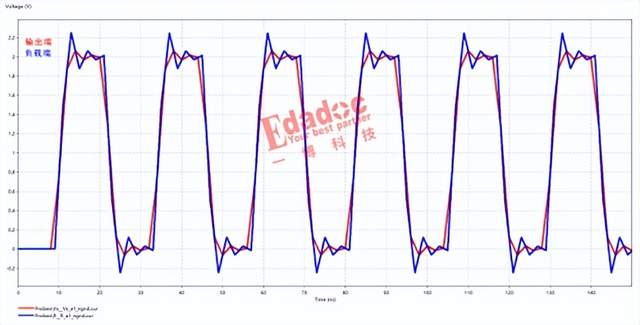

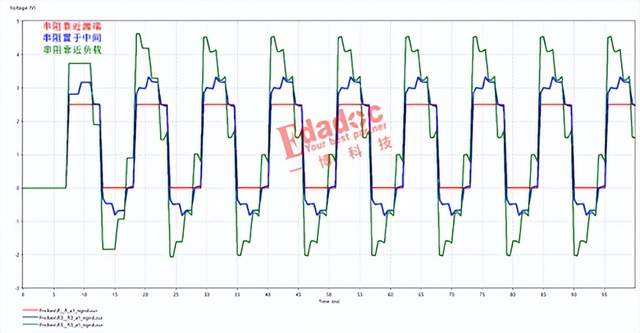

看起來(lái),Tr減小到0.1ns的時(shí)候,反射噪聲約為12%,不同的結(jié)構(gòu),不同的信號(hào)要求不同,具體看信號(hào)能容忍多大的噪聲,僅作為快速定位的經(jīng)驗(yàn)參考。另外需要注意串阻需要盡量靠近源端,不然會(huì)引起多次反射,降低端接效果,甚至導(dǎo)致信號(hào)更差,來(lái)看下不同位置的串阻帶來(lái)的影響。

文末總結(jié)下源端串聯(lián)端接的優(yōu)點(diǎn):

源端串聯(lián)通過(guò)靠近芯片發(fā)送端串聯(lián)電阻,使得該串聯(lián)電阻與芯片的內(nèi)阻之和盡量與傳輸線阻抗一致。該端接簡(jiǎn)單功耗小,不會(huì)給驅(qū)動(dòng)器帶來(lái)額外的直流負(fù)載,只需要一個(gè)電阻就可以抑制驅(qū)動(dòng)端到負(fù)載端的二次反射,常適用于點(diǎn)對(duì)點(diǎn)的拓?fù)渖稀?/p>

審核編輯:湯梓紅

-

串聯(lián)

+關(guān)注

關(guān)注

6文章

446瀏覽量

39579 -

pcb

+關(guān)注

關(guān)注

4405文章

23878瀏覽量

424373 -

仿真軟件

+關(guān)注

關(guān)注

21文章

281瀏覽量

31848

發(fā)布評(píng)論請(qǐng)先 登錄

高速PCB工程師必看:用仿真三步法,讓鋪銅從“隱患”變“保障”

PCB設(shè)計(jì)時(shí)需要知道的16個(gè)概念分享

技能變現(xiàn),千元獎(jiǎng)金等你拿!深圳寶安區(qū)PCB設(shè)計(jì)與電路仿真大賽邀請(qǐng)你出戰(zhàn)

PCB設(shè)計(jì) | AI如何顛覆PCB設(shè)計(jì)?從手動(dòng)布線到智能自動(dòng)化的30年演進(jìn)

?TE Connectivity ES-Cap 0號(hào)端接端蓋技術(shù)解析與應(yīng)用指南

大功率PCB設(shè)計(jì) (一):電壓需求與隔離

告別傳統(tǒng)仿真困局:Sigrity X 三大突破破解PCB設(shè)計(jì)難題

深度解讀PCB設(shè)計(jì)布局準(zhǔn)則

上海圖元軟件國(guó)產(chǎn)高端PCB設(shè)計(jì)解決方案

PCB設(shè)計(jì),輕松歸檔,效率倍增!

原理圖和PCB設(shè)計(jì)中的常見(jiàn)錯(cuò)誤

開關(guān)電源的輸入電容的PCB設(shè)計(jì)技巧

SMT貼片前必知!PCB設(shè)計(jì)審查全攻

【功能上線】華秋PCB下單新增“3D仿真預(yù)覽”,讓PCB設(shè)計(jì)缺陷無(wú)處遁形

PCB設(shè)計(jì)仿真之探討源端串聯(lián)端接

PCB設(shè)計(jì)仿真之探討源端串聯(lián)端接

評(píng)論