在這個由兩部分組成的系列的第 1 部分中,我們討論了復(fù)雜 SoC 和系統(tǒng)設(shè)計中對早期功耗分析的需求,并介紹了 VisualSim 圖形建模工具作為全面的能源仿真解決方案。在第 2 部分中,我們將展示 VisualSim 在多核嵌入式環(huán)境中預(yù)測和表達(dá)多個場景(偏移并發(fā)任務(wù);比較 1 GHz 的單核與 250 MHz 的四個核;動態(tài)電壓頻率縮放 (DVFS)和功率門控)的功率值時的性能。

對新狀態(tài)的更改可以是開始新的執(zhí)行、在一段時間不活動后進入深度睡眠、執(zhí)行低優(yōu)先級與高優(yōu)先級用例,以及內(nèi)存激活和刷新等特定條件。功率表達(dá)式值必須與時鐘速度和溫度等時序?qū)傩酝阶兓?/p>

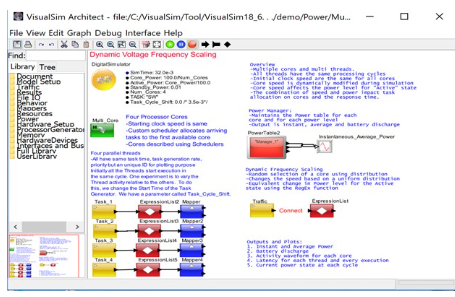

系統(tǒng)級功耗探索可以評估各種功耗降低和低功耗技術(shù)的優(yōu)點和節(jié)省的能源。在這里,我們將討論這些技術(shù),并使用 VisualSim 中的模擬模型解釋它們的影響。出于本研究的目的,我們使用四核處理器、調(diào)度程序代替 RTOS、四個并發(fā)線程以及按順序觸發(fā)處理資源上的線程的中斷。我們已經(jīng)針對內(nèi)核上的可變時鐘速度、1 到 4 之間的可變內(nèi)核數(shù)以及線程觸發(fā)之間的偏移對模型進行了參數(shù)化。此外,我們還集成了電壓和時鐘速度動態(tài)變化的邏輯。

與此描述相關(guān)的框圖如圖 2 所示。

圖2.多核架構(gòu)和四個并發(fā)線程的系統(tǒng)級框圖

進行以下實驗,我們查看每個場景的延遲和功耗。

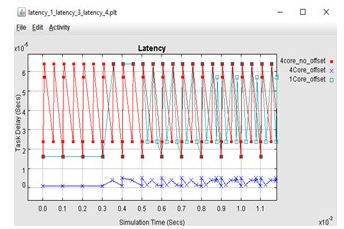

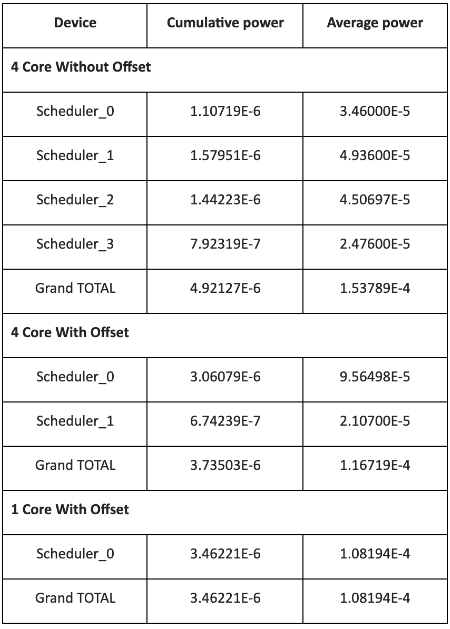

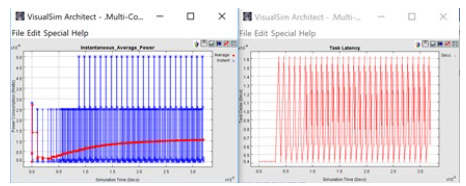

偏移并發(fā)任務(wù):有四個任務(wù),默認(rèn)情況下,這些任務(wù)是同時觸發(fā)的。在這個實驗中,我們將每個任務(wù)移動了 3.5 毫秒。這樣,任務(wù)就不會同時啟動。如圖3所示,這種方法降低了功耗尖峰。最大尖峰從 1.0mW 到 7.5mW,節(jié)省 25%。從圖 4 可以看出,延遲確實從 7ms 降低到 0.5ms,這是一個顯著的改進。從圖 3 和表 1 中得出的有趣推論是,所有四個內(nèi)核都不再被利用,并且處理資源的任務(wù)請求中只有偶爾的重疊。對平均功耗沒有影響。

比較運行在 1 GHz 的單核和運行在 250 MHz 的四個內(nèi)核:在這個實驗中,我們將所有任務(wù)都定位在一個以 1GHz 速度運行的單個內(nèi)核上。我們使用線程的偏移量。圖3的結(jié)果顯示,瞬時功率和平均功率均顯著降低。從圖 4 中我們可以看到延遲圖沒有顯著影響。可以看到,峰值功率與1.0mW的非失調(diào)值相同,但平均功率減少了一半,為0.15mW。這是因為處理速度存在相當(dāng)大的浪費。

圖3.LHS 顯示隨時間推移的平均功率/RHS 顯示隨時間變化的即時功率

圖4.一段時間內(nèi)的延遲

表 1.上述實驗的累積和平均功效

任務(wù)中具有偏移的一個內(nèi)核的累積和平均功耗小于有偏移和不帶偏移的 4 個內(nèi)核。

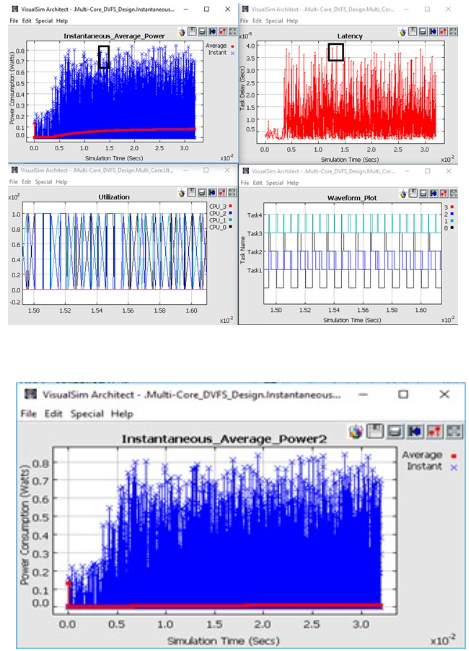

動態(tài)電壓頻率調(diào)節(jié) (DVFS):這是節(jié)省功率的首選技術(shù),通過根據(jù)任務(wù)要求改變時鐘速度來完成。一個很好的例子是 x86 處理器,其額定頻率為 3.2GHz,但在筆記本電腦上以 1.8 GHz 運行。使用原型板,當(dāng)電壓頻繁調(diào)整時,很難預(yù)測任務(wù)的延遲。在相關(guān)模型中,我們沒有實現(xiàn)特定的算法,并且能夠看到功率和延遲在很寬的時鐘速度范圍內(nèi)的變化。結(jié)果如圖 5 所示。我們將使用四個內(nèi)核和四個偏移線程進行此運行。請注意,由于時鐘速度的變化,功率和延遲會波動。延遲與原始偏移版本相同。DVFS幫助我們大規(guī)模降低功耗。

從圖 4 中我們可以看到,所有任務(wù)的時隙都不相同,隨著傳入任務(wù)的增加,時鐘速度會根據(jù)需求隨每個內(nèi)核而變化。

圖 6:通過實施電源管理降低平均功耗

強制內(nèi)核在特定時間段后進入待機狀態(tài)將降低功耗。從圖 6 中,我們可以直觀地看到,實施電源管理后功耗會降低。為了擴展DVFS示例,可以修改每個任務(wù)的開始和頻率。在分析生成的統(tǒng)計信息時,我們可以看到正在使用的內(nèi)核數(shù)量減少(core_3),從而消除了額外的待機功率并減少了功耗。如您所見,同時探索電源選項和軟件調(diào)度非常重要。這將確保所需的響應(yīng)時間,同時減少功耗。

功率門控:這是在一段時間不活動后將處理單元移動到較低功率狀態(tài)的過程。一個常見的例子是筆記本電腦從活動到待機再到睡眠和休眠。在此模型中,我們將功率門控狀態(tài)機邏輯添加到電源表中。我們將空閑延遲設(shè)置為 10us,將轉(zhuǎn)換時間設(shè)置為 1 us。設(shè)備在待機狀態(tài)下停留的時間較短。從圖 6 中,我們可以看到,只要內(nèi)核處于非活動狀態(tài),內(nèi)核的狀態(tài)就會從待機變?yōu)榭臻e。轉(zhuǎn)換時間對延遲的影響最小到零。

圖 6:電源門控,當(dāng)內(nèi)核處于非活動狀態(tài) 0.1ms 時,內(nèi)核從待機狀態(tài)移動到空閑狀態(tài),轉(zhuǎn)換時間為 1.0us

結(jié)論

系統(tǒng)級仿真可用于半導(dǎo)體級和系統(tǒng)級的廣泛功率分析。將功率探索與性能研究結(jié)合使用可確保權(quán)衡同時進行,從而確保更高質(zhì)量的產(chǎn)品。許多功耗研究可以在產(chǎn)品實施之前在系統(tǒng)級完成,并消除集成過程中的所有意外。

這項研究的一個附帶好處是,熱和機械工程師可以獲得經(jīng)過充分驗證的數(shù)據(jù),而不是近似的最佳判斷信息。VisualSim 等軟件工具將性能和功耗分析集成到單個系統(tǒng)級模型中,有助于更快地構(gòu)建模型,使用較小的模型集減少模型維護,并在設(shè)計周期的早期進行更高質(zhì)量的探索。此外,這些系統(tǒng)級工具在設(shè)計中比以前更早地推動探索:

每個任務(wù)中偏移的含義可降低功耗和延遲

減少內(nèi)核數(shù)量并提高處理器速度可顯著降低功耗

根據(jù)任務(wù)要求改變內(nèi)核的時鐘速度是降低系統(tǒng)功耗的最佳方法

使內(nèi)核在非活動期間空閑,減少系統(tǒng)中的電源浪費

審核編輯:郭婷

-

嵌入式

+關(guān)注

關(guān)注

5200文章

20458瀏覽量

334306 -

soc

+關(guān)注

關(guān)注

40文章

4576瀏覽量

229227 -

RTOS

+關(guān)注

關(guān)注

25文章

866瀏覽量

123046

發(fā)布評論請先 登錄

STM32開發(fā)中的五大嵌入式系統(tǒng)

什么是嵌入式應(yīng)用開發(fā)?

C語言單元測試在嵌入式軟件開發(fā)中的作用及專業(yè)工具的應(yīng)用

什么是嵌入式操作系統(tǒng)?

C語言在嵌入式開發(fā)中的應(yīng)用

嵌入式和FPGA的區(qū)別

嵌入式實時操作系統(tǒng)的特點

嵌入式電力儀表在配電系統(tǒng)中的應(yīng)用與選型

Java 在物聯(lián)網(wǎng)與嵌入式系統(tǒng)中的應(yīng)用前景與挑戰(zhàn)

是德示波器MSOX3052T在嵌入式系統(tǒng)中的應(yīng)用

嵌入式工程師為什么要學(xué)QT?

Linux嵌入式和單片機嵌入式的區(qū)別?

嵌入式主板特點與應(yīng)用場景解析

Python在嵌入式系統(tǒng)中的應(yīng)用場景

遠(yuǎn)距版嵌入式掃碼機在戶外掃碼收費場景中的應(yīng)用解析

VisualSim在多核嵌入式環(huán)境中預(yù)測和表達(dá)多個場景展示

VisualSim在多核嵌入式環(huán)境中預(yù)測和表達(dá)多個場景展示

評論