多核處理器越來越多地被采用在關鍵系統領域,特別是在關鍵任務的軍事環境中。它們為單核處理器的長期可用性問題以及促進軍事系統創新所需的處理能力增加的問題提供了解決方案。由于多核處理器既不提供確定性環境,也不提供可預測的軟件執行時間,因此需要一種新的驗證方法(一種解決多核時序分析挑戰的方法)來安全使用。

處理器的SWaP(尺寸,重量和功率)問題的持續進展導致多核供電的手機比阿波羅11號月球著陸器包含更多的功率。使用多核處理器帶來的好處導致該技術在主流技術行業中得到廣泛采用,單核處理器現在只占市場的一小部分。由于這種轉變,芯片制造商正在遠離生產這些傳統處理器,它們的長期可用性受到嚴重質疑。

隨著單核處理器的供應不斷減少,現代嵌入式系統越來越受歡迎,采用多核處理器是不可避免的。然而,在關鍵任務軍事領域安全使用這些處理器具有挑戰性,因為它們既不提供確定性環境,也不提供可預測的軟件執行時間。

軍用航空電子認證的黃金標準

DO-178C 是 FAA [聯邦航空管理局] 和 EASA [歐盟航空安全局] 等著名認證機構批準所有商業軟件航空航天系統的主要文件。多年來,它也已成為在軍用航空電子系統中使用軟件的事實黃金標準。

美國聯邦航空局用題為“多核處理器”的立場文件CAST-32A補充了DO-178C指南,以解決航空中越來越多地使用多核處理器的問題。

美國陸軍指定的主要適航機構AMRDEC航空工程局(AED)發布了一份名為“多核處理器(MCP)適航要求”的指導文件草案,其中DO-178C和CAST-32A目標被確定為可用于滿足MCP [多核處理器]適航要求的指南。

時序分析是 CAST-32A 指南中確定的核心目標之一,并具體由稱為 MCP_Software_1 的目標解決,該目標需要證據證明所有托管軟件組件正常運行,并且在多核環境中運行時有足夠的時間完成其執行。這是一個非常具有挑戰性的目標,并且已被證明是旨在認證多核項目的軍事和航空航天公司的嚴重障礙。

分析多核時序行為

由于多種原因,旨在驗證單核系統時序行為的驗證解決方案不適用于多核時序分析,主要是因為這些解決方案無法考慮資源爭用引起的干擾的影響。為了驗證多核系統的時序行為,需要專門解決多核時序分析挑戰的新方法。

考慮資源爭用和干擾

多核系統任務中任務的計時行為不僅受其上運行的軟件及其輸入的影響,還受與其他內核上運行的任務共享的資源(如總線、緩存和 GPU)爭用的影響。為了設計實驗來分析多核系統的時序行為,必須識別并考慮干擾源。

圖 1 顯示了多核架構的簡化示例,其中總線在多個內核之間共享。由核心 N 訪問此總線而導致的流量可能會影響在核心 0 上運行的應用程序的計時行為,該應用程序需要訪問此總線。

圖1|多核系統中的干擾信道示例。

必須測試假設

為了分析多核系統的時序行為,必然需要對所研究系統的行為進行一些假設,包括存在的干擾信道的影響。由于多核系統的復雜性,對系統做出的看似合乎邏輯的假設以后可能會被證明是不正確的,可能需要一個迭代過程來做出假設,測試它們,并使用分析結果來完善下一輪測試的假設。

這最好用一個實際示例來解釋:正在研究的是運行在 Xilinx Zynq Ultrascale+ ZCU102 目標板上的內存密集型應用對不同干擾水平的敏感性。運行應用程序的應用程序處理單元有四個內核。合理的假設是,由于對系統的先驗了解,二級緩存是此應用的主要干擾通道。為了驗證這一假設,在應用程序運行時執行了一項測試,同時從 0 到 3 個競爭者內核上運行的任務對 L2 緩存進行持續訪問。

圖2|CPU 周期和二級緩存未命中。

如果假設有效,則應用程序執行的二級緩存未命中數和 CPU 周期數將隨著每個額外的競爭者內核而增加。該圖顯示,這一假設一直持續到引入第三個競爭者核心。這增加了 CPU 周期數,但二級緩存未命中數與只有兩個競爭者內核處于活動狀態時大致相同。

多核系統中干擾效應的復雜性意味著設計人員應該期望需要迭代周期來形成假設,測試它們,并使用分析結果形成新的假設。雖然沒有辦法自動化這個過程,但工程師可以在如何形成關于多核處理器的合理假設以及如何通過處理多個項目和積累經驗來在調查工作中重新評估這些假設方面發展專業知識。有效的重新評估和測試將導致全面了解多核處理器的行為方式以及哪些因素會影響其計時行為。

在真實硬件上進行測試

多核CPU很復雜,其內部通常是隱藏的,因此純分析模型在理解其時序行為方面的用途有限。雖然純分析(靜態分析)模型可以為單核系統提供可用的時序估計,但對于多核系統則不是這種情況。即使使用這些方法,它們也會根據多核配置的病理最壞情況行為產生高度悲觀的結果,并且這些結果將沒有實際用途。

要從多核系統生成可用的時序指標,必須測量系統本身的時序行為。Rapita Systems的工程師使用巴塞羅那超級計算中心開發的一系列微基準來強調特定的共享資源,并在發生這種爭用時觀察應用程序的計時行為。通過使用該技術對特定共享資源應用可配置的爭用程度,可以制定實驗,以幫助根據可行的計時環境分析計時指標。這些實驗可以產生滿足CAST-32A定時目標所需的關鍵證據,例如最壞情況執行時間(WCET)。

多核時序分析不能完全自動化

多核處理器的復雜性意味著構建全自動時序分析解決方案是不現實的。雖然工具支持可以自動化大多數數據收集和分析過程,但需要工程智慧和專業知識來了解系統和指導工具使用以產生必要的證據。工程師在了解多核系統、研究干擾信道和使用支持工具方面的經驗越多,分析過程的效率就越高。

未來的關鍵任務

軍事領域使用的關鍵任務嵌入式系統越來越多地使用多核處理器。這些系統的認證考慮因素不是事后才考慮的,而是在開發過程的早期考慮的。值得慶幸的是,DO-178C 提供了一組強大的目標,以確保安全可靠地使用這些處理器。多核系統的時序分析具有挑戰性,但久經考驗的解決方案可以在商業環境中執行。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

20255瀏覽量

252306 -

MCP

+關注

關注

0文章

289瀏覽量

15013

發布評論請先 登錄

探索TDA54x Jacinto?處理器:高性能與安全的完美融合

MAX77874:16A高性能四相降壓調節器,引領多核心處理器電源解決方案

解析Linux的進程、線程和協程

瑞芯微SOC智能視覺AI處理器

FreeRTOS和uC/OS-II的功能特性

云拼接處理器的性能如何?

Andes晶心科技推出AndesCore 46系列處理器家族

關于人工智能處理器的11個誤解

T113-i芯片技術解析:高性能嵌入式處理器的創新設計

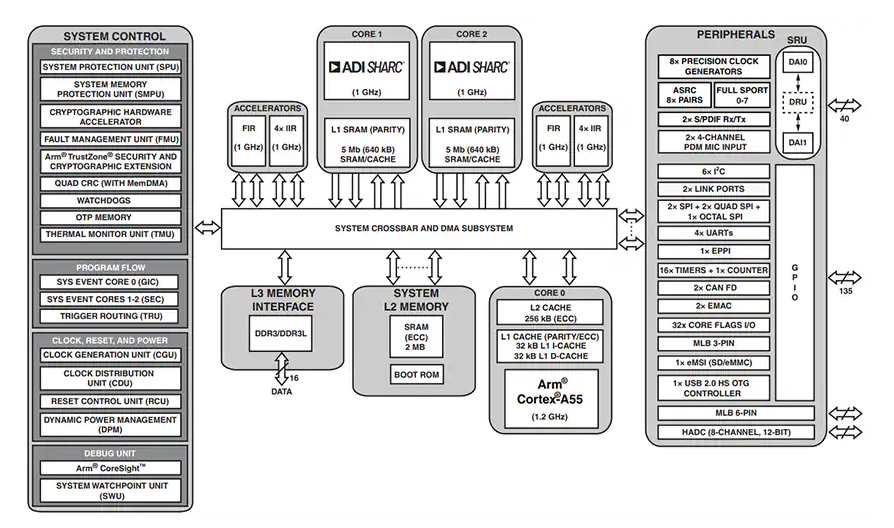

Analog Devices Inc. ADSP-SC598雙SHARC+?數字信號處理器數據手冊

任務關鍵型環境中的多核處理器

任務關鍵型環境中的多核處理器

評論