本文由 AMD 賽靈思 Vitis 統(tǒng)一軟件平臺產(chǎn)品營銷經(jīng)理

Eddie Wu 撰寫

Vitis 統(tǒng)一軟件平臺 2022.2 版已正式發(fā)布!主要增強(qiáng)特性包括下列內(nèi)容:

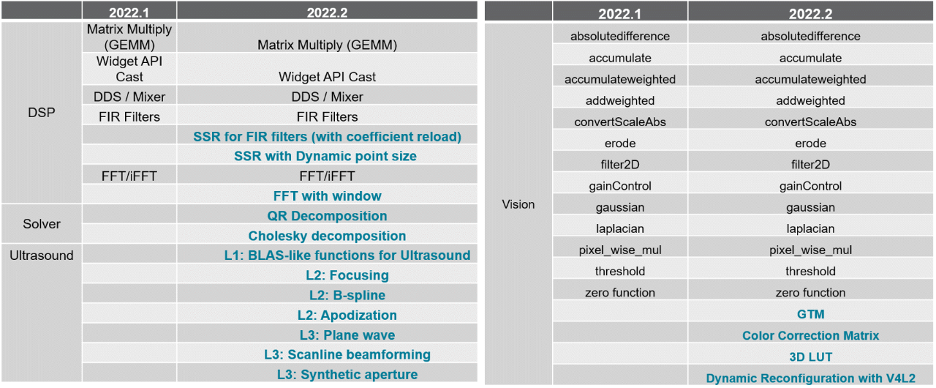

為 Versal AI 引擎陣列提供新的 Vitis 庫功能:

DSP 庫 - 增強(qiáng)特性。

求解器庫功能。

視覺庫功能。

超聲庫功能。

針對 Versal 器件的設(shè)計流程增強(qiáng):

控制內(nèi)核在 AI 引擎陣列中的相對布局,從而提升性能,提高利用率。

強(qiáng)化面向 Versal ACAP 設(shè)計的配置與調(diào)試功能,包括死鎖檢測、較大布線數(shù)據(jù)采集、RTL/Python 測試平臺支持。

Vitis 集成設(shè)計環(huán)境下的異構(gòu)設(shè)計的新仿真選項。

以下是對部分主要增強(qiáng)特性的介紹:

Vitis 庫經(jīng)過強(qiáng)化,支持更多AI 引擎陣列功能

通過系數(shù)再加載功能和動態(tài)點大小,DSP 庫現(xiàn)可支持超高采樣率 (SSR) FIR 濾波器。在指向 AI 引擎陣列的 FFT 功能中,新增 FFT 窗口化元素。

對于求解器庫,為 AI 引擎陣列新增兩個矩陣分解功能,分別是 QR 分解和喬里斯基 (Cholesky) 分解。這兩種是得到廣泛運用的矩陣運算。

Vitis 視覺庫為 AI 引擎陣列新增四項功能:全局色調(diào)映射 (GTM)、色彩校正矩陣、3D 查找表和符合 V4L2 的動態(tài)重配置。

2022.2 版還提供新的超聲庫,其中包括 L1 級到 L3 級功能:

L1 例程為超聲波提供類似基本線性代數(shù)子程序 (BLAS) 的功能。

L2 例程為聚焦、變跡和 b 樣條等功能提供 AI 引擎圖。

L3 例程提供合成孔徑、平面波和掃描線波束成型等超聲子系統(tǒng)。

2022.1 版和 2022.2 版為 AI 引擎提供的 Vitis 庫的更詳細(xì)介紹請見下文。

Versal ACAP 設(shè)計流程強(qiáng)化

AI 引擎編譯器

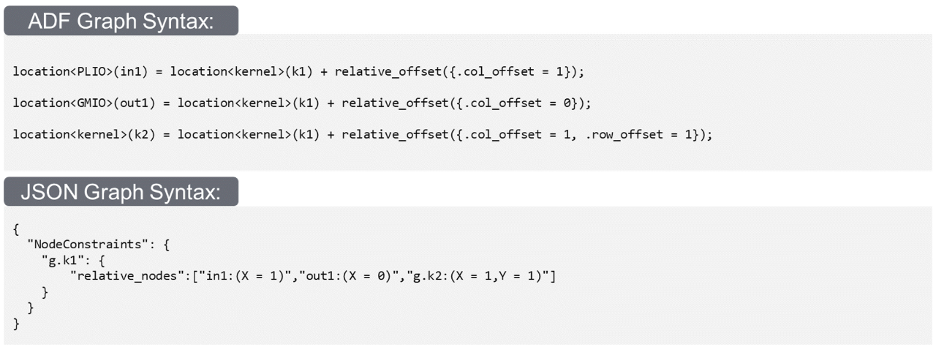

在這個新版本中,AI 引擎相對約束提供了在 AI 引擎內(nèi)控制內(nèi)核相對布局的途徑。這有利于用戶從 AI 引擎陣列獲得更高性能和更充分的利用率。可以將約束定義為自適應(yīng)數(shù)據(jù)流程 (ADF) 圖格式和 JavaScript 對象標(biāo)記 (JSON) 格式。

ADF 和 JSON 圖形語法例如下所示:

Vitis 工具仿真與分析的新特性

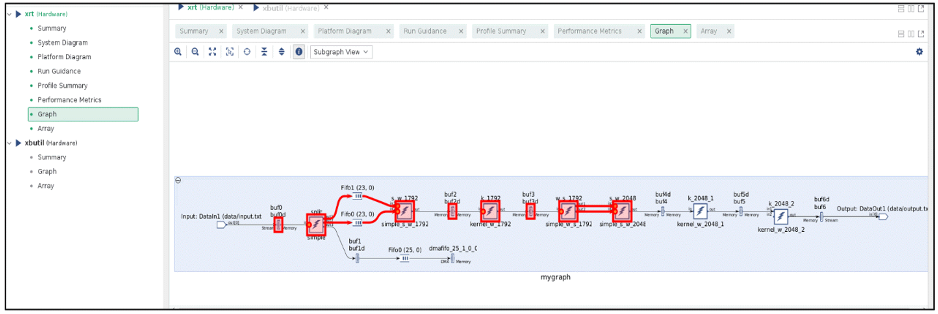

1. 采用 Vitis 分析器配置、調(diào)試和分析 AI 引擎

在 2022.2 版中,可以在 Vitis 分析器中的硬件模擬階段分析 AI 引擎的狀態(tài),為調(diào)試提供幫助。而在 2022.2 版以前,用戶必須在硬件內(nèi)構(gòu)建設(shè)計,才能開展同樣的分析。這項特性允許用戶在構(gòu)建硬件前開展配置,加快迭代速度,同時幫助縮短設(shè)計周期。

從 2022.1 版起,通過 Linux 上的 xbutil 和 XRT,就可以啟用死鎖檢測。現(xiàn)在使用賽靈思系統(tǒng)調(diào)試器 (XSDB) 也支持同樣的特性。這對裸機(jī)用戶有所幫助。可以生成與 xbutil 生成的文件等效的 JSON 文件。這個文件可以導(dǎo)入 Vitis 分析器查看。

死鎖檢測流程如下所示:

這項新特性將對 XRT 的支持?jǐn)U展到對基于 AI 引擎的 XSDB 流程的支持。

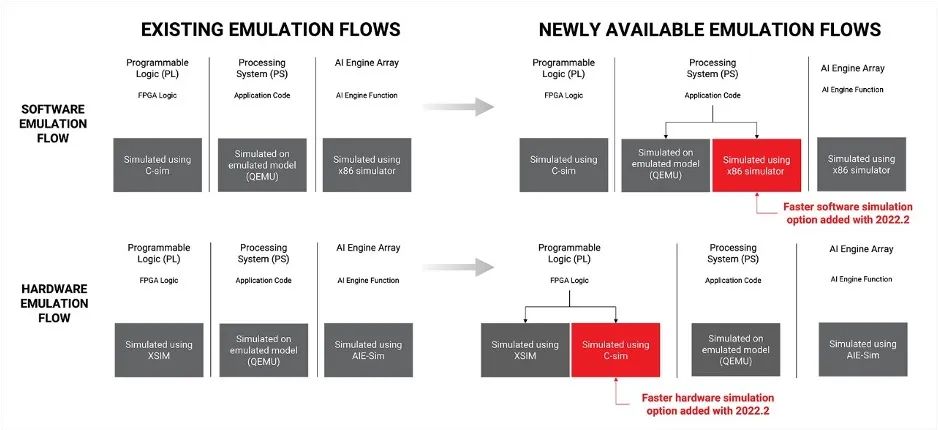

2. 支持在 x86 主機(jī)上用 PS 應(yīng)用開展軟件模擬

除了在嵌入式平臺上的 QEMU,現(xiàn)在用戶可以在 x86 仿真器上通過編譯和運行處理系統(tǒng) (PS) 應(yīng)用來模擬軟件,加快軟件模擬的速度。這項功能無需創(chuàng)建 SD 卡鏡像,也無需在 QEMU 中引導(dǎo) Linux,從而避免相關(guān)開銷,加快周轉(zhuǎn)時間。用戶可以使用 XRT 控制加速內(nèi)核,自己則專注于高級功能模型。使用此功能前,必須在主機(jī)上安裝賽靈思運行時庫 (XRT)。

3. 除了 RTL 以外,還可以使用 SystemC 功能模型進(jìn)行硬件模擬

與 RTL 相比,SystemC 功能模型能加快編譯速度,縮短執(zhí)行時間。此外,用戶也可以搭配使用 C 內(nèi)核和 RTL 內(nèi)核來調(diào)試 RTL 塊。在 2022.2 版中,支持 C/C++ 內(nèi)核、基于 AXI4-Memory Map 的內(nèi)核和基于 AXI4-Stream 的內(nèi)核。

新的仿真選項進(jìn)一步豐富了用戶可用的功能仿真流程,如下所示。這些新的仿真流程主要用于協(xié)助實現(xiàn)快速功能仿真。

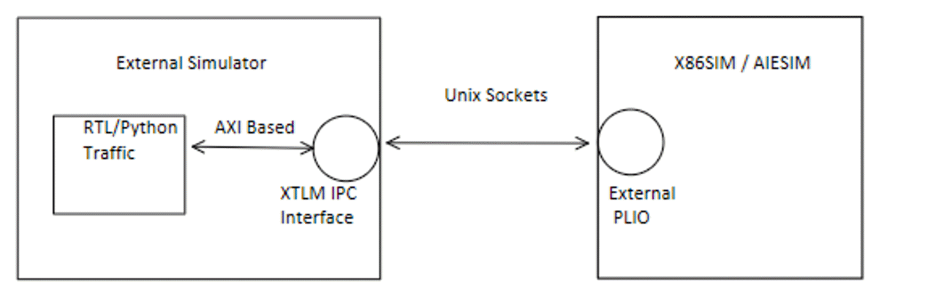

4.使用簡單的 RTL 測試平臺或基于 Python 腳本的流量生成器為仿真 AI 引擎內(nèi)核提供支持

這項特性允許用戶將 RTL 測試平臺重復(fù)用作流量生成器 (TG) 或使用 Python 創(chuàng)建流量生成器。這樣做無需完整平臺就可以單獨驗證內(nèi)核。

RTL 仿真器使用上述測試平臺,x86SIM/AIESIM 負(fù)責(zé)仿真 C 或 AI 引擎內(nèi)核代碼,利用 Unix 套接字和 XTLM IPC 接口在兩個進(jìn)程間建立通信,如下所示:

通過 Vitis 軟件平臺 2022.2 版,我們現(xiàn)在支持Python、VHDL、Verilog 和基于 SystemVerilog 的流量生成器。

審核編輯:湯梓紅

-

賽靈思

+關(guān)注

關(guān)注

33文章

1798瀏覽量

133435 -

Versal

+關(guān)注

關(guān)注

1文章

173瀏覽量

8472 -

Vitis

+關(guān)注

關(guān)注

0文章

157瀏覽量

8348

原文標(biāo)題:Vitis? 統(tǒng)一軟件平臺 2022.2 最新更新

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發(fā)者社區(qū)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

為什么國產(chǎn)MCU的工程生態(tài)很難統(tǒng)一?

軟通動力簽約數(shù)字化統(tǒng)一支付平臺項目

全新AMD Vitis統(tǒng)一軟件平臺2025.2版本發(fā)布

嵌入式開發(fā)工具版本的選擇策略

潤和軟件繪就云邊端統(tǒng)一操作系統(tǒng)新藍(lán)圖

如何在AMD Vitis Unified IDE中使用系統(tǒng)設(shè)備樹

AMD Vitis AI 5.1測試版現(xiàn)已開放下載

AMD Vitis AI 5.1測試版發(fā)布

如何在應(yīng)用程序調(diào)試期間分析棧和堆使用情況

芯盾時代助力寧夏銀行統(tǒng)一身份認(rèn)證平臺建設(shè)

全新AMD Vitis統(tǒng)一軟件平臺2025.1版本發(fā)布

使用AMD Vitis Unified IDE創(chuàng)建HLS組件

如何使用AMD Vitis HLS創(chuàng)建HLS IP

Vitis?統(tǒng)一軟件平臺2022.2最新更新

Vitis?統(tǒng)一軟件平臺2022.2最新更新

評論