汽車作為一種傳統的工業產品,如今也隨著科技發展不斷推陳出新。如果說動力系統是汽車的心臟,那么車載芯片就是汽車的大腦。隨著不斷有先進的工藝和架構應用于車載芯片領域,車載芯片得性能日益提升,用以支持多樣化的娛樂功能和貼心的輔助駕駛功能,為人們提供了更好的駕乘體驗。在單核處理器不能滿足車載芯片對性能的需求時,車載芯片會采用多核處理器架構以達到更高的處理能力。每個處理器都帶有緩存數據的組件(cache),多核系統設計需要考慮處理器緩存數據的一致性,防止處理器使用過時的數據從而導致運行出錯。因此一致性總線應運而生,它保證了各個處理器緩存數據的一致性,使得多個處理器可以共同處理同一項事務,讓處理器的性能得到了很好得發揮。本文從一致性總線的由來、結構和功能等方面,對其進行了簡單介紹,希望能給讀者帶來一些啟發。

總線的由來

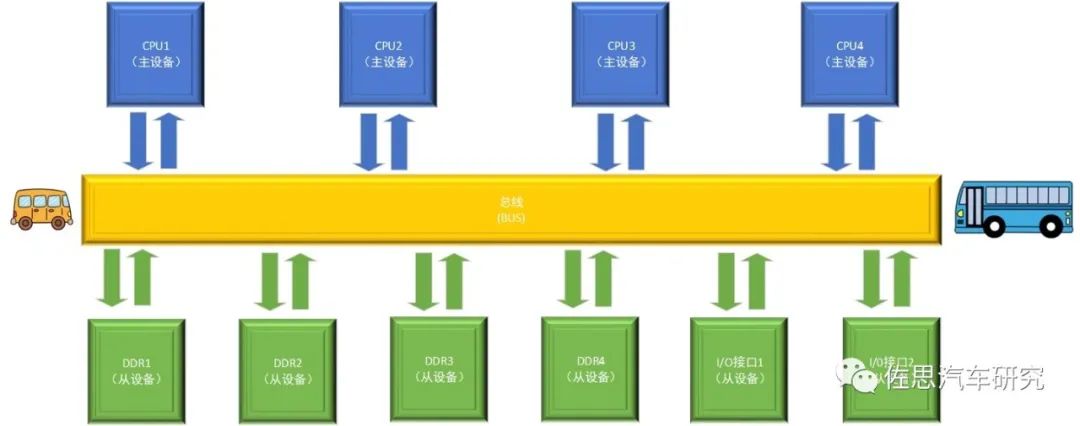

總線最早是源于計算機系統的一個專業術語,是計算機各功能部件之間傳送信息的公共通信干線。在芯片系統中也把連接芯片中各個組件的公共線路稱為總線。總線由地址線(傳送地址信息)、數據線(傳送數據信息)以及控制線(傳送控制信息)三類組成。在傳輸過程中發起請求的一方稱為主設備,返回響應一方稱為從設備。以CPU訪問DDR為例,當CPU發起讀訪問時,總線將讀請求和讀地址發送到DDR控制器,DDR的控制器收到讀請求后,根據讀地址將DDR中對應的數據取出并送到總線處,總線再將數據送到CPU,此時讀訪問結束;當CPU發起寫訪問時,總線將寫請求、寫地址和寫數據發送到DDR控制器,當DDR完成寫數據的存儲后,發送寫應答到總線處,總線再將其發送給CPU,此時寫訪問結束。

CPU讀寫DDR示意圖

隨著對運算能力(計算速度和計算規模)需求的不斷提高,在單核CPU無法滿足計算需求的情況下,多核CPU計算機系統應運而生。目前的芯片系統中通常會包含多個CPU、DDR和外設,即總線上連接有多個主設備和多個從設備,各個CPU都可以使用總線訪問DDR。總線的英文名稱“BUS”形象地描述各位“乘客”(各個主設備的請求)都可以乘坐“BUS”去往相應的“目的地”(從設備),從設備的響應也可以通過總線返回對應的主設備,此時總線可以理解為共享的信息通路,總線把各個組件需要傳遞的信息運送到相應的目的地。

多路主從設備總線示意圖

Cache的由來 提高CPU運算能力的方式之一就是提高CPU工作頻率,但是單單提高CPU頻率帶來的性能提升是有限的,芯片的系統性能還取決于系統架構、指令結構、信息在各個部件之間的傳送速度以及存儲部件的存取速度等因素,特別是CPU與主存之間的存取速度。如果CPU工作速率高于DDR工作速率,就會造成CPU等待,降低芯片性能,浪費CPU運算能力。 此外如果CPU每次訪問DDR都要經過總線,然而總線上的資源是有限的,CPU之間中會存在競爭關系,從中產生的延時也會浪費CPU的運算能力。因此Cache應運而生,在DDR和CPU之間加入cache,cache使用速度快而容量小的SRAM來搭建,CPU在讀取數據時優先訪問cache,如果cache中有相應的數據,即命中,則從cache中獲取。反之,如果cache中不存在對應的數據,再通過總線訪問DDR。Cache的優點在于既能滿足一部分快速讀寫,又不會增加過多的芯片開銷。

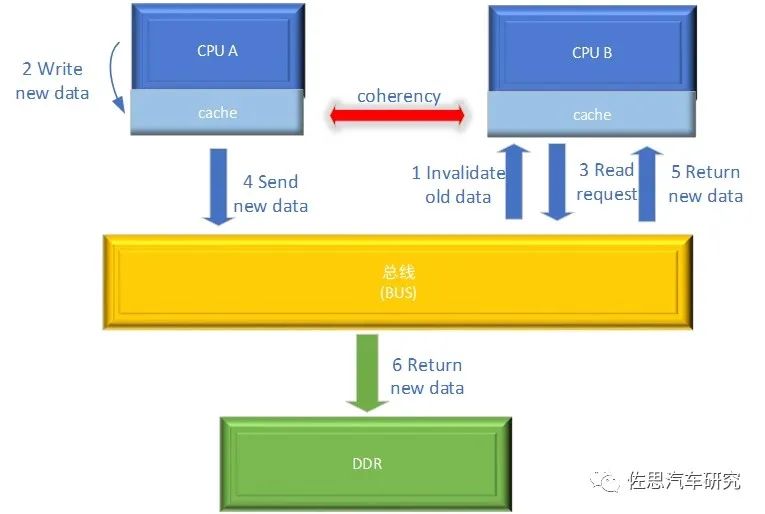

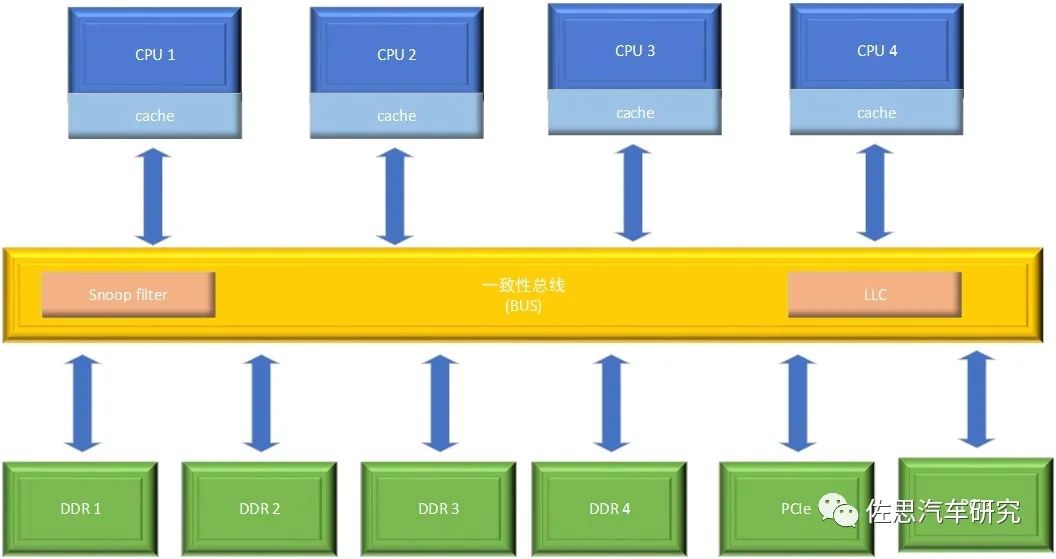

多核處理器系統如何維護cache一致性 在多核處理器系統中引入cache之后,每個CPU都有對應的cache,每個CPU都會對相應的cache進行讀寫操作,由于多個CPU可能對同一地址進行讀寫操作,當某個CPU對共享cache line進行寫操作時,其它CPU的cache中該數據塊的副本將成為過時的數據。如果不及時地通知相應的CPU,將導致錯誤的運行結果。如何保證同一地址的數據在不同cache保持一致成為大家需要考慮的問題。多核處理器系統數據一致性不僅僅涉及各個cache之間的一致性問題,也包含cache和DDR中數據的一致性問題。 我們基于MOESI cache一致性協議假設:CPU A、CPU B以及DDR都保存有同一cache line數據,如果CPU A想要對此cache line中的數據進行改寫,那么總線會先使CPU B中的該 cache line無效,之后CPU A再對其cache line進行改寫,此時DDR中該cache line的數據也成為了舊的不可用數據,如果CPU B需要使用該cache line的數據就需要向總線發起讀請求重新獲取新的數據,總線從CPU A的cache中獲取改寫后的新數據并發送給CPU B的cache;當CPU A和CPU B的cache不再保留該cache line時需要通過總線將其寫回到DDR中。可以看出此時的總線具有管理各CPU cache一致性的功能,被稱為一致性總線(Coherent Bus)。

目前CPU大部分的數據訪問操作都是通過cache完成,不需要和DDR交互,所以cache的出現除了提高CPU訪問數據的效率,又極大的節約了總線帶寬,進而使系統可容納的CPU數目增加。當然,維護cache一致性需要一些額外的總線transaction,這稍稍降低了實際的節約量。

Cache中數據一致性維護示意圖

總線在維護cache一致性時,通知相關cache的操作稱為snoop;snoop操作分為兩種類型:全部通知和精準通知。

全部通知就是通知所有的cache來查詢自身是否有與此操作相關的cache line, 這種做法的缺點是由于共享的cache line畢竟是少數的,所以CPU需要處理很多與自身不相關的snoop請求,從而增加CPU的資源開銷。由于多數snoop都是無效的,因此全部通知也會浪費總線的資源。

精準通知是指總線會記錄各個cache中cache line的信息,當有請求時,先通過snoop filter來篩選出相關的cache并發送snoop。Snoopfilter中記錄了各個cache line的地址信息和狀態信息。目前一致性總線大多采用精準通知的方式,雖然snoop filter增加了總線的資源開銷,但是減少了CPU側的資源開銷,同時也避免總線發送不必要的snoop。

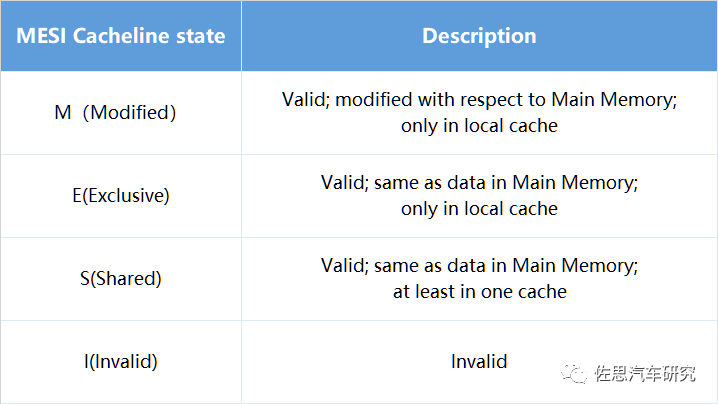

一致性總線通過snoop filter來記錄各個cache中的cache line狀態,在總線的視角中,cache中每個cache line的狀態都在掌握之中。而常用的cache一致性協議包含兩種:MESI和MOESI。

表:cache一致性協議之MESI協議

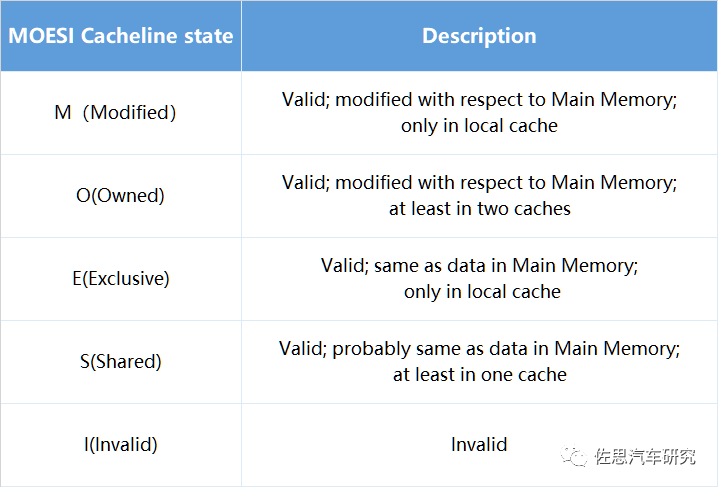

MESI協議的不便之處在于:假設CPUA有個一個M態的cache line,而此時CPU B想獲取此cache line,那么總線必須通知CPU A將cache line同步到主存中。在這個過程中,總線與主存的交互會消耗較長的時間,如果可以在不將數據同步回主存的情況,將CPU A的數據通過總線發送給CPU B,將會節省時間,提高效率。 MOESI協議就優化了這一不便之處。MOESI協議允許cache之間共享dirtycache line。Dirty是指cache line相對于主存而言已經發生變化,這樣就可以節省與主存交互的時間成本,在cache line不需要寫回主存之前,一直在cache之間傳輸。 MOESI相較于MESI多一個O態,O態代表該cache line與主存中的值不同,至少存在于兩個cache中,并由該cache在需要的時刻將cache line刷新到主存中。此外MESI和MOESI的S態有所不同,MESI的S態中的cache line與主存保持一致;而MOESI的S態中的cache line不一定與主存保持一致,可能是共享了dirty cache line,但是沒有向主存刷新cache line的義務。

表:cache一致性協議之MOESI協議

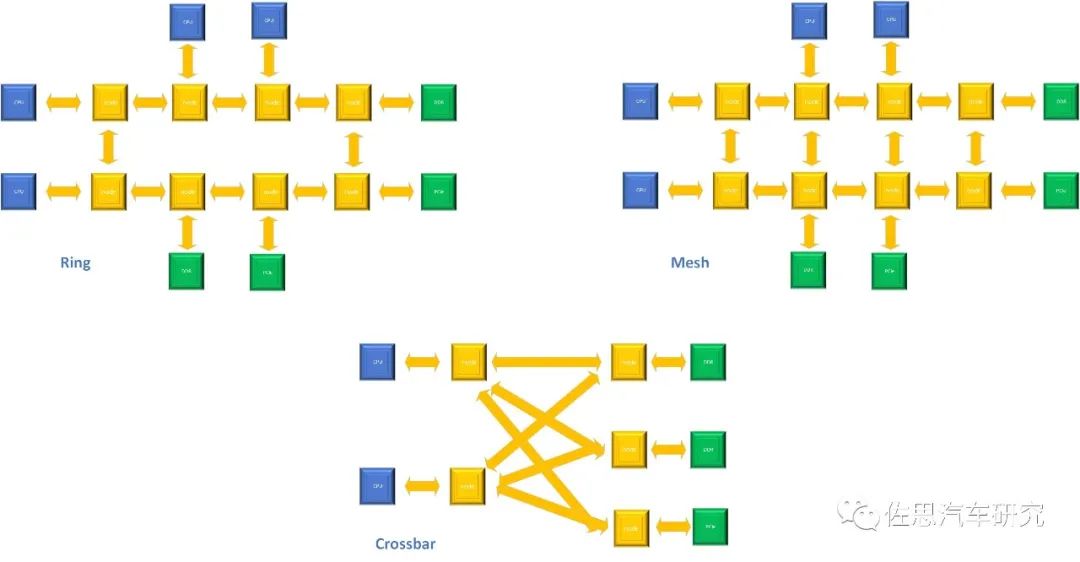

目前常采用CHI協議來實現一致性總線上各個組件的通信,該協議就是采用了MOESI來管理相應的cache line 狀態。CHI靈活用于設計基于一致性總線的芯片系統,支持構建小型、中型或大型芯片系統。系統包含多個組件,從CPU、GPU、DDR到外設接口,以及互連本身。 CHI協議只定義了網絡中不同組件,但是沒有規定使用何種方式來連接組件。一致性總線設計者可以根據PPA(Performance/Power/Area)需求靈活定義拓撲結構。拓撲結構包含以下三類:

環形拓撲(Ring)。在環中,每個組件直接連接到其他兩個組件,形成一個環狀網絡結構,所有組件可以在環中相互通信。這種拓撲的缺點是,延遲隨著環中組件的數量線性增加。這是因為相關事務只能一直沿著環形網絡傳輸,直到抵達目的地。因此,環形拓撲最適合于中型系統。

網格拓撲(Mesh)。與環相比,網格包含了更多的到達目的地的路徑,因此減少了相關事務的訪問時間。這在系統中提供了更高的帶寬,同時也是以犧牲更多的面積為代價。網狀拓撲結構最適合于大規模系統。

交叉連接(Crossbar)。這種拓撲允許每個節點連接到每個可能的節點。這種設計提供了最好的性能,因為每個組件都與需要通信的組件有直接連接。這種拓撲的缺點是連接所有組件的需要很大的資源開銷。這是因為每增加一個組件,系統中所需的信號線數量都會顯著增加。因此,拓撲最適合于小型系統。

拓撲結構示意圖

為了提高CPU存取數據的速率,通常會在一致性總線上加入一級cache,也就是LLC(Last Level Cache)。LLC是一個獨占cache,是低于CPUcache的一級cache,用于緩存從總線中經過的cacheline,它增加了芯片上總cache容量。當總線無法從CPU的cache中獲取需要的數據時,可以先查詢LLC是否含有對應的數據,如果命中,就可以在不訪問主存或外設的情況下,為CPU提供數據。這種多級cache結構有效減少了芯片訪問主存或外設的次數,為高性能CPU提供了相應數據搬運能力。

一致性總線示意圖 結語 一致性總線的出現有效提升了芯片系統內部數據交流的效率,保證了處理器可以及時獲取有效數據,使得高性能處理器可以得到更好的發揮,起到了加速芯片系統運行的作用。隨著車載芯片的不斷發展,一致性總線會得到更加廣泛的應用。

審核編輯 :李倩

-

soc

+關注

關注

40文章

4576瀏覽量

229164 -

核心技術

+關注

關注

4文章

625瀏覽量

20497 -

總線

+關注

關注

10文章

3040瀏覽量

91667 -

芯片系統

+關注

關注

0文章

16瀏覽量

15970

原文標題:總線一致性:高性能SoC核心技術

文章出處:【微信號:zuosiqiche,微信公眾號:佐思汽車研究】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

是德科技推出全新GDDR7發射端一致性測試解決方案

聚焦一致性:鋰電池分選技術的革新者與推動者

比斯特通用分選機四線制測試技術保障電芯性能一致性

以太網一致性測試全解析:保障高性能網絡的關鍵技術

儲能電池一致性,已成核心競爭力

比斯特1810B自動分選機實現電池性能一致性的保障設備

電纜組件相位一致性的意義

請教大家一下DP一致性測試問題

直播回顧 | 深度解讀CAN總線一致性測試的四大層級與實戰方法,虹科技術直播助您破解汽車通信穩定性的關鍵

鏡頭不一致的問題原因分析

堆焊熔池輪廓實時監控,實現工藝穩定性與焊縫一致性

多核處理器系統如何維護cache一致性

多核處理器系統如何維護cache一致性

評論