前面很早就寫出了版圖中WPE、LOD效應的推文: IC后端物理效應--Well Proximity Effect(阱臨近效應) 長文--IC后端物理效應--LOD Effect(擴散區(qū)長度效應)| LOD與OSE的關系 可是PSE卻久久沒有發(fā)出來,為什么呢?因為涉及到的內(nèi)容比較多,包含大學學到的固體物理、半導體工藝以及應變硅工藝的內(nèi)容(這個在大學的時候貌似沒有學過,因為絲毫沒有印象,查了查資料研究了一下)。

PSE(Poly spacing effect)的內(nèi)容應該很多人都知道,也就是Poly的間距對器件的性能會產(chǎn)生影響。

如何在后端版圖上或者布局布線中降低PSE的影響有些人應該也知道,比如在Std cell版圖中可以看到器件兩側(cè)有Dummy Poly的存在,另外在標準單元的兩側(cè)或者標準單元與Macro的交界處需要加一些End Cap。

但是具體為什么PSE會對器件的性能產(chǎn)生影響可能懂的人就不多了,或者大家的理解可能和我之前的理解一樣就是簡單的認為:如果旁邊沒有Dummy Poly或者End Cap那么Core邊界的器件兩側(cè)的環(huán)境就不一樣了,加工出來之后可能和Core中心的器件在物理尺寸或者其他方面有些不一樣,從而會影響器件的性能。

真的是這樣么?是不是太簡單了呢?

后來查閱資料發(fā)現(xiàn),前面的理解或者說猜測貌似是不對的。畢竟我們的版圖中也會添加一堆的Base Filler,里面就包含Dummy Poly,那為什么還專門在外圍添加一些End Cap呢,這肯定說明有一些物理效應或者加工工藝只有引入End Cap才會避免,而引入Dummy Poly Filler是無法解決這種問題的。

那么PSE的真正原因是什么呢?下面根據(jù)我查閱資料的結(jié)果談下我的理解,如有疑問大家可以在公眾號下方探討哦,畢竟我不是做器件出身的。

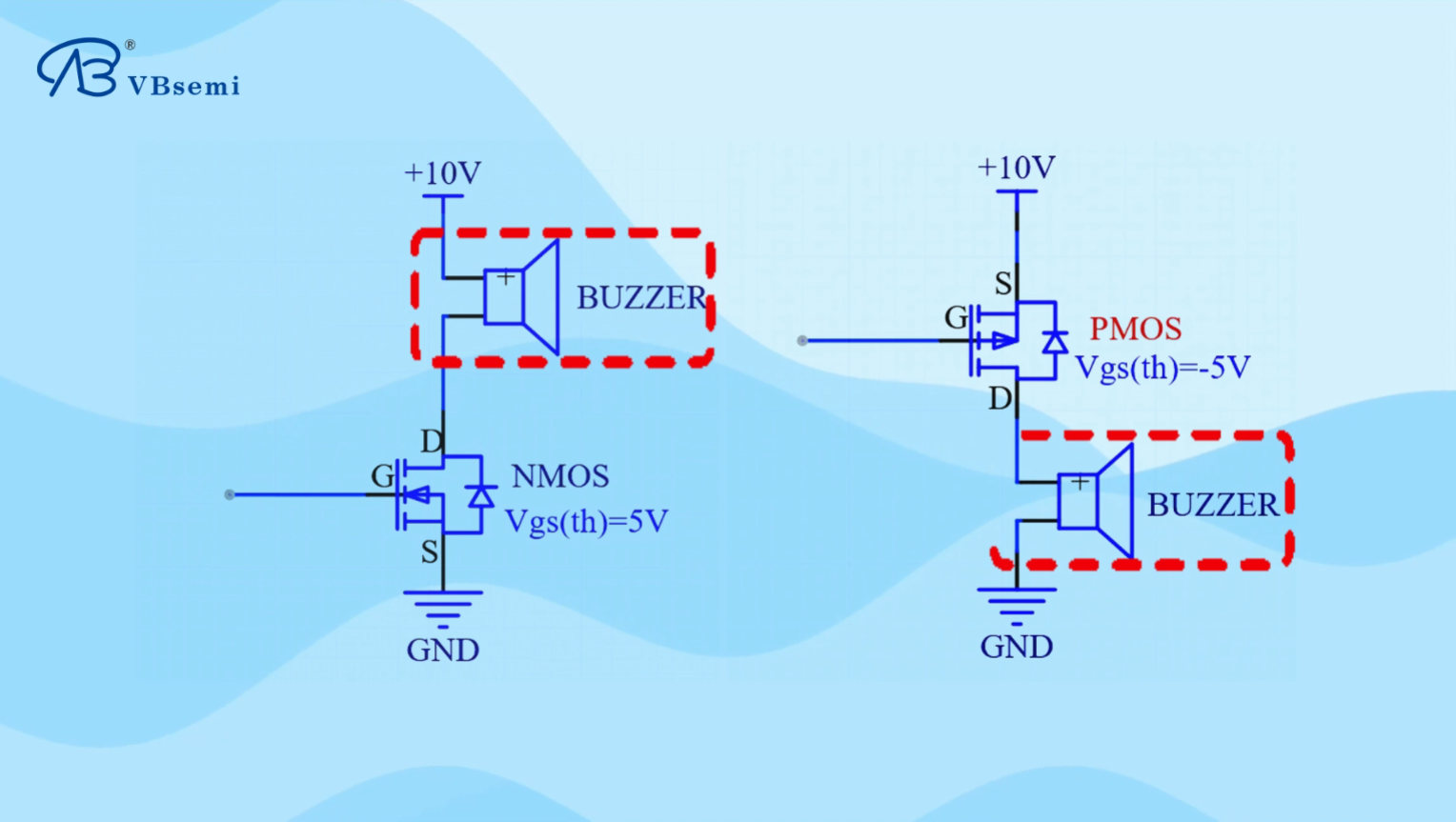

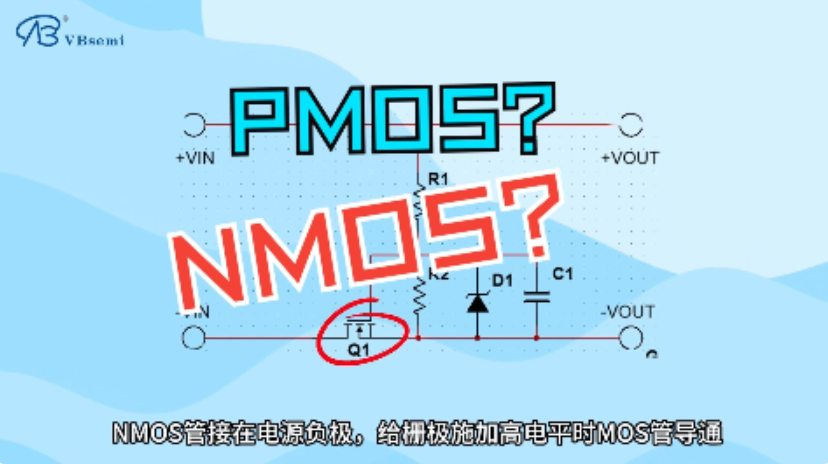

PMOS和NMOS的尺寸比

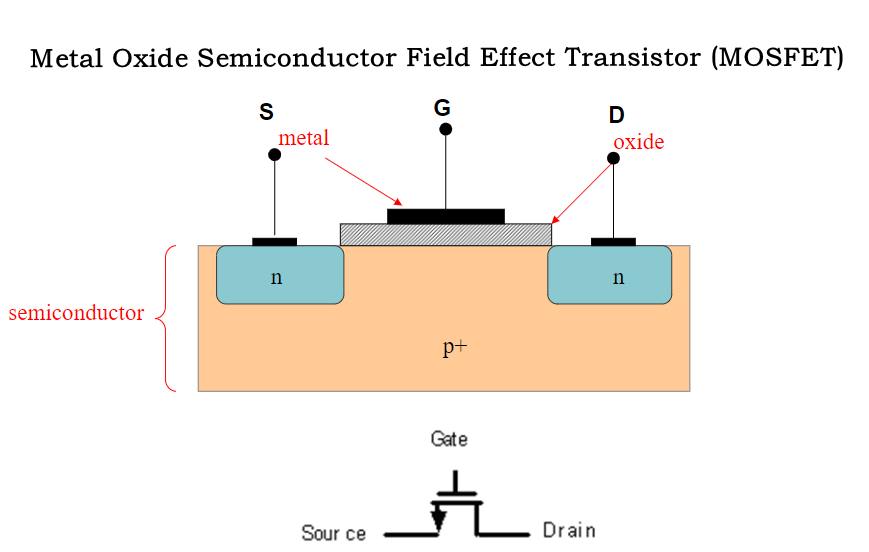

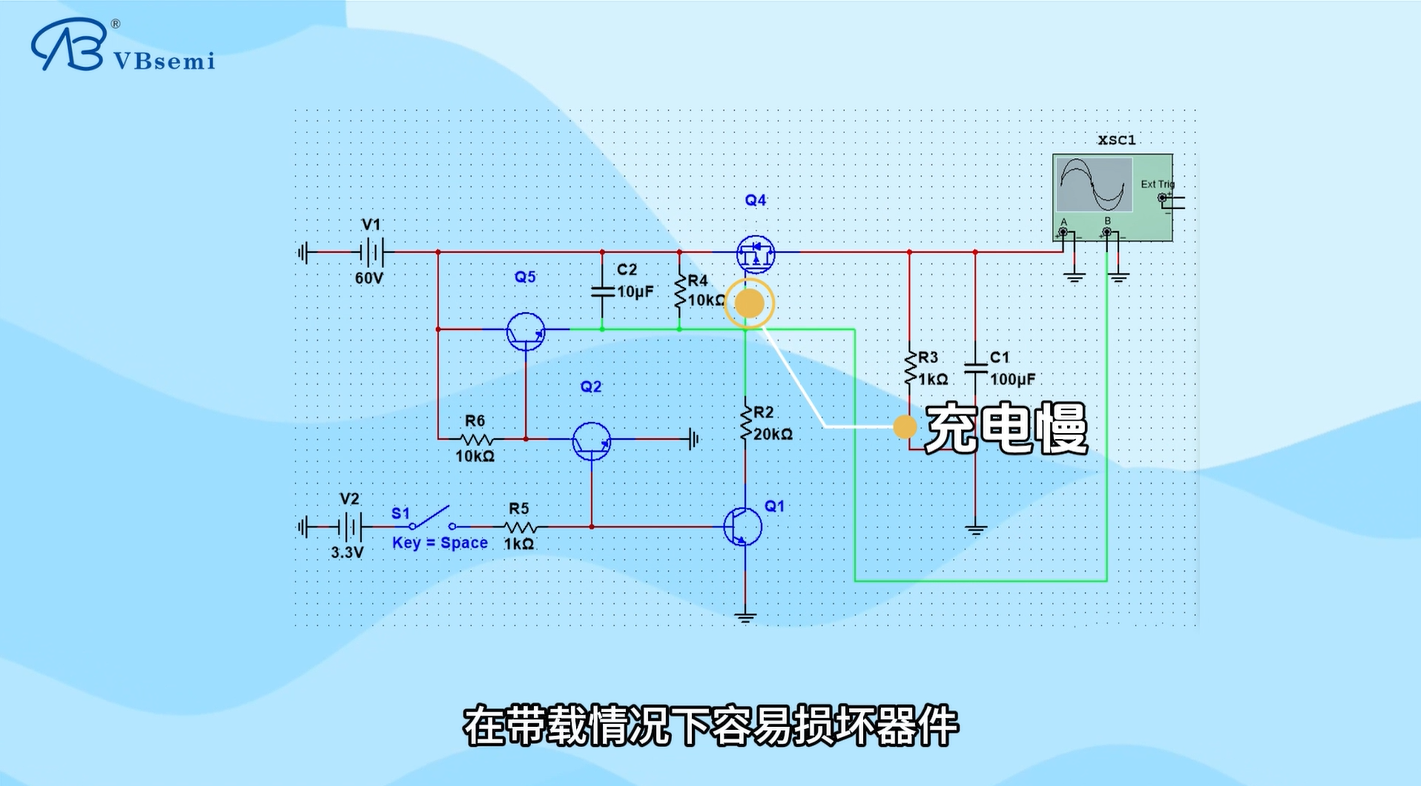

另外,在開始講解之前還得提一下另外一個現(xiàn)象,因為這個與本推文要講解的內(nèi)容也非常相關。在學校的時候我們都知道,PMOS中的空穴遷移率比NMOS中電子的遷移率低,所以為了實現(xiàn)相同的電流輸出,我們需要將PMOS的寬度做的是NMOS寬度的2~3倍。可是在先進工藝下,這種要求已經(jīng)沒有了,兩種MOS的尺寸是一樣的,這是為什么呢?

這和前面講解的STI stress效應以及本節(jié)要介紹的內(nèi)容也息息相關。

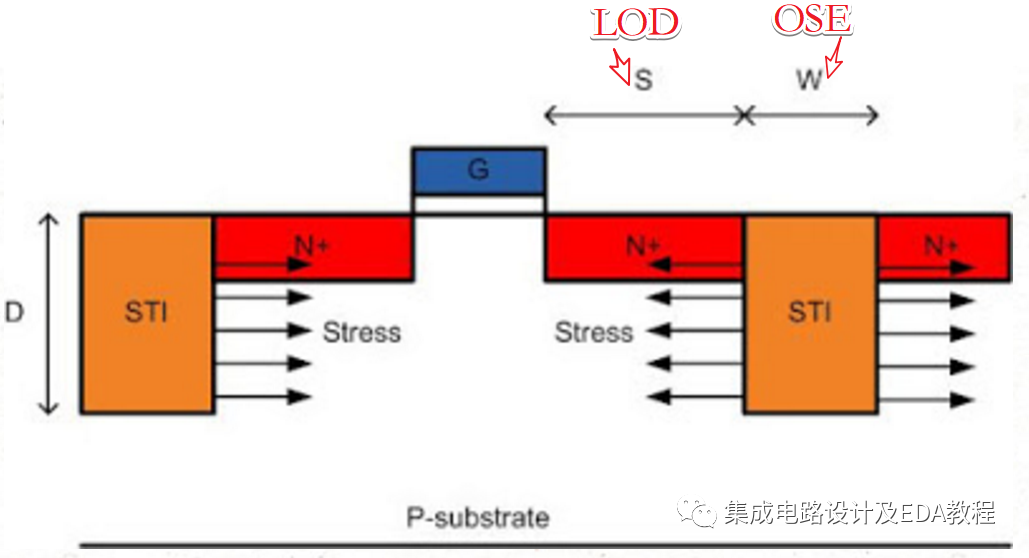

LOD以及OSE效應回顧

在講解PSE之前,先回顧一下LOD以及OSE效應,因為它和下面要講解的PSE有關系。

器件的性能會受到OD長度以及STI寬度的影響,兩者其實都是STI應力引起的效應。

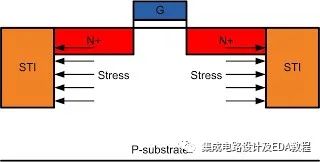

STI會對兩側(cè)的器件產(chǎn)生“壓應力,Compress stress”使得OD的長度發(fā)生變化(縮短):

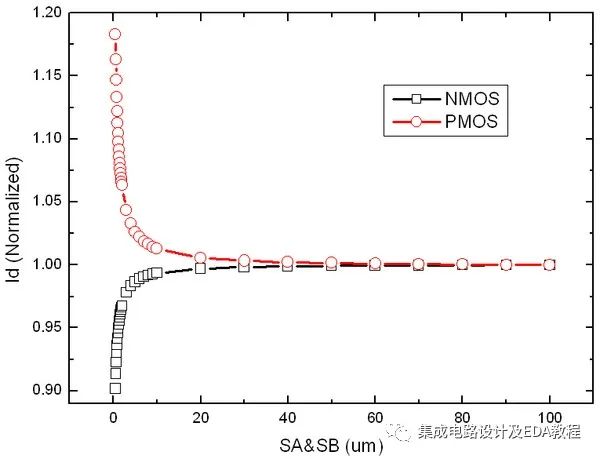

如下圖所示為PMOS和NMOS的電流(性能)隨OD長度變化的曲線,橫坐標為OD的長度SA(SB),縱坐標是電流的大小:

從圖中可以得到如下結(jié)論: 隨著LOD以及OSE效應的增強,PMOS的電流(性能)會提升,NMOS的電流(性能)會下降。這對于PMOS的性能是有好處的,可是對于NMOS的性能則是不利的。 根據(jù)前面的STI stress effect我們可以猜測,如果在器件的OD上面施加一個向外的拉應力(Tensile stress),那么作用將會和上面相反,PMOS的電流(性能)會下降,NMOS的電流(性能)會提升。這對于PMOS的性能是不利的,可是對于NMOS的性能則是有幫助的。

因此,其實為了提高電路的性能,我們更希望在PMOS上施加一個壓應力(Compress stress),在NMOS上施加一個拉應力(Tensile stress)。

應變硅工藝應力引入機制 于是有人就想到,可以利用上面這種物理效應來提升器件的性能。

在器件上面引入應力的有兩種方法:

1、在PMOS源漏下內(nèi)嵌(embedded)一層SiGe(鍺硅)來產(chǎn)生壓應力,這種也被稱為eSiGe (Embedded SiGe)。原因:襯底致雙軸應力引入機制。

2、在器件上加一層CESL(接觸刻蝕停止層,比如SiN)來產(chǎn)生額外的拉/壓應力。

原因:CESL致單軸應力引入機制。

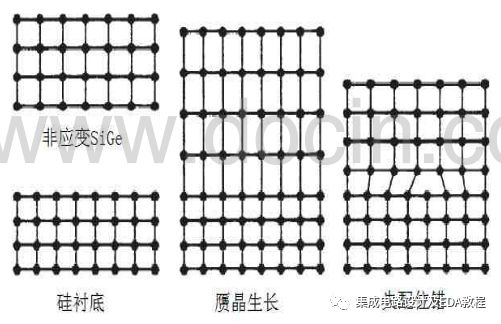

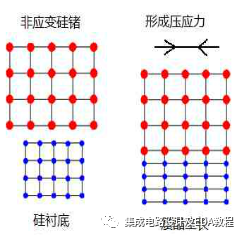

1、鍺硅工藝引入的壓應力 當鍺硅(SiGe)合金生在在Si襯底上時,由于Ge的晶格常數(shù)比Si大,所以其生長平面上的晶格常數(shù)會減小以適應Si襯底的晶格常數(shù),由此會形成贋晶生長,另外贋晶生長會在SiGe上施加一個壓應力。晶格失配程度會隨Ge組分的增加而隨之加深,當超出一定厚度之后會形成大量的失配位錯釋放應力,如下圖所示:

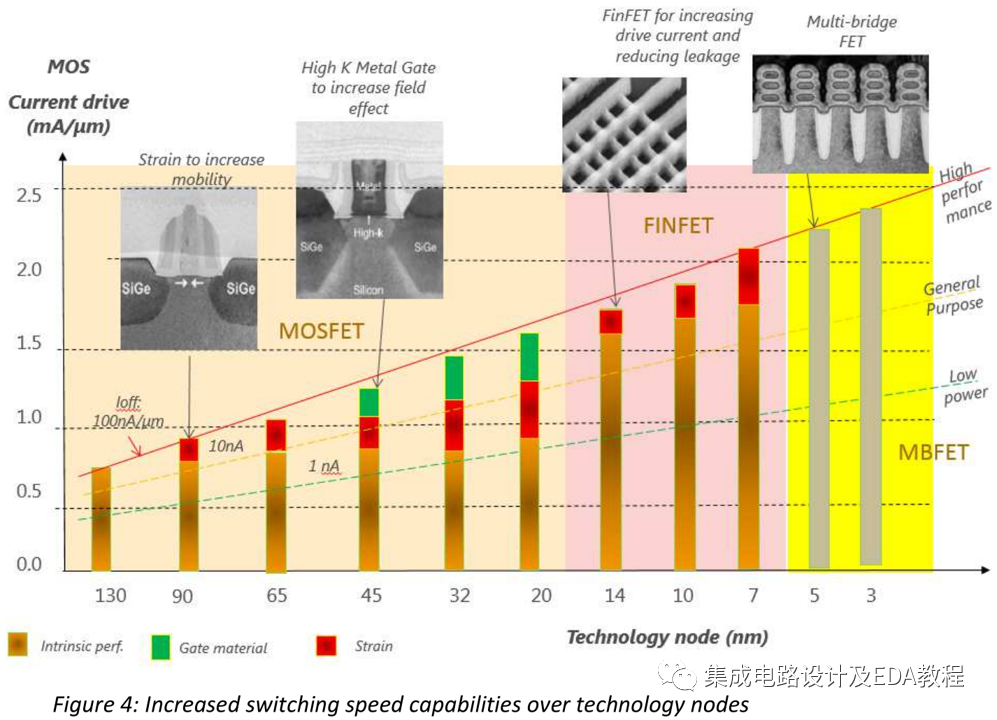

引入的應力會使得PMOS中空穴的遷移率增加(具體原因很復雜,其中一個原因來自于空穴有效質(zhì)量的減小)。對于長溝道鍺硅PMOS而言,與傳統(tǒng)體硅PMOS相比,遷移率可以提高至少50%。 這種技術以及后邊要講的另一種應力引入機制廣泛使用在90nm及以后的工藝下(在5nm及以下工藝下可能不會采用了),如下圖所示(strain工藝):

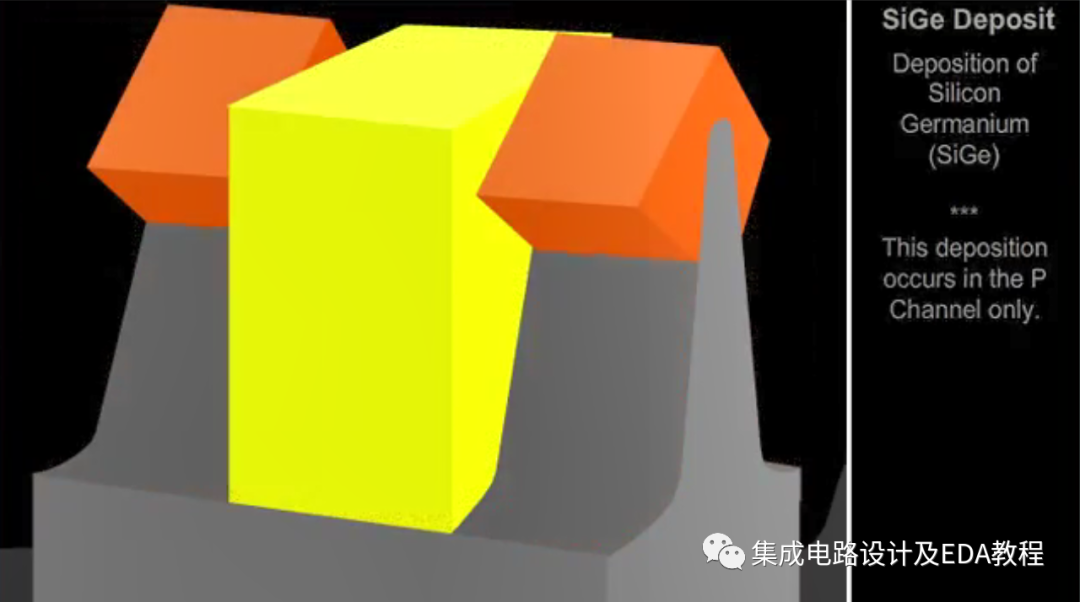

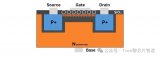

如下圖所示為FinFET工藝下PMOS源漏端淀積的SiGe示意圖:

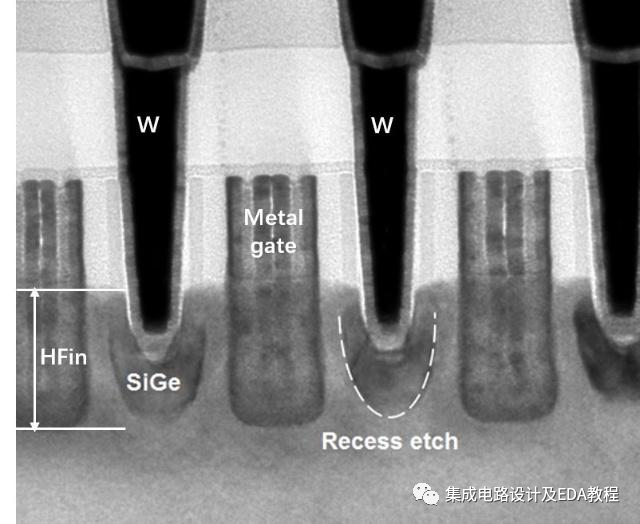

下圖是實際芯片的截面圖,從中可以看到源漏端的SiGe:

另外,工藝上采用這種技術后,PMOS的性能也會受到Metal Gate與OD邊界的距離也就是Length of Diffusion(LOD)的影響,這個可能是LOD效應的另一個原因。

審核編輯:劉清

-

NMOS

+關注

關注

3文章

401瀏覽量

36773 -

PMOS

+關注

關注

4文章

271瀏覽量

31567 -

PSE

+關注

關注

0文章

67瀏覽量

23905

原文標題:Poly Space Effect (PSE)效應 應變硅工藝 eSiGe CESL LOD OSE EndCap相關

文章出處:【微信號:集成電路設計及EDA教程,微信公眾號:集成電路設計及EDA教程】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

PMOS 和 NMOS 的區(qū)別及其在實際應用中的選擇

HG012N06X替代NCE6050KA 60V 50A增強型功率NMOS

一文詳解NMOS與PMOS晶體管的區(qū)別

BDR6200電機驅(qū)動芯片中文手冊

BDR6200半橋驅(qū)動器英文手冊

NMOS在充電樁上的應用

DCDC BUCK通過加RC Snubber解決EMI輻射超標的仿真和實測數(shù)據(jù)分析

PMOS做防倒灌和設想的不一樣是哪里出了問題呢?

MOS管選型的問題

PMOS和NMOS的尺寸比

PMOS和NMOS的尺寸比

評論