電子發(fā)燒友網(wǎng)報(bào)道(文/周凱揚(yáng))對(duì)于高效的數(shù)據(jù)并行負(fù)載處理來說,矢量架構(gòu)的吸引力越來越大,主流ISA都開始注意到這一點(diǎn)。就拿我們熟悉的前超算王者——日本的富岳來說,其處理器富士通A64FX就是基于Arm可伸縮矢量擴(kuò)展(SVE)的。

Arm也在隨后推出的Armv9架構(gòu)中提出了改良版的SVE2,并在其中加入了對(duì)NEON的兼容,SVE2在HPC之外的市場(chǎng)應(yīng)用中做出了指令優(yōu)化,甚至可以用于手機(jī)、汽車等智能設(shè)備中。

正是因?yàn)橛辛薙VE的存在,富岳才得以單靠通用處理器完成高性能的大數(shù)據(jù)運(yùn)算,而不是像其他主流超算一樣,還要靠堆積GPU、FPGA和AI加速器等片外加速器才能實(shí)現(xiàn)可觀的性能,我國(guó)的神威太湖之光同樣運(yùn)用了這樣的矢量設(shè)計(jì)思路。但以上這些都是專有架構(gòu),微架構(gòu)不透明的同時(shí)也限制了開源和定制化方案的出現(xiàn),而這些均可以在RISC-V上一一實(shí)現(xiàn)。

RISC-V矢量處理器的吸引力

RISC-V的矢量擴(kuò)展RVV自2015年提出以來,已經(jīng)有了長(zhǎng)足的進(jìn)展,也有了正式的1.0版本規(guī)范。與傳統(tǒng)的SIMD指令相比,RVV提供動(dòng)態(tài)的矢量長(zhǎng)度修改,做到了更高的效率、更小的代碼體積和更簡(jiǎn)單的循環(huán)結(jié)束。我們近期已經(jīng)看到了不少RISC-V處理器被廣泛使用的新聞,比如谷歌選擇在其TPU上加入SiFive的X280處理器,其實(shí)看重的就是它在矢量處理上的優(yōu)勢(shì)。

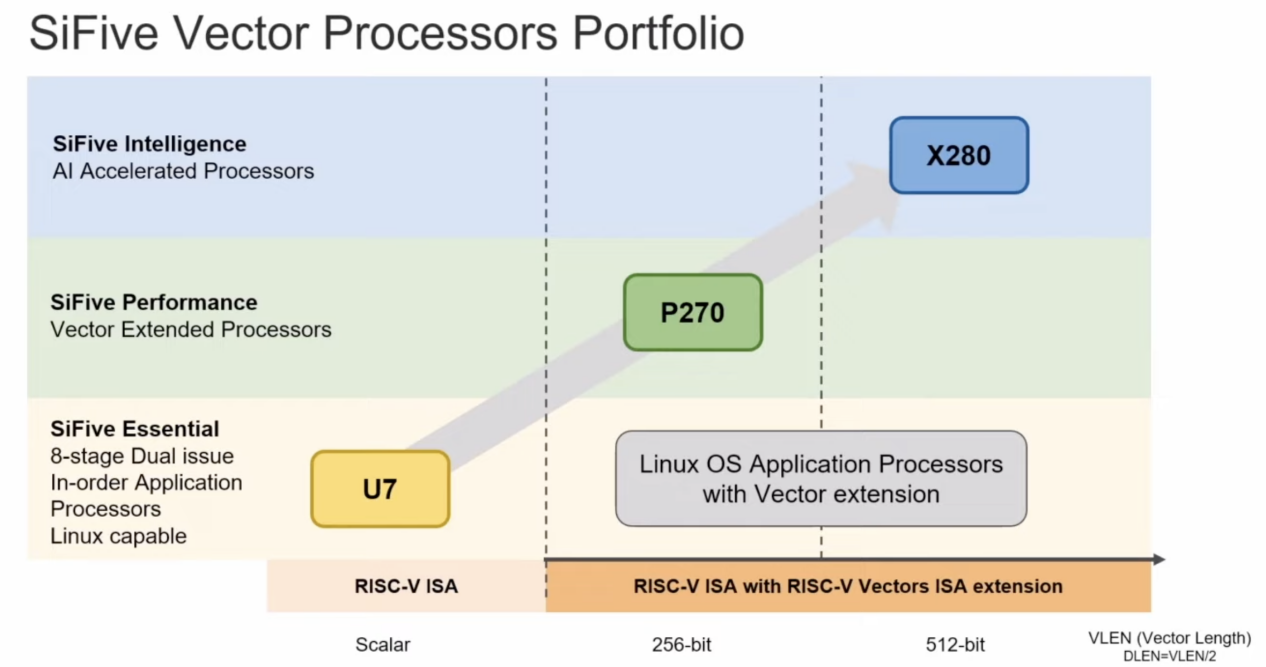

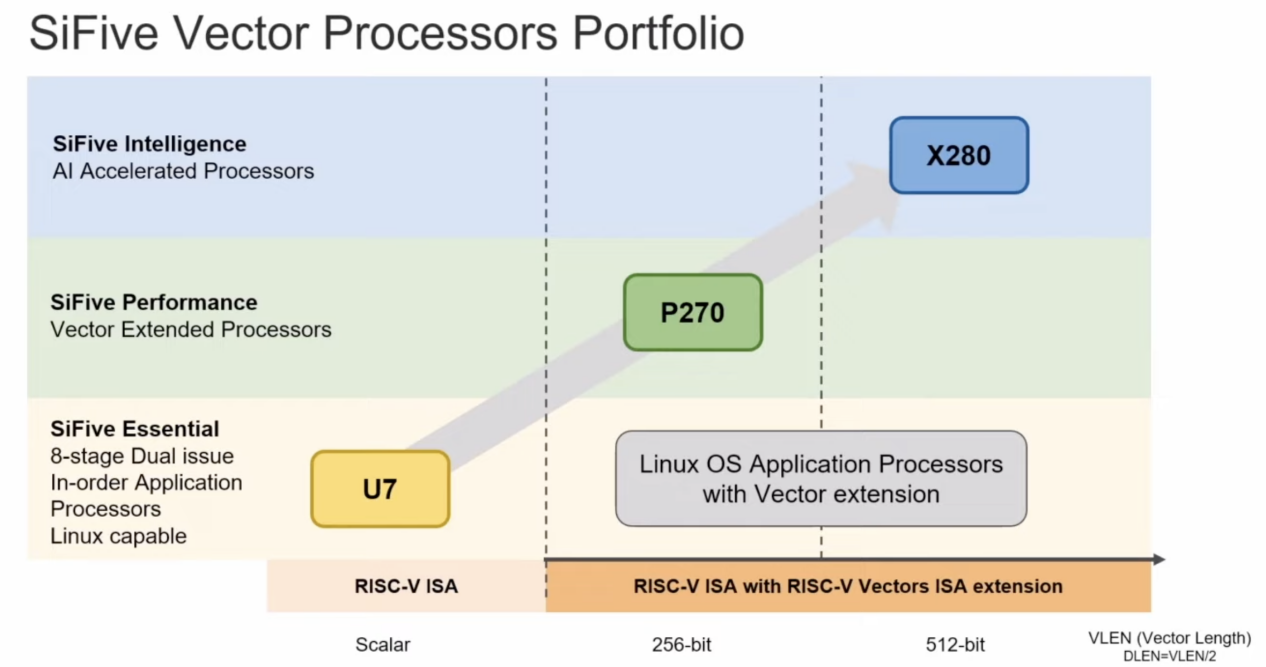

SiFive矢量處理器 / SiFive

所以我們看到在SiFive的處理器產(chǎn)品中,像Performance P270和Intelligence X280都擁有優(yōu)秀的矢量處理能力,后者更是引入了一個(gè)512位矢量寄存器長(zhǎng)度的架構(gòu),在完全支持矢量擴(kuò)展標(biāo)準(zhǔn)的同時(shí),還支持動(dòng)態(tài)可變矢量長(zhǎng)度的運(yùn)算。SiFive也在其矢量擴(kuò)展上做出了改進(jìn),稱其為SiFive智能擴(kuò)展,與直接基于RV64GCV架構(gòu)的設(shè)計(jì)相比,X280的智能擴(kuò)展在INT8格式下的矩陣乘法運(yùn)算時(shí)可將執(zhí)行速度提高12倍。

而且這不僅僅造福的是數(shù)據(jù)中心,還有受制于功耗卻又需要高吞吐量和單線程性能的邊緣應(yīng)用,比如AR/VR、數(shù)碼相機(jī)等等。SiFive同樣測(cè)試了可用于移動(dòng)端或嵌入式設(shè)備的輕量級(jí)神經(jīng)網(wǎng)絡(luò)MobileNet,相較基于RISC-V標(biāo)量的架構(gòu),SiFive智能擴(kuò)展可以將速度提升144倍。

同樣的還有晶心科技推出的RISC-V矢量處理器NX27V,該處理器采用了5級(jí)流水線的設(shè)計(jì),晶心為其設(shè)計(jì)了強(qiáng)大的矢量處理單元,擁有32個(gè)矢量寄存器,最高支持512位的矢量長(zhǎng)度,為了進(jìn)一步支持AI應(yīng)用,晶心還為其增加了BF16和INT4的數(shù)據(jù)格式支持。據(jù)正在打造可擴(kuò)展的高性能AI超算的初創(chuàng)公司Luminous Computing透露,他們打造的系統(tǒng)用到了數(shù)百個(gè)NX27V VPU核心,極大地提升了該系統(tǒng)的深度學(xué)習(xí)性能。

開源RISC-V矢量處理器

RISC-V作為開源架構(gòu)最棒的一點(diǎn)就在于,總是不缺香山處理器這樣優(yōu)秀的開源方案。比如2019年推出的Ara就是一款高效矢量協(xié)處理器,用于輔助OpenHW的CVA6 RISC-V應(yīng)用處理器Ara,只不過Ara剛發(fā)布之際還是基于早期的RVV規(guī)范設(shè)計(jì)的。

來自蘇黎世聯(lián)邦理工學(xué)院(ETH)和華為蘇黎世研究中心的研究員們借助Ara的啟發(fā),基于RVV1.0發(fā)表了一個(gè)開源的高效RISC-V矢量處理器設(shè)計(jì)。他們基于格芯的22FDX工藝進(jìn)行了吞吐量和PPA的驗(yàn)證,整個(gè)系統(tǒng)運(yùn)行頻率為1.34GH,在關(guān)鍵的矩陣乘法內(nèi)核下,F(xiàn)PU的利用率可以達(dá)到98%以上。

相較之下,SiFive的X280和另一個(gè)開源矢量協(xié)處理器Vicuna宣稱的FPU利用率大于90%,伯克利的開源方案Hwacha可以做到95%以上。為了展示從RVV擴(kuò)展這么多年以來的改進(jìn),他們也與基于RVV 0.5版下的設(shè)計(jì)做了對(duì)比,結(jié)果是在面積占用上有了15%的提升,吞吐量也有了6%的提升,雙精度計(jì)算效率也做到了37.1GFLOPS/W。

結(jié)語(yǔ)

AI時(shí)代下,矢量處理的應(yīng)用場(chǎng)景已經(jīng)遠(yuǎn)超我們的現(xiàn)象,包括深度學(xué)習(xí)、推薦系統(tǒng)、鍵值存儲(chǔ)和HPC等,都已經(jīng)廣泛利用了矢量計(jì)算。但如何做到高效高性能,才是未來所有ISA的努力方向,而RISC-V作為后來者,反而能在這上面找到彎道超車的機(jī)會(huì)。

Arm也在隨后推出的Armv9架構(gòu)中提出了改良版的SVE2,并在其中加入了對(duì)NEON的兼容,SVE2在HPC之外的市場(chǎng)應(yīng)用中做出了指令優(yōu)化,甚至可以用于手機(jī)、汽車等智能設(shè)備中。

正是因?yàn)橛辛薙VE的存在,富岳才得以單靠通用處理器完成高性能的大數(shù)據(jù)運(yùn)算,而不是像其他主流超算一樣,還要靠堆積GPU、FPGA和AI加速器等片外加速器才能實(shí)現(xiàn)可觀的性能,我國(guó)的神威太湖之光同樣運(yùn)用了這樣的矢量設(shè)計(jì)思路。但以上這些都是專有架構(gòu),微架構(gòu)不透明的同時(shí)也限制了開源和定制化方案的出現(xiàn),而這些均可以在RISC-V上一一實(shí)現(xiàn)。

RISC-V矢量處理器的吸引力

RISC-V的矢量擴(kuò)展RVV自2015年提出以來,已經(jīng)有了長(zhǎng)足的進(jìn)展,也有了正式的1.0版本規(guī)范。與傳統(tǒng)的SIMD指令相比,RVV提供動(dòng)態(tài)的矢量長(zhǎng)度修改,做到了更高的效率、更小的代碼體積和更簡(jiǎn)單的循環(huán)結(jié)束。我們近期已經(jīng)看到了不少RISC-V處理器被廣泛使用的新聞,比如谷歌選擇在其TPU上加入SiFive的X280處理器,其實(shí)看重的就是它在矢量處理上的優(yōu)勢(shì)。

SiFive矢量處理器 / SiFive

而且這不僅僅造福的是數(shù)據(jù)中心,還有受制于功耗卻又需要高吞吐量和單線程性能的邊緣應(yīng)用,比如AR/VR、數(shù)碼相機(jī)等等。SiFive同樣測(cè)試了可用于移動(dòng)端或嵌入式設(shè)備的輕量級(jí)神經(jīng)網(wǎng)絡(luò)MobileNet,相較基于RISC-V標(biāo)量的架構(gòu),SiFive智能擴(kuò)展可以將速度提升144倍。

同樣的還有晶心科技推出的RISC-V矢量處理器NX27V,該處理器采用了5級(jí)流水線的設(shè)計(jì),晶心為其設(shè)計(jì)了強(qiáng)大的矢量處理單元,擁有32個(gè)矢量寄存器,最高支持512位的矢量長(zhǎng)度,為了進(jìn)一步支持AI應(yīng)用,晶心還為其增加了BF16和INT4的數(shù)據(jù)格式支持。據(jù)正在打造可擴(kuò)展的高性能AI超算的初創(chuàng)公司Luminous Computing透露,他們打造的系統(tǒng)用到了數(shù)百個(gè)NX27V VPU核心,極大地提升了該系統(tǒng)的深度學(xué)習(xí)性能。

開源RISC-V矢量處理器

RISC-V作為開源架構(gòu)最棒的一點(diǎn)就在于,總是不缺香山處理器這樣優(yōu)秀的開源方案。比如2019年推出的Ara就是一款高效矢量協(xié)處理器,用于輔助OpenHW的CVA6 RISC-V應(yīng)用處理器Ara,只不過Ara剛發(fā)布之際還是基于早期的RVV規(guī)范設(shè)計(jì)的。

來自蘇黎世聯(lián)邦理工學(xué)院(ETH)和華為蘇黎世研究中心的研究員們借助Ara的啟發(fā),基于RVV1.0發(fā)表了一個(gè)開源的高效RISC-V矢量處理器設(shè)計(jì)。他們基于格芯的22FDX工藝進(jìn)行了吞吐量和PPA的驗(yàn)證,整個(gè)系統(tǒng)運(yùn)行頻率為1.34GH,在關(guān)鍵的矩陣乘法內(nèi)核下,F(xiàn)PU的利用率可以達(dá)到98%以上。

相較之下,SiFive的X280和另一個(gè)開源矢量協(xié)處理器Vicuna宣稱的FPU利用率大于90%,伯克利的開源方案Hwacha可以做到95%以上。為了展示從RVV擴(kuò)展這么多年以來的改進(jìn),他們也與基于RVV 0.5版下的設(shè)計(jì)做了對(duì)比,結(jié)果是在面積占用上有了15%的提升,吞吐量也有了6%的提升,雙精度計(jì)算效率也做到了37.1GFLOPS/W。

結(jié)語(yǔ)

AI時(shí)代下,矢量處理的應(yīng)用場(chǎng)景已經(jīng)遠(yuǎn)超我們的現(xiàn)象,包括深度學(xué)習(xí)、推薦系統(tǒng)、鍵值存儲(chǔ)和HPC等,都已經(jīng)廣泛利用了矢量計(jì)算。但如何做到高效高性能,才是未來所有ISA的努力方向,而RISC-V作為后來者,反而能在這上面找到彎道超車的機(jī)會(huì)。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

RISC-V

+關(guān)注

關(guān)注

48文章

2886瀏覽量

53026

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

RISC-V vs ARM:為什么工業(yè)與邊緣計(jì)算仍然選擇 ARM 架構(gòu)?

完整,占據(jù)工業(yè)與邊緣計(jì)算主流。 既然 RISC-V 看起來更“先進(jìn)”,為什么工業(yè)界和工程項(xiàng)目依然大量選擇 ARM? 本文從 工程實(shí)現(xiàn)、軟件生態(tài)和項(xiàng)目風(fēng)險(xiǎn) 三個(gè)技術(shù)視角,拆解這個(gè)問題。 一、先明確事實(shí):RISC-V 不由任何公司控

RISC-V,正式崛起

編譯自financialcontent全球半導(dǎo)體行業(yè)迎來里程碑式的變革:開源指令集架構(gòu)(ISA)RISC-V已于2026年1月正式占據(jù)全球處理器市場(chǎng)25%的份額。這一里程碑標(biāo)志著x86和Arm長(zhǎng)期雙

Banana Pi BPI-CM6 計(jì)算模塊將 8 核 RISC-V 處理器帶入 CM4 外形尺寸

Banana Pi BPI-CM6是一款緊湊型“計(jì)算模塊”,本質(zhì)上是一塊小型高性能計(jì)算機(jī)板,它采用的是 RISC-V 處理器,而非更常見的 ARM 芯片。其

發(fā)表于 12-20 09:01

重磅合作!Quintauris 聯(lián)手 SiFive,加速 RISC-V 在嵌入式與 AI 領(lǐng)域落地

之后,要打造的是高可靠性、高能效還支持可擴(kuò)展的 RISC-V 設(shè)計(jì)方案。而且合作的核心目標(biāo)特別明確:

讓 RISC-V 處理器在嵌入式、物聯(lián)網(wǎng)、AI 系統(tǒng)里更快普及;

用集成式 IP

發(fā)表于 12-18 12:01

探索RISC-V在機(jī)器人領(lǐng)域的潛力

的硬件配置給人留下了深刻的第一印象:

? 核心處理器: 搭載了進(jìn)迭時(shí)空的K1系列高性能RISC-V處理器,具備強(qiáng)大的通用計(jì)算能力和AI加速特性。

? 內(nèi)存與存儲(chǔ): 板載LPDDR4

發(fā)表于 12-03 14:40

為什么RISC-V是嵌入式應(yīng)用的最佳選擇

最近RISC-V基金會(huì)在社交媒體上發(fā)文,文章說物聯(lián)網(wǎng)和嵌入式系統(tǒng)正在迅速發(fā)展,需要更高的計(jì)算性能、更低的功耗和人工智能。RISC-V是為未來而建的,包括超高效的MCU到高性能應(yīng)用處理器

大灣區(qū)RISC-V生態(tài)全景展示:RISC-V生態(tài)發(fā)展論壇、開發(fā)者Workshop和生態(tài)應(yīng)用專區(qū)

繼7月份上海的RISC-V中國(guó)峰會(huì)之后,中國(guó)RISC-V生態(tài)和產(chǎn)業(yè)發(fā)展最新動(dòng)態(tài)將在10月份深圳的灣芯展上全景展示。 ? RISC-V,這個(gè)以開放、簡(jiǎn)約、模塊化重塑處理器架構(gòu)格局的開源指

奕斯偉計(jì)算亮相2025 RISC-V中國(guó)峰會(huì)

國(guó)際交流合作。奕斯偉計(jì)算高級(jí)副總裁、首席技術(shù)官何寧博士在主論壇發(fā)表《產(chǎn)業(yè)賦能:RISC-V場(chǎng)景化方案創(chuàng)新與生態(tài)協(xié)同》主題演講,闡述了奕斯偉計(jì)算在RISC-V場(chǎng)景化應(yīng)用與生態(tài)建設(shè)上的戰(zhàn)略

知合計(jì)算:RISC-V架構(gòu)創(chuàng)新,阿基米德系列劍指高性能計(jì)算

在2025 RISC-V中國(guó)峰會(huì)上,知合計(jì)算處理器設(shè)計(jì)總監(jiān)劉暢就高性能RISC-V處理器架構(gòu)探索與實(shí)踐進(jìn)行了精彩分享。 在以X86和ARM為

RISC-V 工具鏈的版本更新、開發(fā)動(dòng)態(tài)及生態(tài)建設(shè)愿景

架構(gòu)能否突破 “硬件強(qiáng)、軟件弱” 的瓶頸,真正成為具有競(jìng)爭(zhēng)力的通用計(jì)算架構(gòu)。 ? 2025 年 7 月 18 日,在第五屆(2025)RISC-V 中國(guó)峰會(huì)的軟件與生態(tài)系統(tǒng)分論壇上,SiFive

發(fā)表于 07-18 11:08

?4985次閱讀

RISC-V International CEO:RISC-V 應(yīng)用全面開花,2031 年滲透率將達(dá) 25.7%

and RISC-V Adoption in 2025》。 ? 當(dāng)前,RISC-V 的成功已從嵌入式計(jì)算領(lǐng)域加速向存儲(chǔ)技術(shù)與高性能計(jì)算(HPC)領(lǐng)域滲透,展現(xiàn)出跨行業(yè)的顛覆性潛力。A

發(fā)表于 07-17 10:28

?3700次閱讀

RISC-V和ARM有何區(qū)別?

在微處理器架構(gòu)領(lǐng)域,ARM與RISC-V是兩個(gè)備受關(guān)注的體系。ZLG致遠(yuǎn)電子在推出ARM核心版后,又推出了基于RISC-V的MR6450核心版,這引發(fā)了人們對(duì)這兩種架構(gòu)差異的深入探討。ARM

HPM5E31IGN單核 32 位 RISC-V 處理器

HPM5E31IGN單核 32 位 RISC-V 處理器在當(dāng)今嵌入式系統(tǒng)領(lǐng)域,RISC-V架構(gòu)正以開源、靈活和高性價(jià)比的優(yōu)勢(shì)快速崛起。HPM5E31IGN作為先楫半導(dǎo)體的一款單核32位RISC

發(fā)表于 05-29 09:23

FPGA與RISC-V淺談

全球半導(dǎo)體產(chǎn)業(yè)競(jìng)爭(zhēng)格局正在經(jīng)歷深刻變革,物聯(lián)網(wǎng)、邊緣計(jì)算等新興技術(shù)的蓬勃發(fā)展,讓RISC-V憑借其開源、精簡(jiǎn)以及模塊化的靈活優(yōu)勢(shì),日益成為業(yè)界焦點(diǎn),也為全球半導(dǎo)體產(chǎn)業(yè)注入新的活力與挑戰(zhàn)

發(fā)表于 04-11 13:53

?677次閱讀

思爾芯與玄鐵合作IP評(píng)測(cè),加速RISC-V生態(tài)發(fā)展

的需求,又兼具安全可靠、高性價(jià)比及可拓展性等優(yōu)勢(shì)。在近期的2025玄鐵RISC-V生態(tài)大會(huì)上,玄鐵抓住AI新機(jī)遇,旗下系列處理器不斷推陳出新,進(jìn)一步推動(dòng)了RISC-V

通用計(jì)算仍有差距,RISC-V可靠矢量處理彎道超車

通用計(jì)算仍有差距,RISC-V可靠矢量處理彎道超車

評(píng)論