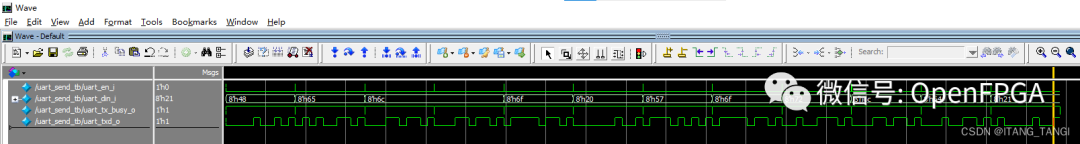

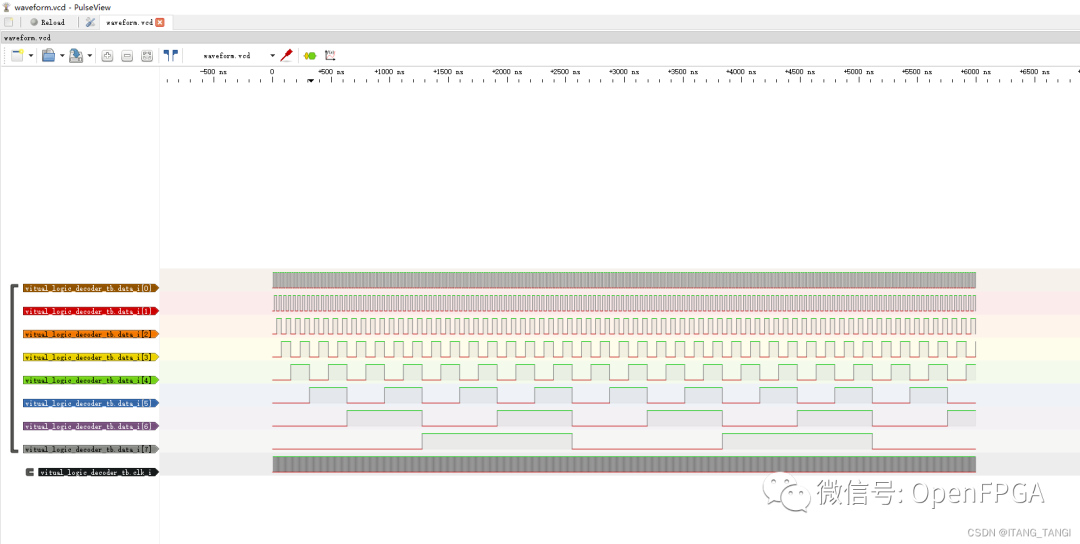

經常使用RTL例如verilog進行數字邏輯設計的朋友,仿真一定是一個繞不開的話題。在一些標準的數字接口和協議上,使用仿真軟件例如modelsim或者vcs進行仿真后,得到的都是波形文件,使用相應的波形查看器查看數字信號的變化以確認協議邏輯設計的正確性,這點一般需要憑借個人豐富的經驗和對協議的充分理解才能保證。可謂是“人腦解碼器”,效率低下且很容易出錯。例如下圖中的串行發送數據不經解碼很難確認正確性。

市面上一些邏輯分析儀配套軟件例如DSview或是pulseview擁有龐大的數字協議解碼器庫,配合邏輯分析儀使用時能夠快速分析設計正確性,但這樣一般又都需要邏輯分析儀硬件設備以及數字邏輯設計的實現載體例如FPGA等,也很不方便。

經過研究,邏輯分析儀軟件例如pulseview能夠通過導入其他格式波形(例如vcd)文件,再對相應通道添加解碼器,即可實現仿真+解碼驗證的全套軟件實現流程,不需要借助硬件進行分析,并且也不需要靠人工去分析協議的正確性,十分方便。

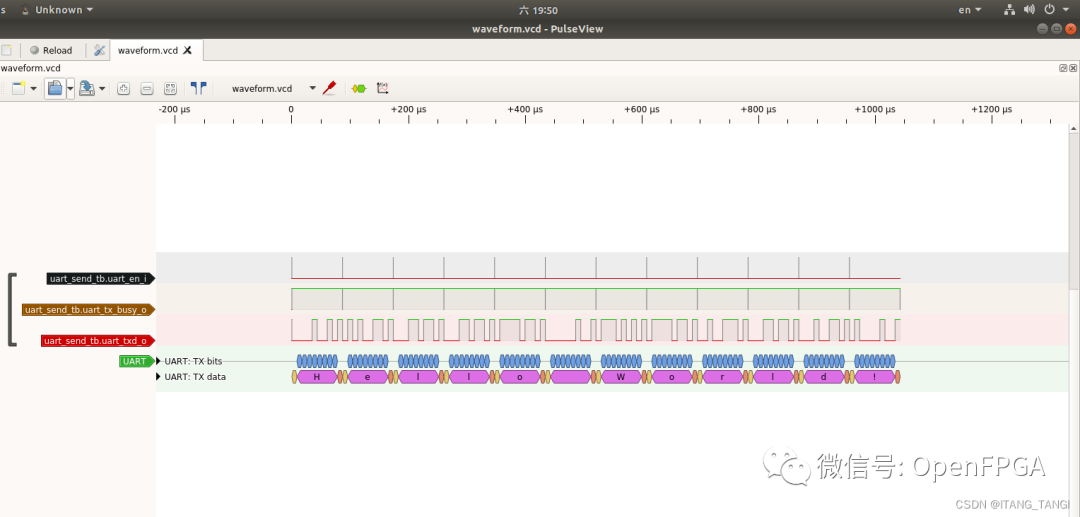

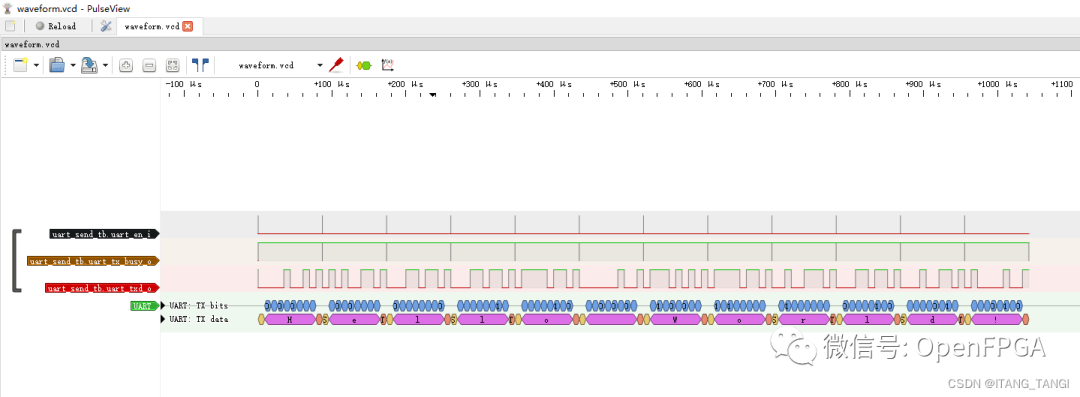

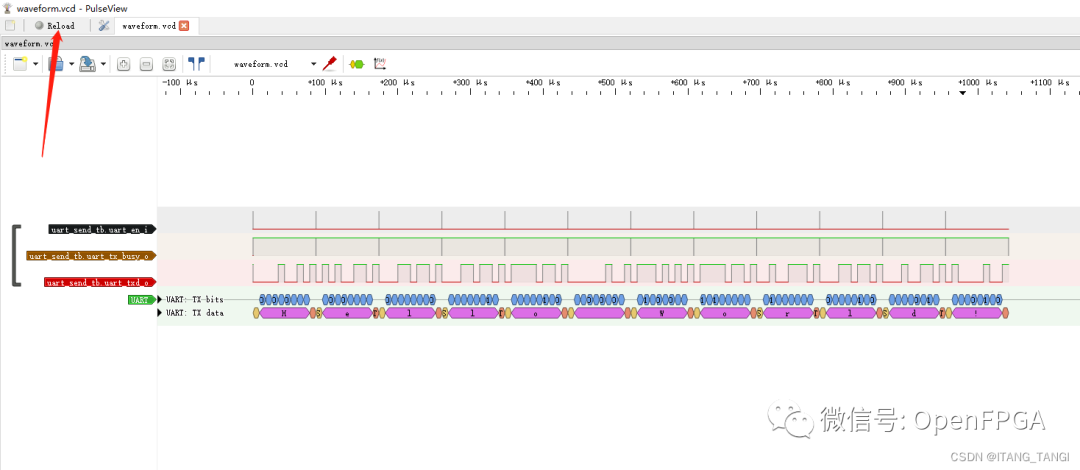

例如上圖中的波形導出vcd文件后由pulseview軟件導入并添加串口解碼器后得到如下圖所示的結果,可以看到串口協議設計正確且發送的數據十分清晰被解碼出來。

軟件和波形文件格式

Pulseview是一款開源的邏輯分析儀軟件,具有十分漂亮的界面和強大的解碼庫,支持Windows,Linus,MacOS等多個平臺,可以通過導入波形文件進行解碼和分析,具體介紹可以查看官方Wiki。

VCD (Value Change Dump)是一個通用的格式。 VCD文件是IEEE1364標準(Verilog HDL語言標準)中定義的一種ASCII文件。它主要包含了頭信息,變量的預定義和變量值的變化信息。正是因為它包含了信號的變化信息,就相當于記錄了整個仿真的信息,我們可以用這個文件來再現仿真,也就能夠顯示波形。

本次的教程即通過邏輯分析儀配套軟件pulseview讀取vcd文件進行解碼。

使用過程

參考Verilog和Testbench設計源碼在github:

https://github.com/ITANGTANGI/verilog_decoder_pulseview

本次教程分為Windows端和Linux端兩個部分。

Windows平臺

軟件安裝

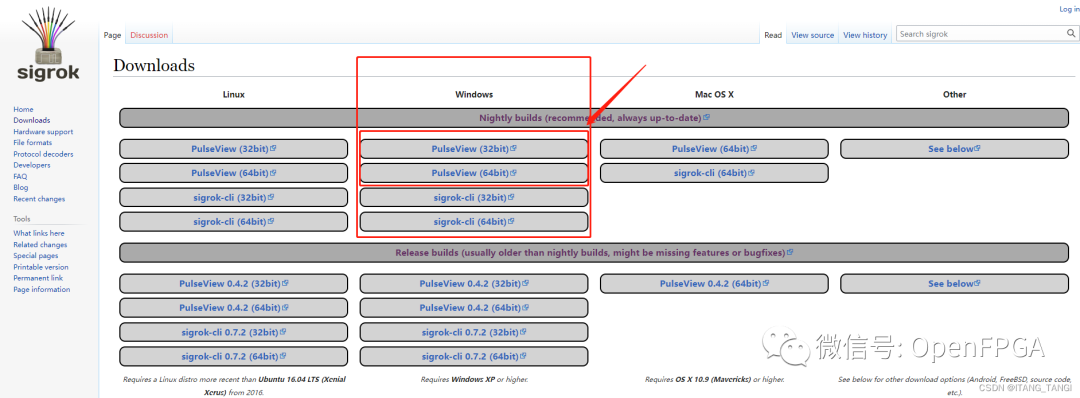

首先到官網

https://sigrok.org/wiki/Downloads

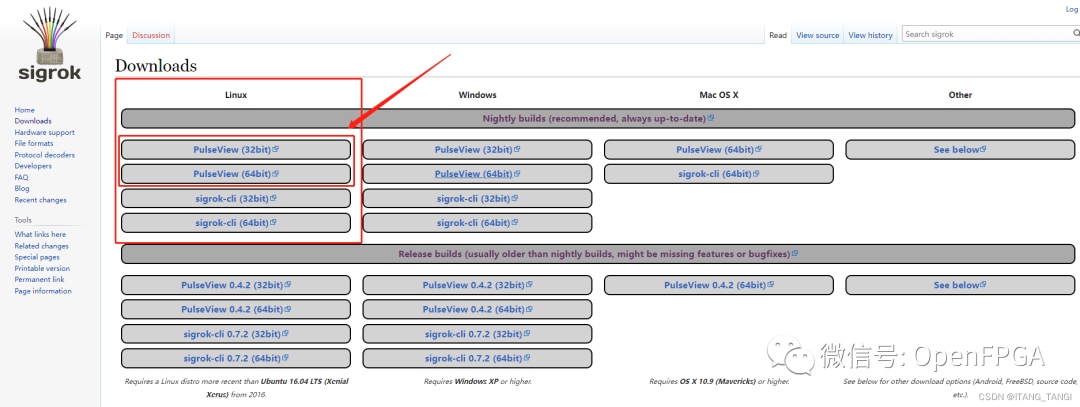

如下圖所示,根據電腦的配置下載Windows安裝包,已經使用過sigrok兼容的邏輯分析儀的話應該電腦中都有pulseview軟件了。

下載完成后雙擊安裝包,按照正常軟件安裝步驟正常安裝即可,沒有啥需要注意的。如下圖所示就是安裝按成了。

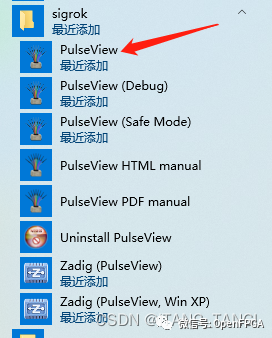

安裝完成后不會生成快捷方式,在“開始”菜單欄中找到如下圖所示的sigrok文件夾中pulseview打開或自行添加快捷方式即可。

至此軟件安裝完成。

vcd波形文件生成

因為VCD是 Verilog HDL語言標準的一部分,因此所有的verilog的仿真器都要能夠實現這個功能,也要允許用戶在verilog代碼中通過系統函數來dump VCD文件。我們可以通過Verilog HDL的系統函數dumpfile來生成波形,通過dumpvars的參數來規定我們抽取仿真中某些特定模塊和信號的數據。

基礎波形生成和導入顯示操作如下例代碼中添加的一個initial塊,里面使用dumpfile生成了waveform.vcd文件,并把clk_i和data_i信號添加進波形文件的變量中。

樣例代碼:

`timescale1ns/1ps

modulevitual_logic_decoder_tb;

//vitual_logic_analyzerParameters

parameterPERIOD=10;

parameterSAMP_CLK_FREQ=100_000_000;

parameterSAMP_CHANNELS=8;

//vitual_logic_analyzerInputs

regclk_i=0;

reg[SAMP_CHANNELS-1:0]data_i=0;

//vitual_logic_analyzerOutputs

initialbegin

$dumpfile("waveform.vcd");

$dumpvars(0,vitual_logic_decoder_tb.clk_i,vitual_logic_decoder_tb.data_i);

end

//dumpfsbl

initialbegin

$fsdbDumpfile("waveform.fsdb");

$fsdbDumpvars(0);

end

//Clockgenerate

initial

begin

forever#(PERIOD/2)clk_i=~clk_i;

end

always@(posedgeclk_i)begin

data_i<=?data_i?+?8'd1;

end

//operations

initial

begin

#6000

$finish;

end

endmodule

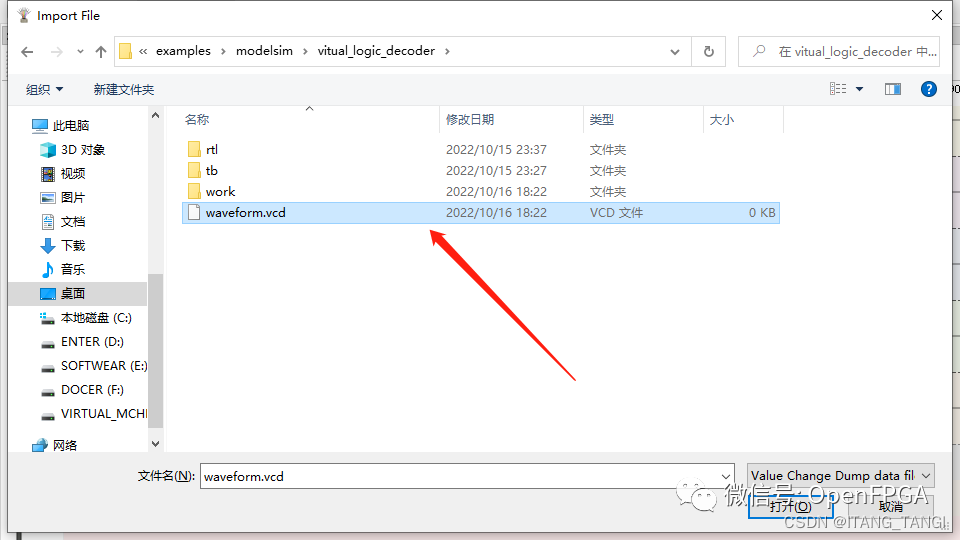

使用Windows下的Verilog仿真軟件,我這里使用的是Modelsim,也可以使用vivado自帶的仿真器或者iverilog等對上述代碼進行仿真。仿真后會在仿真文件夾下生成waveform.vcd文件。Verilog仿真的流程不介紹。

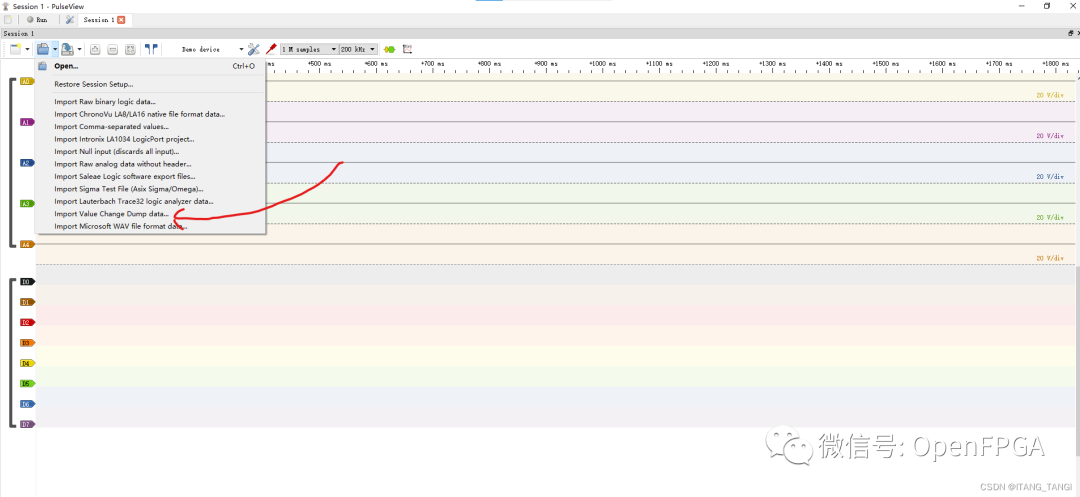

打開pulseview軟件,點擊菜單欄open圖標右側小三角,選擇Import Value Change Dump data選項,界面如下圖所示:

打開生成的vcd文件

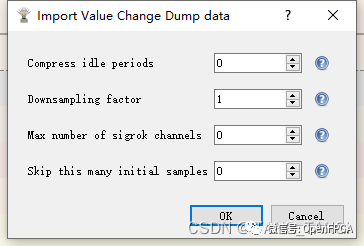

參數設置,可以不用管

點擊OK后,即可成功加載波形

波形解碼

編寫一個串口發送Hello world!字符串的Verilog程序,按照上述方法進行仿真生成vcd文件,使用pulseview加載后如下圖所示。

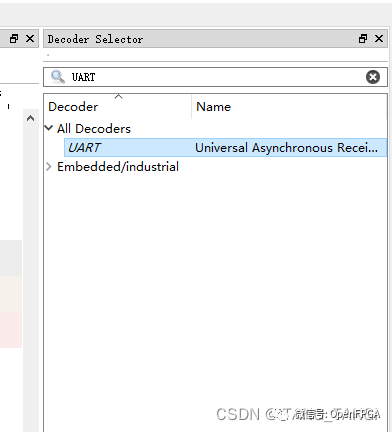

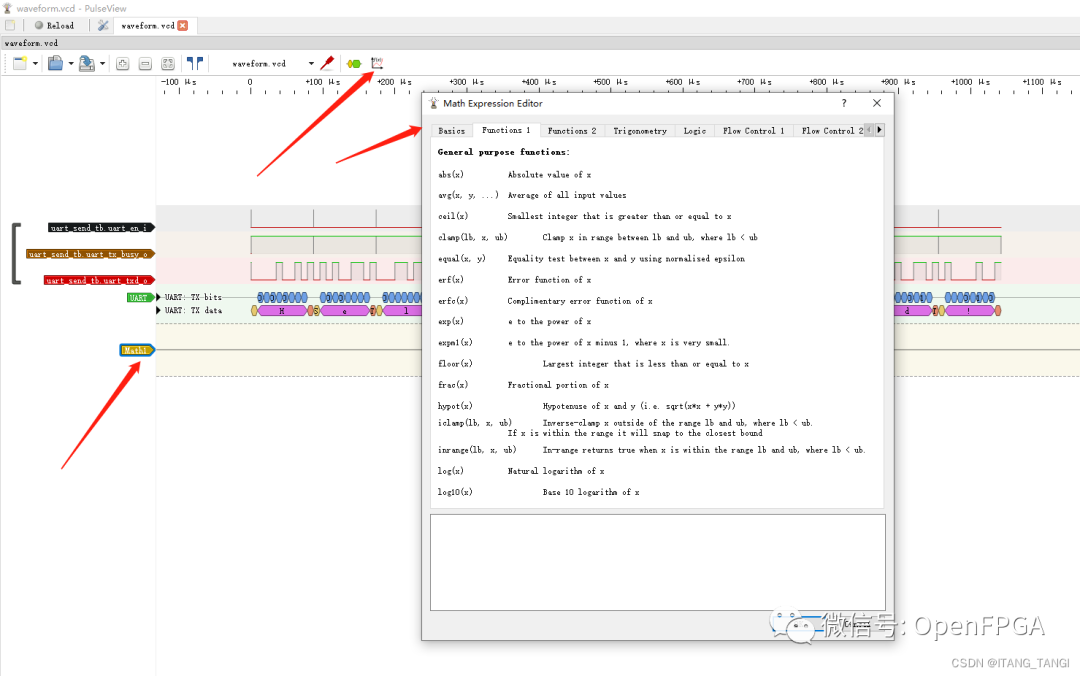

點擊箭頭所指,打開解碼器庫界面,搜索UART,并雙擊UART解碼器添加到波形圖中。

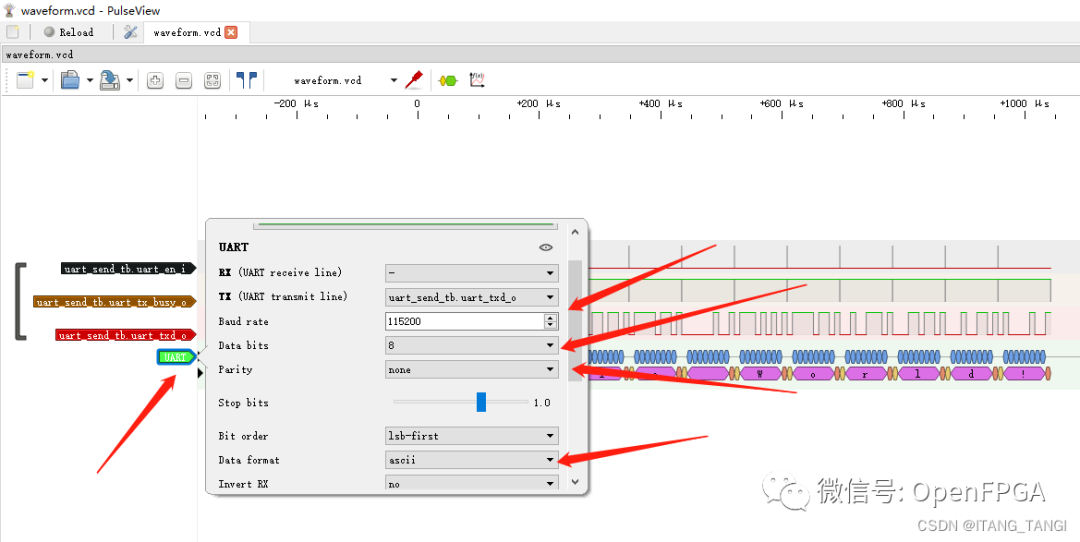

點擊波形圖中的UART解碼器,根據自己的設計選擇需要解碼的通道,設置波特率等參數,選擇數據顯示格式為ASCII,選擇完成后會自動重新解碼。

解碼完成后顯示正確的解碼結果。

其它功能

解碼器按鈕右邊的“Math”按鈕可以支持對通道使用數學表達式進行多種算術邏輯運算,可以實現很多一般數字邏輯設計波形查看器不能實現的功能。

提升解碼性能技巧

在解碼或加載仿真時間單位小或是仿真時間長的vcd波形時,pulseview軟件需要執行比較長的時間,執行時間和CPU性能有關。

可以通過在Testbench設計中的timescale降低仿真精度,或者是減少仿真時間,避免過多的無用波形產生。這方面讀者可以自行發揮。

備注

Windows下Modelsim仿真過程中,仿真器會占用vcd文件導致pulseview無法加載(打開VCD文件時卡死),暫未找到解決辦法。關閉Modelsim軟件再加載vcd波形就行。不知有沒更好解決辦法。

重新仿真后,不需要點擊open按鈕重新打開vcd文件,點擊軟件左上角的reload按鈕即可自動重新加載波形并解碼,無需重新設置。

Linux平臺

軟件安裝

Linux下pulseview軟件無需安裝,到官網

https://sigrok.org/wiki/Downloads

下載Linux的執行文件,用chmod 777 賦予可執行權限后直接運行即可。

仿真,波形顯示和解碼

剩下的操作和Windows平臺相同,只不過是使用的仿真軟件不同而已,參考源碼中給了VCS工程例程。

審核編輯 :李倩

-

解碼器

+關注

關注

9文章

1219瀏覽量

43425 -

仿真

+關注

關注

54文章

4483瀏覽量

138276 -

源碼

+關注

關注

8文章

685瀏覽量

31320

原文標題:使用Pulseview軟件輔助verilog數字設計仿真協議解碼

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

TLV320AIC1x系列單聲道編解碼器:特性、應用與設計要點

TLV320AIC22C:雙VoIP編解碼器的技術剖析與應用指南

深入剖析LM4549B:高性能音頻編解碼器的技術指南

SN74AHC139雙2到4位解碼器/多路分解器深度解析

探秘SN74AHC238:高速硅門CMOS解碼器的設計與應用

SN74ACT238-Q1高速硅門CMOS解碼器:設計與應用全解析

深度剖析TVP5160:高性能數字視頻解碼器的卓越之選

探索TVP5147M1:高性能數字視頻解碼器的深度剖析

基于E203 RISC-V的音頻信號處理系統 -CODEC(音頻編解碼器)配置

增強T-BOX設計,新唐編解碼器的重要作用

0.1-2.7 GHz SP4T 開關,帶集成邏輯解碼器 skyworksinc

0.25 - 2.15 GHz 4x2 開關矩陣,帶音調/電壓解碼器 skyworksinc

4 x 2 開關矩陣,帶音調/電壓解碼器 250 MHz–2.15 GHz skyworksinc

Transformer架構中解碼器的工作流程

pulseview軟件導入并添加串口解碼器

pulseview軟件導入并添加串口解碼器

評論