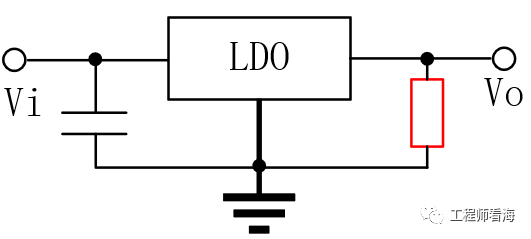

有的同學在看到一些原理圖時,會發現LDO輸出端對地并聯了個電阻,這豈不是會白白消耗功率嗎?為什么要加這個電阻呢?

今天介紹其中的一個原因:

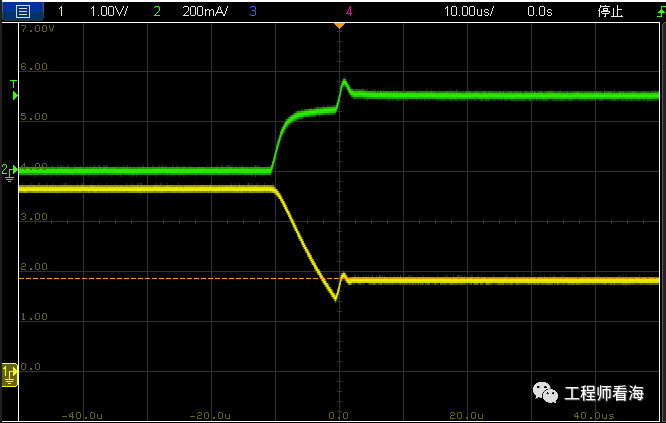

以前在工作中,同事遇到一個問題,LDO輸出接了一個負載,負載有低功耗和普通模式兩種工作模式,低功耗模式時正常,普通模式時工作也正常,但是從低功耗切換到普通模式時,卻發生了異常,測量得到LDO的輸出電壓波形大約如下,綠色是電流波形,黃色是電壓波形,在負載從低電流切換到高電流后,輸出電壓異常,導致負載不能正常工作。

后來分析到是LDO為了進一步降低功耗,當檢測到電流低于一定閾值后,自身也會進入低功耗模式,如果突然從低功耗切換到普通模式時就容易發生異常,可以參考LDO的負載調整率的概念。

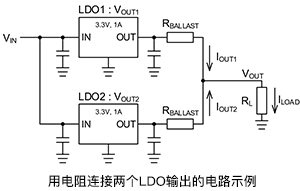

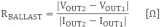

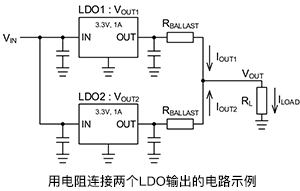

當時的緩解方法是,在LDO輸出端對地并聯一個大電阻,防止LDO進入低功耗模式,以此來規避問題,這個電阻的阻值選擇方法為,LDO輸出電壓除以低功耗切換電流,然后阻值減小一點,比如減低22%,以此保證LDO輸出電流一直高于這個低功耗切換電流閾值。

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

接地電阻

+關注

關注

2文章

292瀏覽量

19324 -

輸出電壓

+關注

關注

2文章

2048瀏覽量

41116 -

LDO穩壓器

+關注

關注

0文章

183瀏覽量

17827

原文標題:LDO輸出為什么并聯接地電阻?

文章出處:【微信號:玩轉單片機與嵌入式,微信公眾號:玩轉單片機與嵌入式】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

為什么運放和ADC的PSRR不能把LDO輸出的內部噪聲抑制的干干凈凈呢?

容專門用來降低LDO的內部噪聲,和反饋電阻R1并聯。

第二種方法測到的數據波動明顯小,說明前饋電容降低LDO內部噪聲比較明顯,但是問題來了,為什么運放和ADC的PSRR不能把

發表于 09-03 07:32

為什么LM8272運放反向端和輸出端要加一個4.7K電阻和0.01UF電容呢?

為了能夠驅動一款ADC的頂參考電壓,用LM8272做個跟隨器.

請教一下,為什么運放反向端和輸出端要加一個4.7K

發表于 09-20 07:55

為什么要加電阻?

1、為什么要加電阻下圖是典型的 MIC 應用電路以及 MIC 內部的電路圖。在 MIC 內部,駐極體電容將聲音信號變為電信號,并立即通過一級共源 FET 放大輸出。

發表于 07-27 08:25

開關電源輸出端并聯電阻作用

開關電源輸出端并聯電阻作用 開關電源是一種常見的電源,它具有高效率、小體積、低發熱等優勢,廣泛應用于電子設備、機器人、航空航天等領域。在開關電源的設計中,

X電容屬于陶瓷電容嗎?X電容兩端為啥要并聯電阻?

X電容屬于陶瓷電容嗎?X電容兩端為啥要并聯電阻?? X電容,也就是X2和X1電容,是一種特殊的陶瓷電容。與普通的陶瓷電容不同的是,X電容能夠在高壓交流電的環境下工作,并且具有防火的特性

LDO輸出端為什么要加這個并聯電阻呢

LDO輸出端為什么要加這個并聯電阻呢

評論