讓我們談談將 RISC-V 整合到工業(yè)產(chǎn)品線開發(fā)流程中。這里的關(guān)鍵信息是,軟件工程師可以更早、更頻繁地進行創(chuàng)新,并為硬件設(shè)計團隊提出更具體的核心要求。如果你曾經(jīng)做過基于 Linux 的設(shè)計,你應該熟悉這個過程,因為有很多相似之處。同時,硬件工程師利用開源 RISC-V 實施,可以在創(chuàng)新和協(xié)作方面領(lǐng)先一步,并參與開放社區(qū)。

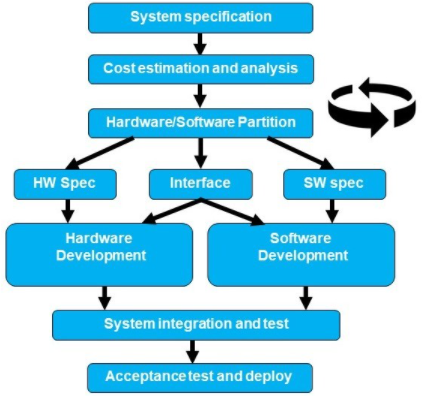

圖1

如圖所示,傳統(tǒng)的硬件/軟件協(xié)同設(shè)計模型在劃分階段后硬件和軟件設(shè)計并行向前發(fā)展。雖然這是“完美世界”的場景,但現(xiàn)實情況是硬件通常驅(qū)動設(shè)計的大部分定義,而軟件則支持硬件定義的內(nèi)容。雖然這種情況多年來有所改善,并且軟件對整體定義的貢獻比過去更大,但它仍然是一個以硬件為主的模型。

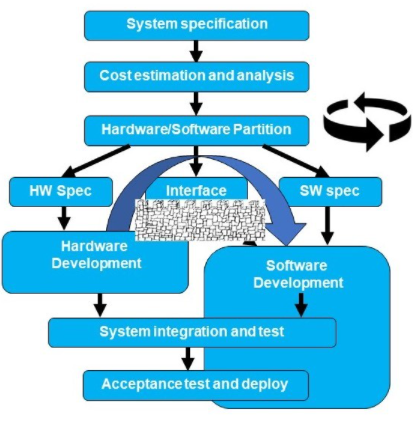

圖 2

像所有模型一樣,最終您必須從概念到實際實施,并且必須以具有成本效益的方式進行。因此,大多數(shù)組織實施產(chǎn)品開發(fā)模型來管理此過程,例如 NXP 顯示的模型,其中硬件和軟件開發(fā)階段大部分與幾個已定義的正式里程碑并行運行。

美中不足的地方在于,硬件和軟件開發(fā)人員通常是從不同的地方裁減出來的。對于每個學科來說,完美的解決方案看起來都非常不同,而性能方面的考慮往往會迫使做出對軟件人員不友好的決策。一種潛在的解決方案是,在做出這些決定時,硬件開發(fā)人員應該考慮如何讓軟件團隊更輕松,即幫助他們利用已知的范例。

在恩智浦,軟件團隊驅(qū)動下一代物聯(lián)網(wǎng)系統(tǒng)的編程模型,這是定義算法和數(shù)據(jù)結(jié)構(gòu)表達的底層計算系統(tǒng)的抽象。這有助于彌合底層硬件架構(gòu)與應用程序開發(fā)人員的軟件支持層之間的差距。它將包括操作系統(tǒng)以及可以通過硬件實現(xiàn)改進的功能,例如低級中斷、內(nèi)存管理和時鐘支持。例如,對于具有連接性的嵌入式處理器,軟件團隊提供與硬件設(shè)計團隊緊密架構(gòu)的 PHY 和 MAC 層堆棧的輸入,以實現(xiàn)高效的 SoC 設(shè)計。

當您查看當前設(shè)計所投入的資源(資源等于人)時,很明顯軟件開始主導嵌入式設(shè)計的成本。因此,軟件團隊需要在決策中擁有更大的發(fā)言權(quán)。

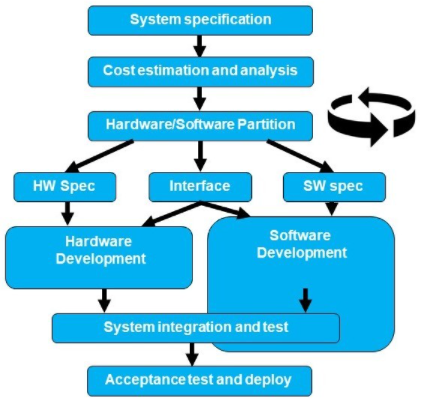

圖 3

圖 3 顯示了一個更現(xiàn)實的設(shè)計流程,其中硬件設(shè)計在軟件之前開始,為軟件團隊提供了一些關(guān)于它需要支持什么的定義。不幸的是,這最終會導致更長的軟件設(shè)計時間。

圖 4

如圖 4 所示,可以通過使用 Zebu 和仿真等快速仿真技術(shù)在流程的早期開始,采用“左移”方法進行軟件開發(fā)。因此,圖 3 中的過程圖已經(jīng)演變,現(xiàn)在顯示軟件開始更早,結(jié)束更早。

RISC-V 編程模型由創(chuàng)建機器抽象視圖的語言和庫組成。關(guān)于控制你需要問的問題是”

并行性是如何產(chǎn)生的?

如何強制執(zhí)行依賴項(排序)?

對于數(shù)據(jù),它是:

數(shù)據(jù)可以共享還是全部私有?

如何訪問共享數(shù)據(jù)或傳輸私有數(shù)據(jù)?

對于同步:

可以使用哪些操作來協(xié)調(diào)并行性?

什么是原子(不可分割)操作?

使用 Chisel 硬件設(shè)計工具等工具和 RISC-V 等開放式 ISA 實現(xiàn),軟件團隊可以在流程的早期開始探索,使用關(guān)鍵軟件算法和應用程序,設(shè)計可以有效執(zhí)行這些關(guān)鍵軟件應用程序的專用 RISC-V 內(nèi)核。 這尤其適用于系統(tǒng)定義和軟件系統(tǒng)建模。

在處理系統(tǒng)定義和軟件系統(tǒng)建模時,軟件工程師使用類似于 C/C++ 程序或 Matlab 模型的模型以及一組性能要求。然后,Chisel 用于設(shè)計探索。

一旦團隊獲得了擴展 RISC-V 架構(gòu)所需的指令,它們就會作為新指令的定義傳遞出去,最終生成編程模型。這就是發(fā)送回硬件團隊進行實施和優(yōu)化的內(nèi)容。

一個重要的問題是 RISC-V 是否可以“足夠開放”以類似于 Linux 模型的方式運行。如果你看看 Linux 的早期以及它是如何開始流行的,那么如果它確實以這種方式發(fā)生,那將是對行業(yè)有利的。在嵌入式領(lǐng)域,Linux 項目的數(shù)量大約增長了 50%。大約 80% 的用戶使用操作系統(tǒng)的免費版本。

RISC-V要取得成功,必須堅持這四個“自由”:

出于任何目的運行軟件的自由。

研究軟件如何工作的自由,并對其進行更改以使其按照您的意愿行事。訪問源代碼是一個先決條件。

重新分發(fā)副本的自由,以便您可以幫助您的鄰居。

將修改后的版本的副本分發(fā)給他人的自由。

關(guān)鍵信息是嵌入式軟件工程師將在定義 SoC 架構(gòu),特別是編程模型和系統(tǒng)優(yōu)化方面發(fā)揮更大的作用。開源 RISC-V 實現(xiàn)將允許更多的軟件驅(qū)動硬件。生態(tài)系統(tǒng)對于 RISC-V 的成功至關(guān)重要。

審核編輯:郭婷

-

soc

+關(guān)注

關(guān)注

40文章

4580瀏覽量

229375 -

Linux

+關(guān)注

關(guān)注

88文章

11778瀏覽量

219175 -

RISC-V

+關(guān)注

關(guān)注

48文章

2901瀏覽量

53153

發(fā)布評論請先 登錄

新思科技VC Formal解決方案在RISC-V驗證中的應用

新思科技ARC-V處理器驅(qū)動RISC-V市場無限機遇

RISC-V B擴展介紹及實現(xiàn)

RISC-V 手冊

2025新思科技RISC-V科技日活動圓滿結(jié)束

RISC-V International CEO:RISC-V 應用全面開花,2031 年滲透率將達 25.7%

芯華章邀您共赴2025 RISC-V中國峰會

IAR邀您共赴2025 RISC-V中國峰會

兆易創(chuàng)新將攜多元解決方案亮相2025 RISC-V中國峰會

deepin社區(qū)邀您相約2025 RISC-V中國峰會

時擎科技邀您參加2025 RISC-V中國峰會

SiFive 上海芯伍科技邀您參加2025 RISC-V中國峰會!

思爾芯邀您共赴2025 RISC-V中國峰會!

沁恒微電子:從互連互通應用推動RISC-V落地發(fā)展

FPGA與RISC-V淺談

將RISC-V放入您的設(shè)計中

將RISC-V放入您的設(shè)計中

評論