將二維材料集成到傳統的半導體制造工藝中可能是芯片行業歷史上更激進的變化之一。

盡管在半導體制造中引入任何新材料都會帶來痛苦和這么,但過渡到金屬二硫屬化物 (TMD:transition metal dichalcogenides) 支持各種新的器件概念,包括BEOL晶體管和單晶體管邏輯門。新的背柵(back-gate )和分柵(split-gate)晶體管已經顯示出二維設計的前景。

一段時間以來,人們已經了解了諸如 MoS 2和 WS 2等 TMD 對晶體管溝道的優勢。隨著器件的縮小,溝道厚度也需要縮小,以最大限度地減少短溝道效應。然而,在硅中,非常薄的層會受到載流子遷移率降低的影響。陷阱( traps )和其他界面缺陷(interface defects)的影響壓倒了體積特性。

相比之下,二維材料沒有平面外懸掛鍵(out-of-plane dangling bonds,),從而減少或消除了界面效應。雖然業界一致認為 3nm 是硅溝道的實際厚度限制,但 MoS 2單層的厚度小于 1nm。

直到最近,接觸電阻還是采用 TMD 的最大障礙。然而,在過去一年左右的時間里,銻和鉍等半金屬已成為潛在的解決方案。半金屬往往不會在半導體帶隙中產生電子態,因為它們本身沒有帶隙,并且它們在費米能級處具有低態密度。

盡管如此,將 TMD 與現有的半導體制造基礎設施集成仍然具有挑戰性。所涉及的許多材料——鉬、硫、銻和鉍等——對行業來說都是新的,可能對現有工藝有害。

制造 TMD 單層

最好的 TMD 單層是通過從塊狀材料上剝離或在藍寶石上進行分子束外延制造的,這兩種方法都需要隨后轉移到傳統晶圓上。雖然它是一種對制造更友好的工藝,但金屬有機化學氣相沉積需要非常高的沉積溫度,并且可以將碳副產物摻入沉積膜中。

在最近的 VLSI 技術研討會上,英特爾的組件研究工程師 Kirby Maxey 和他的同事指出,實際上 TMD 晶體管有兩種不同的用例。一種是在生產線前端( front-end-of-line),它使用 TMD 代替高性能 finFET 或硅納米片晶體管。這種應用依賴于高質量的單晶層,此時需要在 1,000°C 附近的沉積溫度。英特爾小組表明,金屬有機前體物質的熱解會導致碳沉積以及 TMD,但替代前體和優化的工藝條件可以提高薄膜質量。

第二個潛在用例將 TMD 放置在第二(或第三)有源層中,與中間金屬和接觸層垂直堆疊。一旦金屬層在晶圓上,沉積溫度就會受到更多限制。但是這些后端產線(back-end-of-line)晶體管可能更大,并且能夠使用更厚的多晶通道。成功的沉積工藝需要與沉積發生時晶圓上的任何材料兼容。

高度縮放的 FEOL 設備尋求最小化溝道厚度,僅使用單層 TMD 材料。在第二層開始生長之前,第一個成核位點應該合并成一個連續的薄膜。在今年的材料研究學會春季會議上發表的工作中,亞琛工業大學的研究員 Songyao Tang 及其同事分析了 WS 2單分子層的生長和聚結。隨著initial nucleation islands變大,他們發現中心到邊緣的距離超過了吸附原子的遷移距離。當吸附原子無法到達微晶的邊緣時,就會形成雙層。通常,過早的雙層可以覆蓋薄膜總表面積的 30%。

亞琛工業大學小組確定了幾種減少雙層形成的方法。如果每個單獨的微晶都更小,那么吸附原子就不需要走那么遠就能到達邊緣。因此,一種可能的解決方案是減小 grain size,同時增加nucleation位置的數量。英特爾小組將這一想法更進一步,使用過渡金屬氧化物模式作為與硫屬元素前體反應的模板。使用模板,工藝工程師可以控制 TMD 晶粒相對于預期電路圖案的位置和方向。

較高的沉積溫度通過增加吸附原子在結合到生長膜中之前可以遷移的距離來減少雙層形成。不過,TMD 沉積溫度已經相當高,制造商希望降低它們。最后,降低生長速率使每個吸附原子有更多時間在被隨后的生長掩埋之前找到一個能量有利的位置。

新器件設計支持新邏輯概念

隨著提議的器件設計走向制造,工藝工程師必須確定是否存在合理的集成方案。例如,許多提議的設計依賴于背柵,要么應用一般的反向偏置,要么形成單獨控制的局部柵極。雖然這樣的設計相對容易通過層轉移技術制造,但直接在預先存在的柵極電介質上生長高質量的 TMD 材料并不那么簡單。

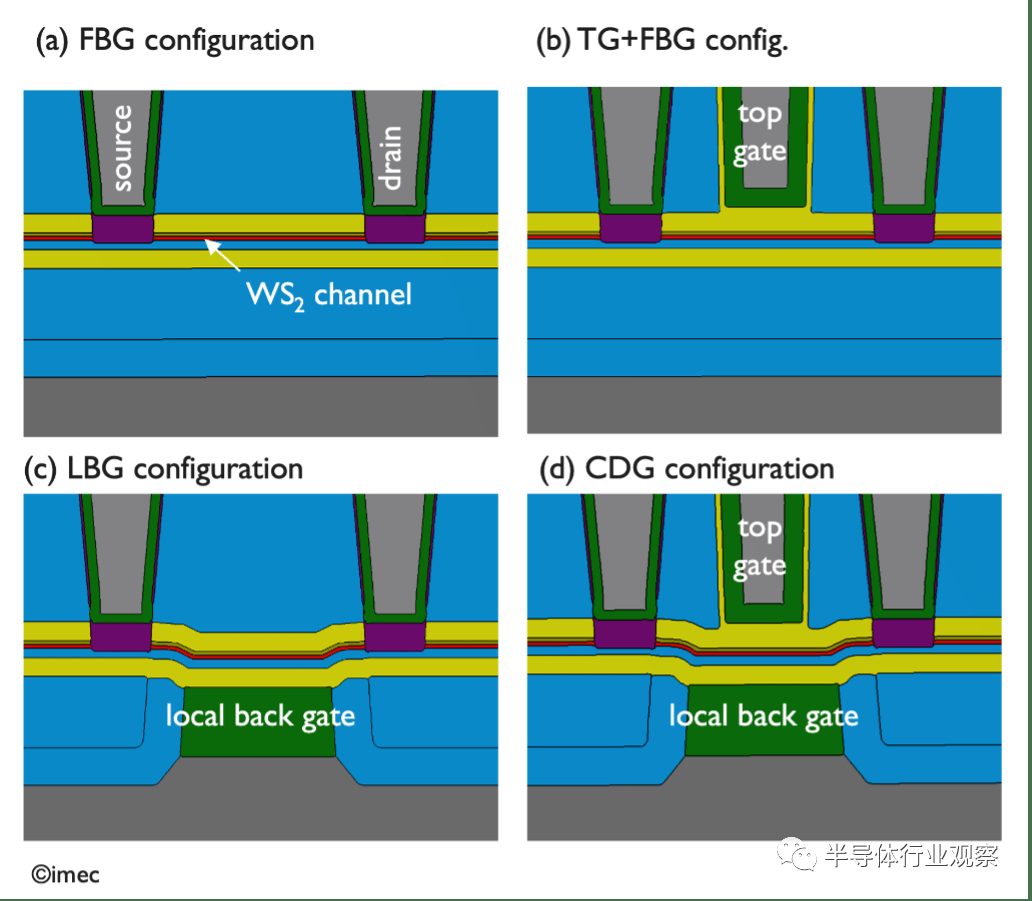

圖 1:具有可以強烈累積的厚而均勻的 EOT,全背柵配置產生最高的離子 (a);頂柵+FBG有不同的EOT,單獨掃過;本地背柵 (c) 和連接的雙柵 (d) 提供了 EOT 擴展的好處。資料來源:IMEC

在 12 月的 IEEE 電子器件會議上展示的工作中,Imec 的研究員 Quentin Smets 及其同事提出了四種不同的設計——僅全背柵、頂柵加全背柵設計、僅局部背柵和頂柵加局部背柵設計門“連接雙門”設計。其中,連接的雙門設計提供了最好的溝道控制,但結果不太一致。局部背柵處理導致通道中的形貌。在最短的柵極長度處,頂部柵極電極和電介質之間存在間隙,這可能是由于蝕刻不完全。這些不太理想的結果增加了可變性并為工藝改進提供了機會,但 CDG 設計仍然提供始終如一的更好性能。

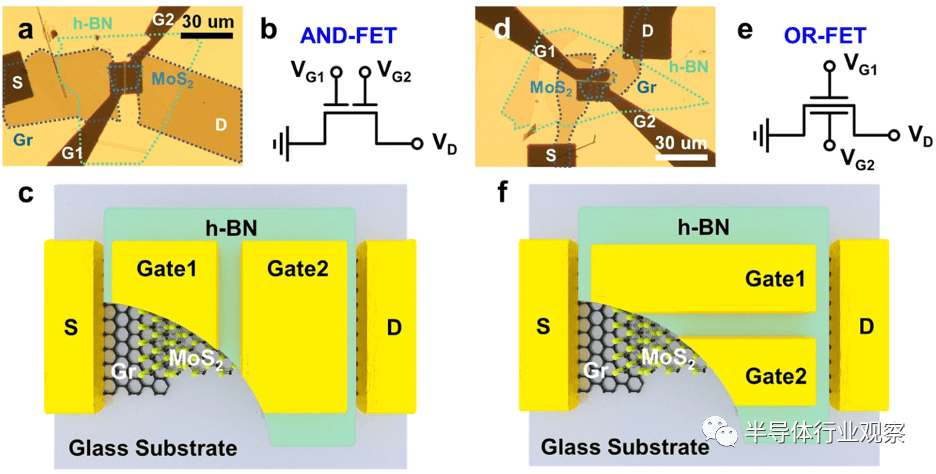

在硅GAA設計中,整個門在電氣上是一個單一的單元。只有一個偏置旋鈕。使用雙獨立門,有兩個。具有兩個輸入信號和一個輸出信號的器件可能定義一個單晶體管邏輯門。傳統的門需要至少兩個晶體管。相比之下,單晶體管門在更小的電路占位面積內提供相同的功能。臺積電的 Yun-Yan Chung 及其同事于 2020 年首次提出了基于獨立控制的頂柵和底柵的單晶體管柵極。最近,韓國仁荷大學的 Minjong Lee 及其同事展示了帶有分離頂柵的設備。在他們的 AND-FET 晶體管/柵極中,柵極的兩半垂直于溝道。僅當柵極的兩半都“開啟”時,晶體管才“開啟”。或者,在 OR-FET 晶體管/柵極中,柵極的一半與通道平行。如果柵極的任何一半“開啟”,則晶體管“開啟”。

縱向和橫向Split-Gate模型

圖 2:AND-FET(a、b、c)和 OR-FET(d、e、f)的圖像、電路圖和 3D 示意俯視圖。資料來源:知識共享

結論

現在說基于過渡金屬二硫化物通道的單晶體管門是否是數字邏輯的未來,或者晶體管最終是否會進入 BEOL 堆棧還為時過早。但隨著硅的終結——這一次可能是真的——這些材料提供了一種對后硅未來的看法。

審核編輯 :李倩

-

半導體

+關注

關注

339文章

30737瀏覽量

264184 -

晶體管

+關注

關注

78文章

10396瀏覽量

147771 -

半導體制造

+關注

關注

8文章

515瀏覽量

26122

原文標題:2D材料,半導體行業最激進的變化!

文章出處:【微信號:TenOne_TSMC,微信公眾號:芯片半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

BW-4022A半導體分立器件綜合測試平臺---精準洞察,卓越測量

一文讀懂 | 關于半導體制造數據的那些事兒

現代集成電路半導體器件

海德堡儀器攜手康耐視實現半導體制造效率全面提升

半導體制造中的高溫氧化工藝介紹

半導體制冷機chiller在半導體工藝制程中的高精度溫控應用解析

2025年半導體制造設備市場:前景璀璨還是風云變幻?

超短脈沖激光加工技術在半導體制造中的應用

麥科信獲評CIAS2025金翎獎【半導體制造與封測領域優質供應商】

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

靜電卡盤:半導體制造中的隱形冠軍

半導體制造新器件設計支持新邏輯概念

半導體制造新器件設計支持新邏輯概念

評論