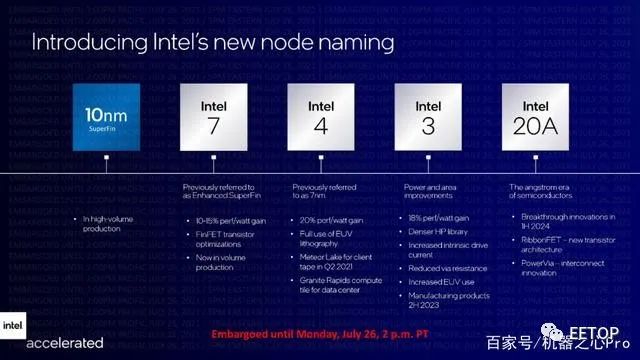

對于英特爾來說,Intel 4 是一個重要的里程碑,它既是英特爾第一個集成 EUV 的工藝,也是第一個跳出陷入困境的 10nm 節點的工藝。

本周舉行的 IEEE 年度 VLSI 研討會是業界披露和探討新芯片制造技術的重大活動之一。今年最受期待的演講之一莫過于英特爾介紹的 Intel 4 工藝的物理和性能特征,該工藝計劃將用于 2023 年的產品中。

Intel 4 工藝對于英特爾來說是一個重要的里程碑,因為它是英特爾第一個集成 EUV 的工藝,也是第一個跨越陷入困境的 10nm 節點的工藝。對于英特爾而言,Intel 4 將助其重新奪回晶圓廠的霸主地位。

英特爾本來計劃在當地時間周二發表題為「Intel 4 CMOS 技術,采用面向高密度和高性能計算的高級 FinFET 晶體管」的演講。但在展會開始之前,英特爾重新發布了有關 Intel 4 的相關數據,讓我們第一次看到了該工藝的更多信息。

Intel 4 即為以前的英特爾 7nm 工藝,是其第一次在芯片上采用 EUV 光刻技術。EUV 的使用保證了英特爾可以繪制出更先進制造節點所需的更小特征,同時使其通過多模式 DUV 技術減少制造步驟。

Intel 4 的研發對英特爾來說是一個關鍵節點,最終擺脫了 10nm 工藝。英特爾雖然已經竭力制造出適合 10nm 工藝節點的產品,尤其是最近的 10nm 增強 SuperFin 變體(我們熟悉的 Intel 7)。但英特爾試圖通過 10nm 在縮放和大量新制造技術等方面一次實現太多事情,卻導致其出現了倒退。

因而,英特爾在第一個 EUV 節點上可能不會采取太過激進的策略,總體采用更加模塊化的開發方法,逐步實現新技術,并在必要時進行調試。

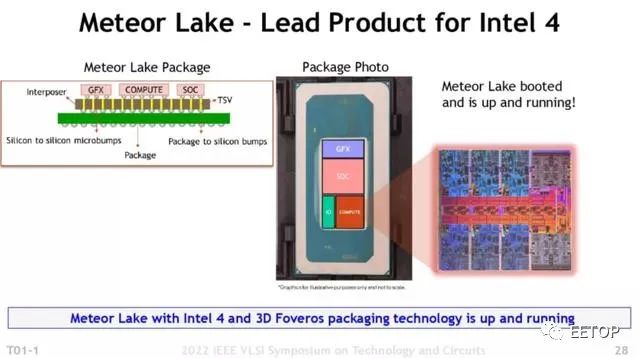

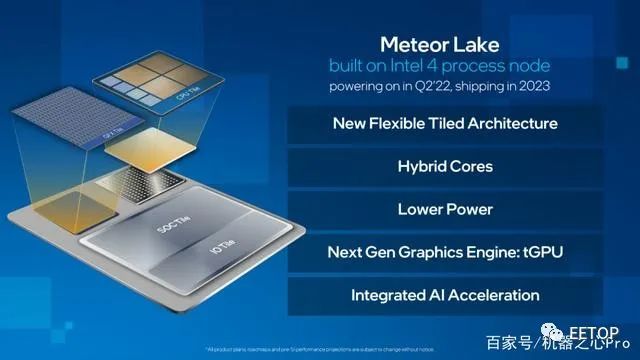

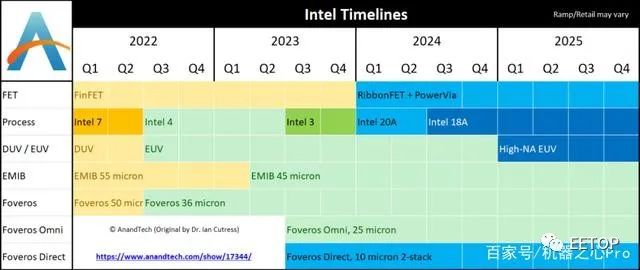

Intel 4 將首先用于英特爾即將推出的 Meteor Lake 客戶端 SoC,該 SoC 有望成為英特爾 14 代酷睿處理器系列的基礎。盡管要 2023 年出貨,但英特爾已經在實驗室中啟動并運行了 Meteor Lake。

除了在工藝技術取得顯著進步之外,Meteor Lake 還將成為英特爾首個基于 tile/chiplet 的客戶端 CPU,它混合使用了 I/O、CPU 核心和 GPU 核心的 tile。

Intel 4 物理參數:密度是 Intel 7 的兩倍,繼續使用鈷

對于 Intel 4 工藝,英特爾著手解決一些不同的問題。首先是密度,英特爾仍在努力保持摩爾定律的生命力,更高的晶體管密度可以在相同的硬件下提供更小的芯片,或者通過更新的設計集成更多的核心(或其他處理硬件)。

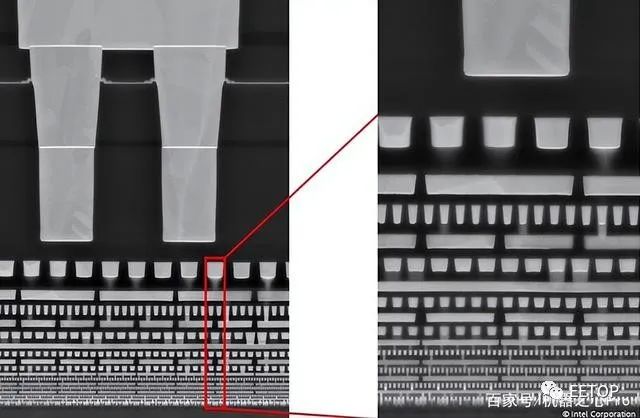

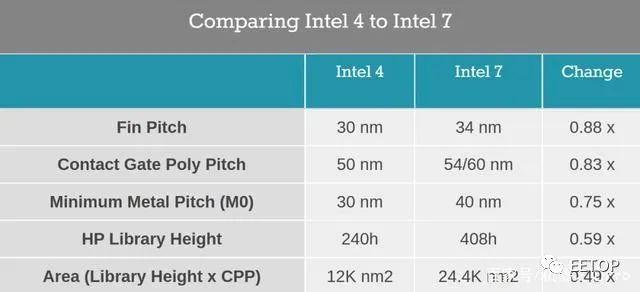

根據英特爾公布的數據,Intel 4 的鰭片間距降至 30nm,是 Intel 7 34nm 間距的 0.88 倍。同樣,接觸柵之間的間距也有之前的 60nm 降至了 50nm。最重要的是,最下層(M0)的最小金屬間距也為 30nm,是 Intel 7 上 M0 間距大小的 0.75 倍。

此外,英特爾的 Library Height 也降低了,Intel 4 上高性能(HP)庫的單元高度為 240nm,僅是 Intel 7 上單元高度的 0.59 倍。因此英特爾稱 Intel 4 的密度比 Intel 7 增加了兩倍,晶體管的尺寸減少了一半,這意味著傳統的、全節點晶體管密度的改進。

由于芯片是 2D 結構,英特爾使用的度量標準是將 HP 單元高度乘以接觸的多晶硅間距。在這種情況下,Intel 7 的單元面積為 24,408 nm^2,Intel 4 為 12,000 nm^2,后者是前者單元面積的 0.49 倍。

不過,Intel 4 上的 SRAM 單元大小僅為 Intel 7 上相同單元的 0.77 倍左右。因此,雖然標準化邏輯單元的密度翻了一番,但 SRAM 密度僅提升了 30% 左右。

此外,英特爾雖然也談及了標準單元的密度,但并沒有正式披露實際的晶體管密度數據。目前,英特爾給出的說法是,總體晶體管密度降為目前提供的 2x 倍。Intel 7 的 HP 庫的密度為 8,000 萬個晶體管 /nm^2,Intel 4 的 HP 庫的密度大約為 60MTr/mm^2。

這些數字都是針對英特爾低密度高性能庫,因此高密度庫會成為后續明顯的問題。傳統上,這些數字會進一步壓縮以換取時鐘速度的降低。然而,英特爾不會為 Intel 4 開發高密度庫。Intel 4 將是一個純粹的高性能節點,高密度設計將伴隨下一代 Intel 3 到來。

這種不尋常的研發策略來源于英特爾在工藝節點開發中的模塊化努力。在接下來五年左右,英特爾基本上會采取穩健的節點開發策略,基于 EUV 或 High-NA 機器開發一個初始節點,然后在此基礎上推出更加精煉或優化的繼任者。就 Intel 4 而言,雖然它在英特爾的發展中為 EUV 做了重要的開創性工作,但該公司未來更希望 Intel 3 成為更長壽的 EUV 節點。

這一切都意味著不需要 Intel 4 的高密度庫,英特爾計劃在一年左右的時間里讓功能更全面的 Intel 3 所取代。Intel 3 在設計上與 Intel 4 兼容,因此可以清楚地看到英特爾在時間允許的情況下推動自己的設計團隊使用后者的流程。英特爾代工服務客戶也將面臨相似的情況,他們可以使用 Intel 4,但 IFS 需要更專注于提供對 Intel 3 的訪問和設計幫助。

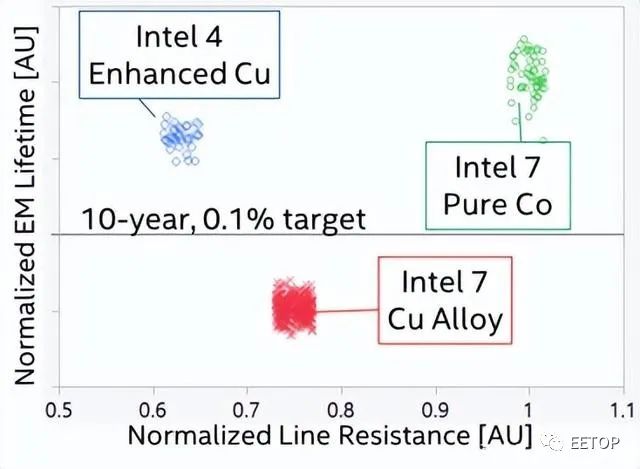

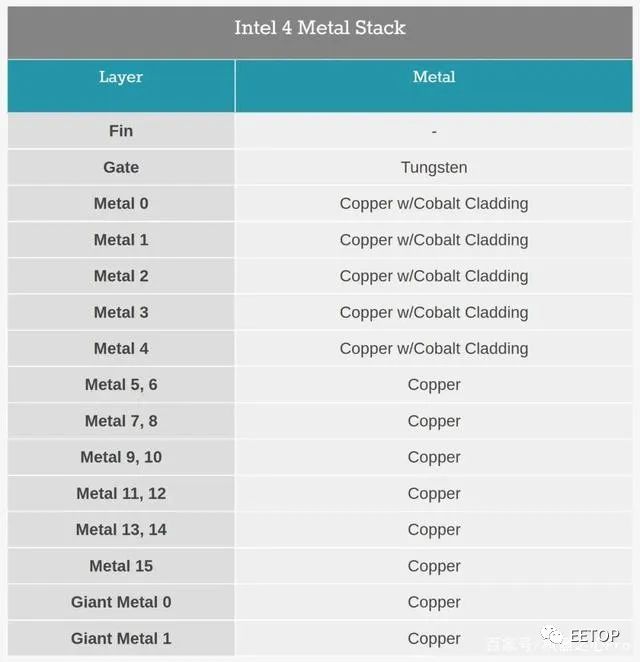

回到 Intel 4 本身,與英特爾的 10nm 工藝制程相比,新節點對金屬層有了重大改變。英特爾在其 10nm 工藝制程的最底層用鈷取代了銅,該公司認為這可以延長晶體管壽命。遺憾的是,從性能(時鐘速度)來講,鈷的性能其實沒有那么好,長期以來,人們一直懷疑,改用鈷是英特爾 10nm 開發的主要障礙之一。

對于 Intel 4,該公司仍在生產過程中使用鈷,但現在不再使用純鈷,而是使用所謂的增強型銅(Enhanced Copper,eCu),即銅包覆鈷。eCu 將二者結合起來,這樣既能保證摻雜銅金屬化層的性能,又能獲得鈷的電遷移電阻優勢。

雖然英特爾不再使用純鈷,但在某些方面,他們對鈷的使用總體上在增加。英特爾的 10nm 工藝僅在接觸柵極和前兩層金屬層中使用了鈷,而 Intel 4 正在將 eCu 的使用擴展到前 5 層。因此,英特爾芯片中最低三分之一的完整金屬層堆疊使用的是鈷包銅。然而英特爾已經從柵極本身中移除了鈷,現在是純鎢,而不是鎢和鈷的混合物。

總體來說,Intel 4 的金屬層數量比 Intel 7 有所增加,后者有 15 個用于邏輯的金屬層,而 Intel 4 有 16 層。

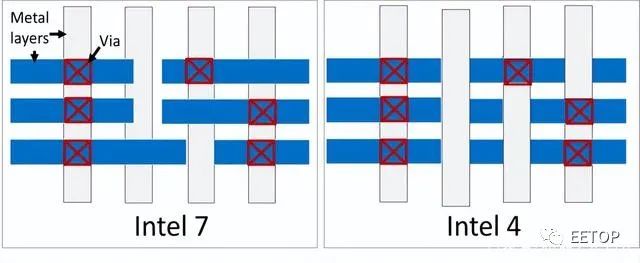

除了更加緊密的柵極和金屬層 pitches,英特爾在改變互連設計方面也改進較大。在 Intel 4 中,英特爾已經轉向網格互連設計。簡而言之,Intel 4 只允許 Via 通過預先確定的網格在金屬層之間,而此前 Via 可以放置在任何地方。

英特爾表示,網格的使用通過減少可變性以及優化設計提高了工藝的產量。這一改變還有一個額外好處,使英特爾不必為互聯使用復雜、多模式的 EUV。

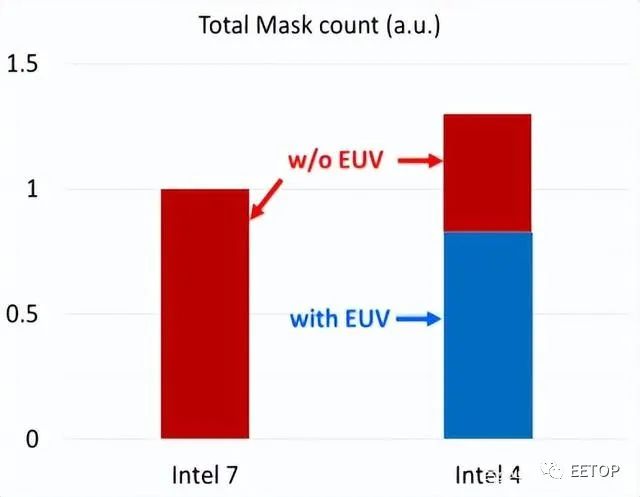

EUV 的使用使得英特爾減少了制造芯片所需的步驟和掩膜數量。雖然沒有給出絕對數字,但 Intel 4 需要的掩膜數量比 Intel 7 減少了 20%。

此外,EUV 的使用也對英特爾產生了積極的影響,雖然該公司沒有提供確切的數字。

Intel 4:頻率提高 21.5%,功耗降低 40%

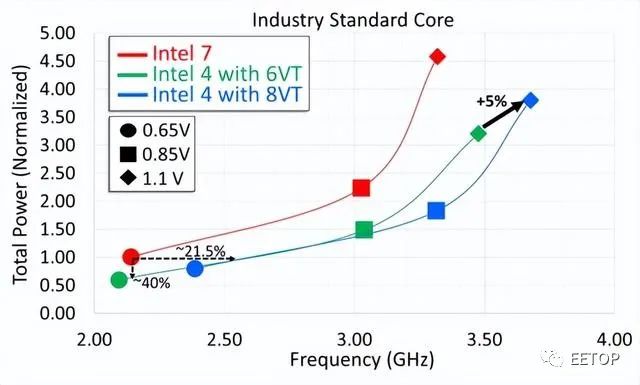

除了密度方面的改進,英特爾在頻率和能效方面都取得了高于平均水平的提升。

行業標準核心的電路分析顯示,在匹配功率為 0.65V 時,Intel 4 性能比 Intel 7 提高了 21.5%;在高電壓下,匹配功率 8VT 比 6VT 可獲得 5% 的性能增益。

在等功率為 0.65v 的情況下,與 Intel 7 相比,Intel 4 的時鐘速度提高了 21.5%。在 0.85v 及以上時,等功率增益接近 10%。

Intel 4 在電源效率方面收益更大,在等頻即 2.1GHz 左右,Intel 4 的功耗降低了 40%。隨著頻率的增加,收益遞減。

總而言之,英特爾是在不斷提升產品性能,例如在去年夏天的工藝路線圖更新中討論的 Intel 4 的每瓦性能提升 20%,去年,英特爾一直在接近 Intel 4 開發的終點線,因此正如他們所預想的那樣,英特爾似乎正在實現性能提升。

與此同時,英特爾也報告稱從 Intel 7 到 Intel 4,他們在成本上取得了良好的發展,不過該公司沒有提供具體數字。1 EUV 層確實比 1 DUV 層更貴,但由于 EUV 消除了一堆多重模式(a bunch of multi-patterning),這有助于通過減少總步驟數來降低總成本。改用 EUV 也減輕了英特爾的資金壓力。

最后,英特爾希望在 2023 年推出 Meteor Lake 和第一代 Intel 4 產品,英特爾能夠以多快的速度讓其新工藝節點啟動并付諸到大批量制造的標準,還有待觀察。不過由于 Meteor Lake 樣品已經在英特爾的實驗室中,英特爾離最終進入 EUV 時代越來越近。但對于英特爾來說,要實現所有的目標,不僅意味著要擴大希爾斯伯勒工廠的產量,還意味著要將他們的工藝遷移到生產 Intel 4 的工廠。

審核編輯 :李倩

-

英特爾

+關注

關注

61文章

10301瀏覽量

180452 -

intel

+關注

關注

19文章

3508瀏覽量

191287 -

EUV

+關注

關注

8文章

615瀏覽量

88807

原文標題:Intel 4工藝細節曝光:較上代性能提升21%、功耗降低40%

文章出處:【微信號:AI_Architect,微信公眾號:智能計算芯世界】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何確保CAT.1模組的高性能與低功耗?

晶圓工藝制程清洗方法

探索PE42641:UltraCMOS?工藝下的高性能SP4T RF開關

進程概念和特征

暫降的波形特征在判斷電網問題和裝置誤判時有多大的參考價值?

德承新款工控機P2302系列全面搭載新一代 Intel? Meteor Lake-PS Core? Ultra 7/5/3 處理器

汽車物理按鍵按壓力測試:力學性能與操作便捷性的權衡

Intel OCP 3.0用E610-IT4以太網網絡適配器數據手冊

aQFN封裝芯片SMT工藝研究

Simcenter STAR-CCM+多物理場解決方案:支持在設計早期對實際性能進行預測

Intel 4工藝的物理和性能特征

Intel 4工藝的物理和性能特征

評論