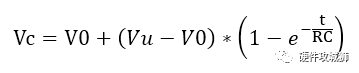

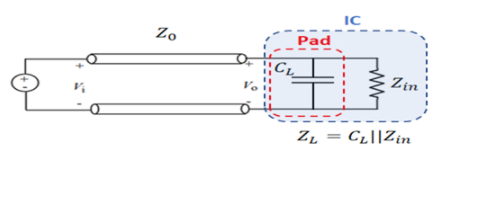

任何芯片IO都有輸入電容,通常為2pf左右,加上寄生電容,大約3ps。這個電容相當(dāng)于負(fù)載電容,高速信號在這個電容上建立電壓,相當(dāng)于給電容充電,電容的充電公式是:

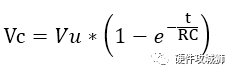

V0是電容初始電壓,Vu充滿后的電壓值,假設(shè)V0=0V。那么上面公式簡化為:

當(dāng)t = RC時,Vt = 0.63Vu;

當(dāng)t = 2RC時,Vt = 0.86Vu;

當(dāng)t = 3RC時,Vt = 0.95Vu;

當(dāng)t = 4RC時,Vt = 0.98Vu;

當(dāng)t = 5RC時,Vt = 0.99Vu;

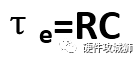

我們平時用的時間常數(shù)τe指電容兩端電壓從0V上升到1-1/e=1-37%=63%所需的時間(e=2.71828);

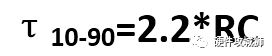

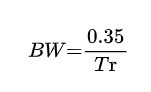

利用上述公式,計(jì)算出上升時間10%~90%所需要的時間是:

如果傳輸線阻抗50Ω,Cin=3pf,則τ10-90=0.33ns。如果信號的上升時間小于0.33ns,電容的充放電效應(yīng)將會影響信號的上升時間。如果信號的上升時間大于0.33ns,這個電容將使信號上升時間增加越0.33ns

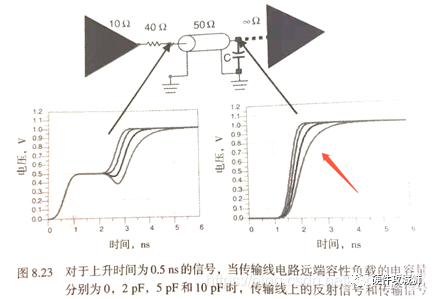

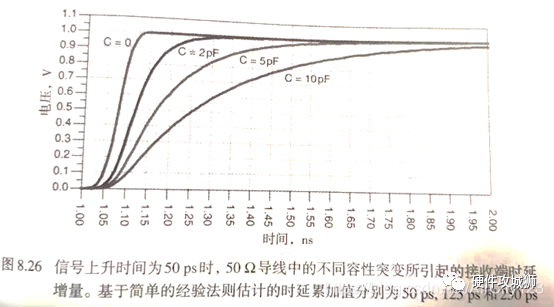

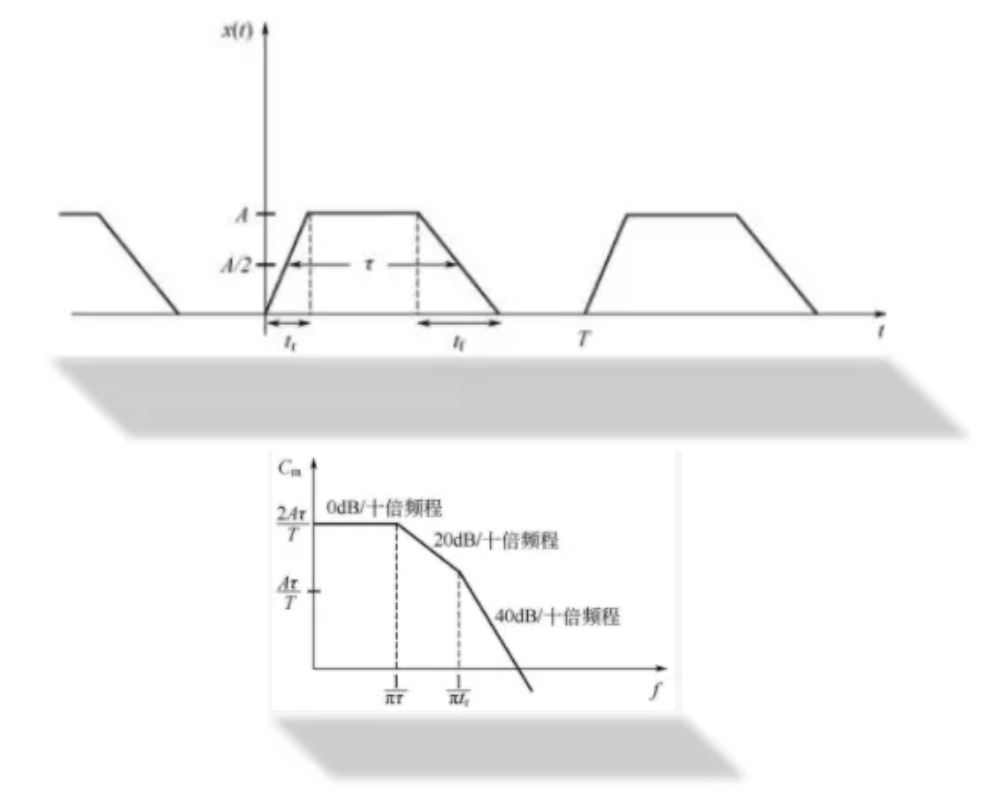

負(fù)載電容對信號上升沿的直接影響就是延長了上升時間,如下圖:

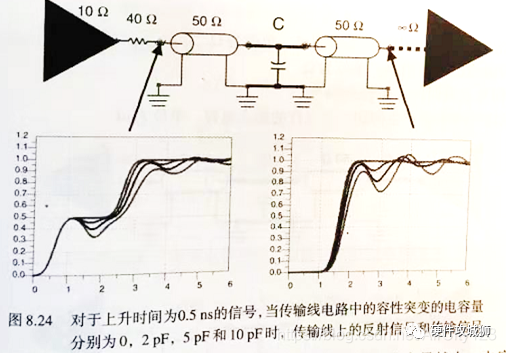

線路中途容性負(fù)載對信號的影響

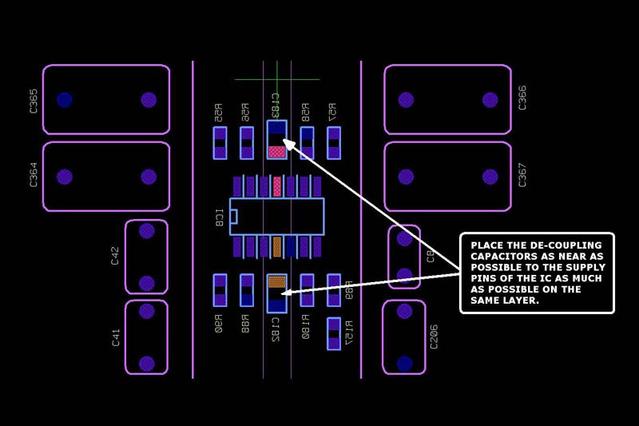

測試焊盤,過孔,封裝引線或者連接到互連線中途的短樁線,都有寄生電容,相當(dāng)于容性負(fù)載。這些容性負(fù)載通常是pf級別。

假設(shè)這些容性負(fù)載導(dǎo)致阻抗突變?yōu)?5Ω,這導(dǎo)致信號傳輸?shù)竭@里,有負(fù)的信號被反射,然后入射信號降低。當(dāng)信號到達(dá)負(fù)載端后返回,在這個點(diǎn),又有負(fù)的信號返回到負(fù)載端。從波形上看就是信號幅度下降,下沖,振鈴,上升時間增加。

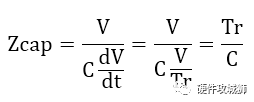

下面計(jì)算一下線路中途負(fù)載電容的阻抗:

假設(shè)上升沿是線性的dV/dt=V/Tr;

如果C很小,則Zcap很大,如果遠(yuǎn)遠(yuǎn)大于50Ω,那么與傳輸線的阻抗并聯(lián),幾乎不影響整個傳輸線阻抗。如果Zcap的值與傳輸線相當(dāng),它與傳輸線50Ω并聯(lián),形成比50Ω小的阻抗,就會引起信號完整性問題。

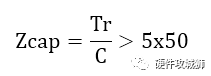

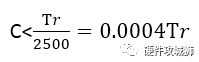

經(jīng)驗(yàn)法則是Zcap>5x50Ω,就不會引起信號完整性問題。帶入上述公式:

也即是:

假設(shè)上升時間是1nf,則允許的電容量為4pf;如果上升時間是0.25ns,則允許的電容量是1pf。

容性突變對信號上升時間的影響有一個經(jīng)驗(yàn)公式:

50Ω傳輸線,對于2pf容性突變,傳輸信號的10-90%上升時間增加約50x2pf=100ps。50%門限的延遲累加約為0.5x50x2pf=50ps。

50%門限的延遲成為延遲累加,用這個衡量電容突變對延遲的影響比較準(zhǔn)確。上面的經(jīng)驗(yàn)公式比較準(zhǔn)確,下面是仿真結(jié)果,基本能吻合:

要想降低電容突變對信號上升沿的影響,如果電容降低不了,就只能降低傳輸線阻抗了。

審核編輯 :李倩

-

電容

+關(guān)注

關(guān)注

100文章

6487瀏覽量

159354 -

信號

+關(guān)注

關(guān)注

12文章

2914瀏覽量

80138

原文標(biāo)題:電容對信號上升沿的影響

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

什么是負(fù)載電容?淺析PCB中的負(fù)載電容影響

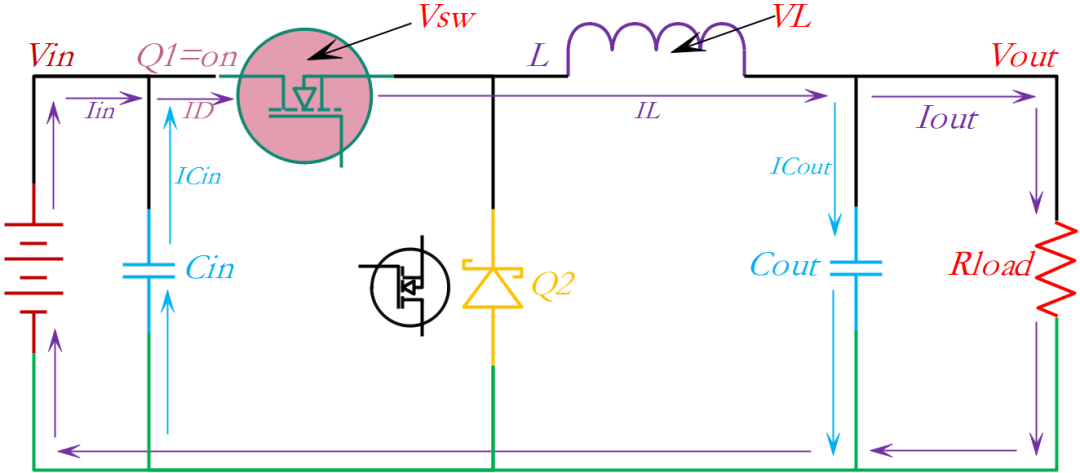

如何計(jì)算DC-DC的輸入電容Cin與輸出電容Cout

FPGA的IO口輸出20M頻率方波信號,上升沿和下降沿有毛刺怎么解決

負(fù)載電容是什么_負(fù)載電容的作用

電容對信號上升沿的影響

西門子1200上升沿和下降沿的操作流程

DC-DC的輸入電容Cin和輸出電容Cout計(jì)算選型

關(guān)于濾波電容、去耦電容、旁路電容的作用及其原理

負(fù)載電容(IO電容)Cin對信號上升沿的影響

負(fù)載電容(IO電容)Cin對信號上升沿的影響

評論