軟件定義無線電 (SDR) 將是各種移動設備的絕佳選擇,如果它不是那么耗電的話。SDR 可以安裝在更節能的芯片組中嗎?這是重新考慮架構以適應低功耗實現的案例。

對于許多已經在使用 SDR 實施的公司來說,使用匯編代碼在低級別對處理器進行編程已被證明對于實現所需的性能水平至關重要。但是,使用匯編編程有兩個主要影響:

1. 為一個處理器編寫的代碼在沒有完全重寫的情況下不能輕易地轉移到同一處理器的另一個或未來幾代。即使使用交叉匯編器也會導致翻譯性能不佳。這對大型軟件組件的可移植性有重大影響,導致成本和競爭力問題。

2. 這些匯編代碼程序的創建需要大量的專家工程時間,并且對正在實施的處理器和算法都有深入的了解。這反過來又使該方法既昂貴又耗時,從而延遲了上市時間。

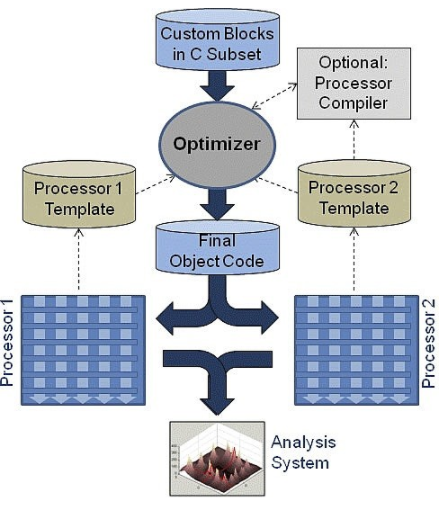

只有解決了可移植性和可編程性問題,MVR 才能在商業上運行。新興的優化技術,包括 Sigmatix 的新技術,包括在其 MVR 基帶平臺中(如圖 2 所示),以高性能方式打開了高級語言的使用。該技術利用對通常與綜合技術相關的處理器硬件的理解,并將此信息用于并行化算法并將算法緊密映射到處理器架構上。使用 C++ 模板系統將算法描述編碼為可以利用處理器提供的功能的形式,從而實現高性能的可移植性。

圖 2: Sigmatix 的 MVR 基帶平臺支持實現更高性能和可移植性的方法。

在這種方法中,協議或基帶設計工程師可以使用 C 代碼來描述他們的算法元素,而無需考慮處理器架構。處理器工程師推動模板的構建,這些模板在處理器上提供原始數據,并酌情利用部分或全部隨附的編譯器技術。優化器結合了這兩個代碼庫,修改輸入代碼以充分利用目標處理器架構來生成原始匯編代碼或包含內在函數的已處理 C 代碼,以指導進一步的編譯步驟。然后針對處理器的周期近似模型運行二進制代碼,并執行分析以檢查可能導致代碼庫改進的常見性能問題。

下一代 MVR

SDR 已被證明對軍事和商業無線基帶實施很有價值,因為它的使用提供了更高的易用性、多模應用和控制多功能性。然而,與定制硬件相比,它的低性能水平阻礙了其在商用蜂窩手機等功率敏感應用中的普及。此外,高性能匯編代碼實現缺乏可編程性和可移植性,這有損于它在更通用的基礎設施應用程序中的使用。

MVR 通過利用現代處理器架構提供的多維并行性來解決這個問題,從而在不降低基于軟件的設備的積極優勢的情況下推動性能提升一個數量級。通過利用一種以便攜和可編程方式保持性能的方法,MVR 代表了下一代基帶設計的未來。

作者:Dave Kelf,Phil Moorby

審核編輯:郭婷

-

處理器

+關注

關注

68文章

20255瀏覽量

252290 -

SDR

+關注

關注

7文章

241瀏覽量

51953 -

編譯器

+關注

關注

1文章

1672瀏覽量

51610

發布評論請先 登錄

TMS320VC5402 定點數字信號處理器深度解析

SMJ320C80數字信號處理器:架構、特性與應用全解析

TAS3103A數字音頻處理器:特性、架構與應用詳解

利用Verdi調試協處理器的實現步驟

基于E203 NICE協處理器擴展指令

提高RISC-V在Drystone測試中得分的方法

基于E203 NICE協處理器擴展指令2.0

基于蜂鳥E203架構的指令集K擴展

云拼接處理器的性能如何?

龍芯處理器支持WINDOWS嗎?

RISC-V向量處理器:現代計算的革命性引擎

通過利用現代處理器架構的并行性提高SDR的性能

通過利用現代處理器架構的并行性提高SDR的性能

評論