Xilinx SelectIO IP使用說明

引言

雷達信號處理離不開高速ADC/DAC的使用,而高速ADC/DAC的信號處理對時序的要求非常苛刻。Xilinx SelectIO IP的出現滿足了大多數芯片對于時序的處理需求,開發者可以高效的完成ADC/DAC驅動設計。

本文主要針對Xilinx SelectIO IP的GUI(圖形用戶界面),對每個參數進行詳細解釋,理解其中的內涵,快速完成驅動設計。下文詳細講述各個參數含義,內容上有些枯燥,后續進行FPGA設計實戰,理論與實際相結合。

介紹

Xilinx SelectI IP是一個VHDL/Veilog封裝文件,根據用戶配置生成實例化的I/O邏輯,滿足了輸入SERDES、輸出SERDES和延遲模塊的應用要求。另外,它也可以例化生成所需的I/O時鐘原語,將它連接到I/O引腳。

特色

支持輸入、輸出或雙向總線,數據總線寬達16位,滿足絕大多數器件的設計要求;

創建驅動I/O所需的時鐘電路邏輯,分為內部時鐘或外部時鐘電路邏輯;

可選數據或時鐘延遲插入,對數據信號進行同步或數據信號與時鐘信號之間進行同步;

支持單、雙數據速率,實現信號與數據的相互轉換;

支持多種數據總線標準:芯片對芯片、相機接收器、相機發射器、數字視覺接口(DVI)接收接口、發送接口和串行千兆媒體獨立接口(SGMII);

產品說明書

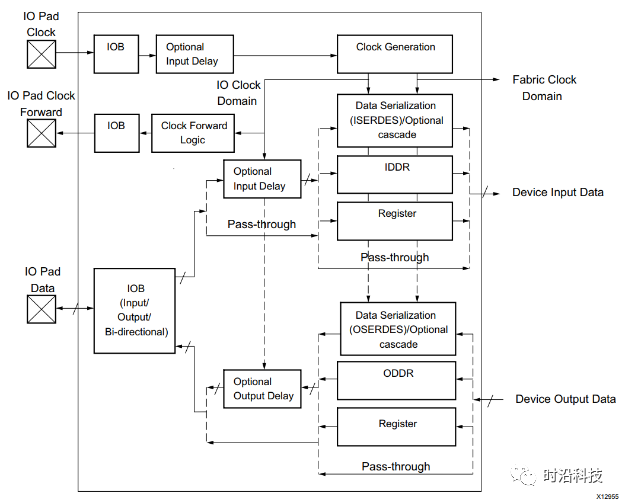

SelectIO接口提供了源代碼HDL,包括輸入、輸出或雙向總線I/O電路,緩沖區,任何所需的延遲元件,ISERDES和OSERDES、寄存器和I/O時鐘驅動的實現。電路設計包含兩個主要組件:時鐘緩沖和處理,以及數據路徑。

SelectIO內部框圖

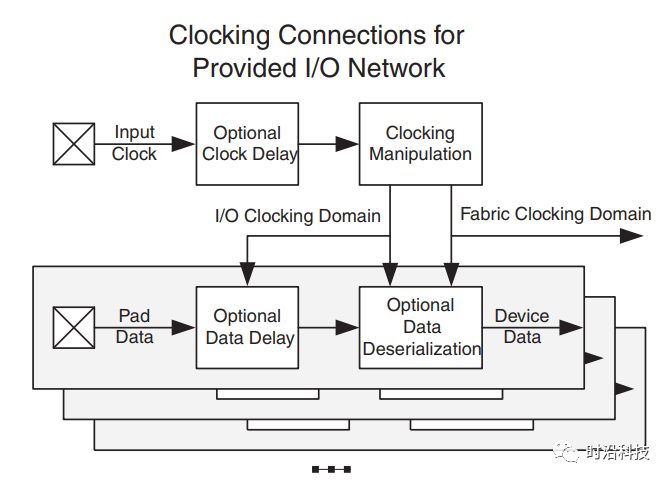

時鐘緩沖和處理

SelectIO向導支持對時鐘I/O邏輯使用BUFG或BUFIO2。一個帶有BUFIO2原語的輸入數據如下圖所示。可以為輸入時鐘添加插入延遲。

I/O網絡時鐘連接

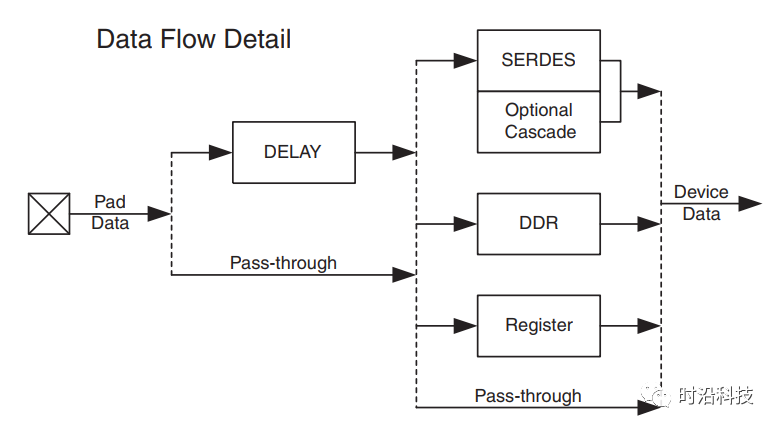

數據路徑

SelectIO向導幫助在I/O中實例化和配置組件互連。你可以選擇:

使用或繞過延遲功能。

通過使用輸入SERDES或輸出SERDES來使用串并轉換/并串轉換功能。

支持雙數據速率(DDR)數據。

為單速率數據使用I/O寄存器。

數據流細節

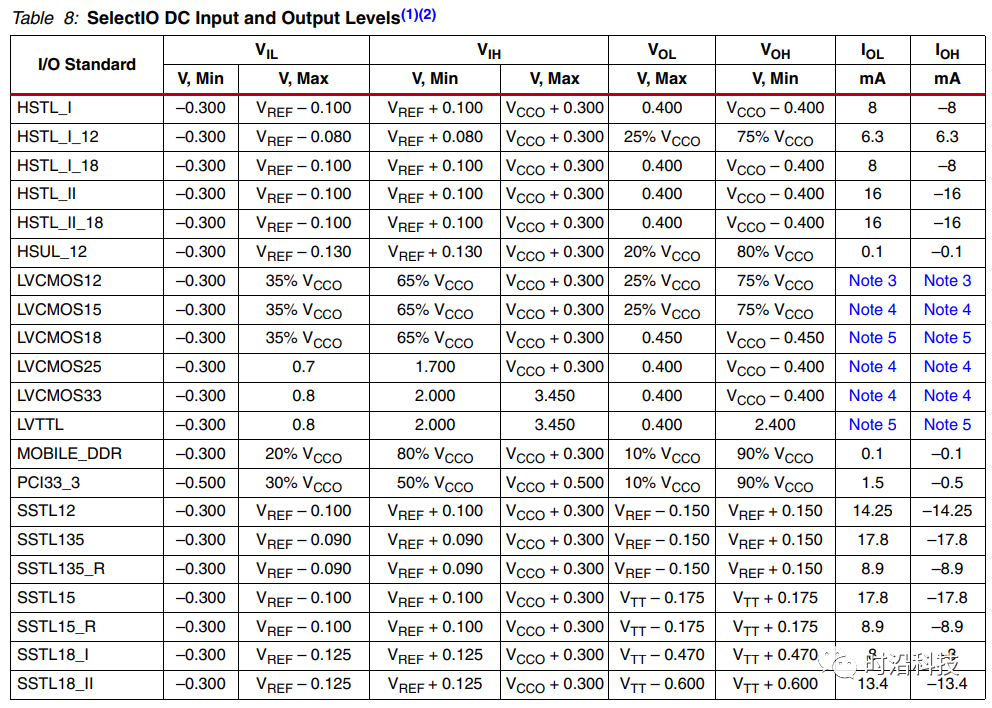

標準

該接口支持下列I/O標準。

單端信號:??HSTL_I, HSTL_II, HSTL_III, HSTL_I_18, HSTL_II_18, HSTL_III_18, HSTL_I_12, LVCMOS33, LVCMOS25, LVCMOS18, LVCMOS15, LVCMOS12, SSTL15SSTL18_I, SSTL18_II

差分信號:??DIFF HSTL I, DIFF HSTL I 18, DIFF HSTL II, DIFF HSTL II 18, DIFFSSTL15, DIFF SSTL18 I, DIFF SSTL18 II, LVDS25, TMDS_33, MINI_LVDS_25, PPDS_25,BLVDS_25、LVDS RSDS_25

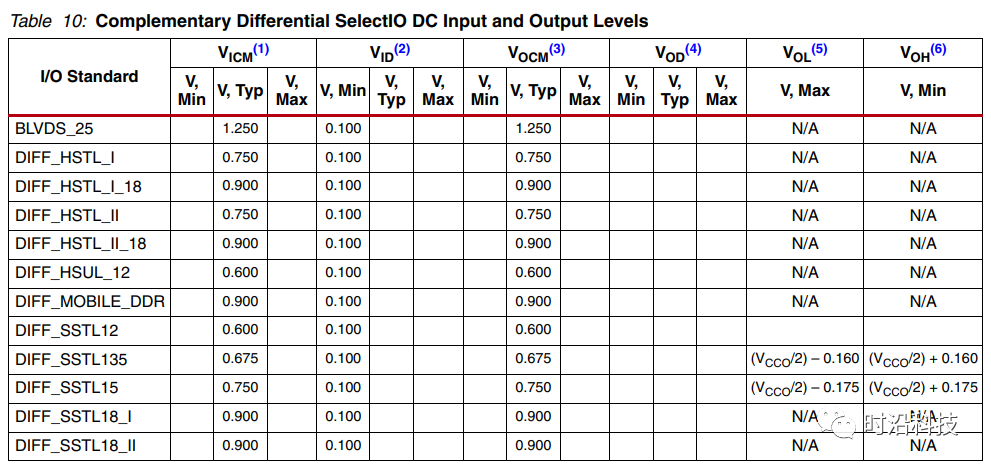

SelectIO單端輸入輸出電平

SelectIO差分輸入輸出電平

更多關于Select IO邏輯資源的詳細介紹(比如LOGIC、DELAY、DELAYCTRL、SERDES等),請閱讀ug471_7Series_SelectIO.pdf

設計流程

本章描述了定制和生成核、約束核和的仿真、合成和實現步驟。

Data Bus Setup

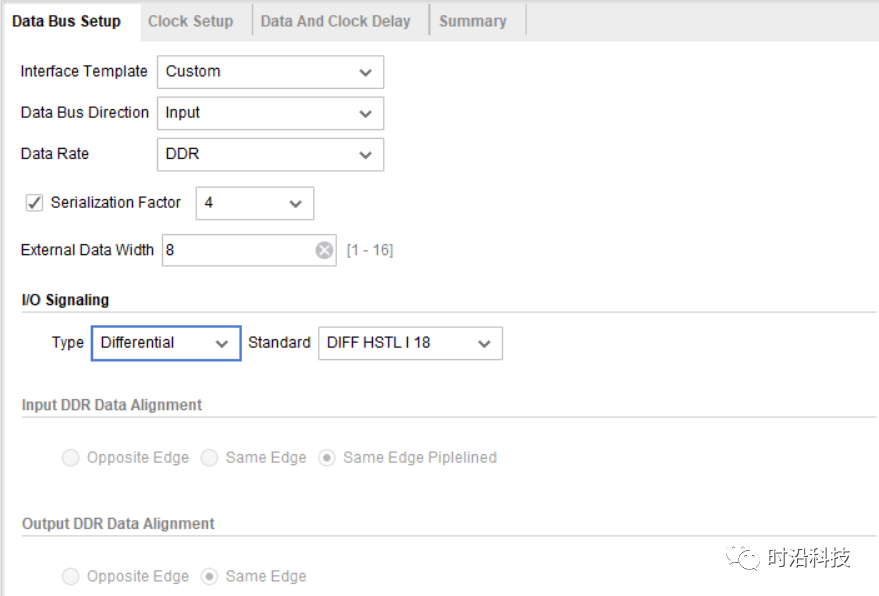

Data Bus Setup界面

Interface Template

選擇向導支持SGMII, DVI接收器,DVI發射器,Camera link接收器數據總線格式,攝像頭連接發射器和芯片對芯片接口。SelectIO接口向導僅為上面提到的所有接口配置數據引腳。一般選擇Custom或者Chip to Chip來完成高速ADC、DAC芯片或者AD/DA芯片的時序設計。

Data Bus Direction

總線的方向可以選擇。選擇向導支持輸入,輸出,雙向和單獨的I/O總線。單獨的輸入和輸出選項創建獨立的輸入和輸出引腳。開發者根據所用芯片的引腳實際方向進行選擇。

Data Rate

如果數據在上升沿觸發時,請選擇SDR。如果上升沿與下降沿都觸發,選擇DDR。數據速率的選擇影響序列化因子限制。

Serialization Factor

如果選擇了序列化因子,將實例化ISERDESE2(串并轉換器)和/或OSERDESE2(并串轉換器)。所有數據由時間片,然后從右到左連接。例如,假設輸出數據總線是8位寬的,序列化因子為4。如果數據在引腳上顯示為:00,01、02、03時,呈現給設備的數據將為03020100。如果選擇了10或14的序列化因子,那么每個I/O將實例化兩個SERDES塊因為每個SERDES的最大序列化能力是8:1。當數據速率為SDR時,序列化因子的可能值為2-8。當數據速率為DDR時,序列化因子可設置為4、6、8、10或14。Bitslip對于網絡模式總是啟用功能。如果不是,則將此引腳綁定到邏輯0。

如果所用ADC/DAC芯片為串行數據輸入輸出,選擇序列化因子,可以方便的實現串并、并串數據之間的轉換。

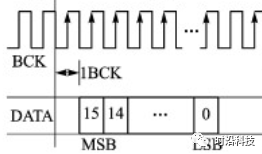

串行數據時序

如果選擇了序列化因子,IP自動生成ISERDESE2或者OSERDESE2,IP引腳會多出Bitslip,其用來實現并行數據的邊界對齊。比如串行輸入的8bit的數據,經過ISERDESE2后,得到8bit的并行數據,但這并行數據可能存在前后8bit數據之間的錯位,也即無法正確判斷最高位、最低位, Bitslip就是用來找到并行數據的邊界。

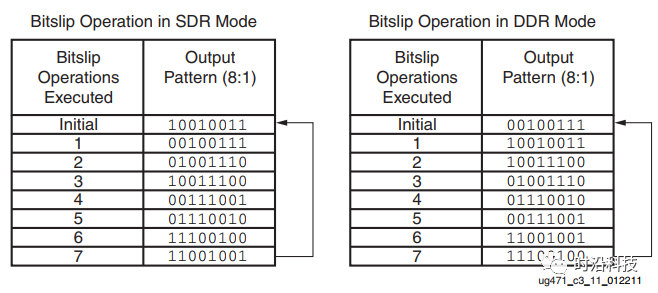

下圖展示了Bitslip是如何確定并行數據的邊界:對于SDR模式,Bitslip使能1次,則數據會左移1次,對于8bit并行數據,移動8次完成一個循環,可以這樣無止境的循環。對于DDR模式,Bitslip工作方式不同,Bitslip使能1次,數據會右移1次或者左移3次,兩者交替進行,同樣移動8次完成一個循環。

不同模式Bitslip操作

External Data Width

芯片的并行輸入、輸出引腳的數目,比如:并行16位ADC芯片,數據寬度填寫16。

I/O Signaling

所有的I/O信號標準都顯示為所選擇的I/O信號類型。根據實際外部芯片ADC/DAC引腳的實際信號類型進行設置。

Input DDR Data Alignment

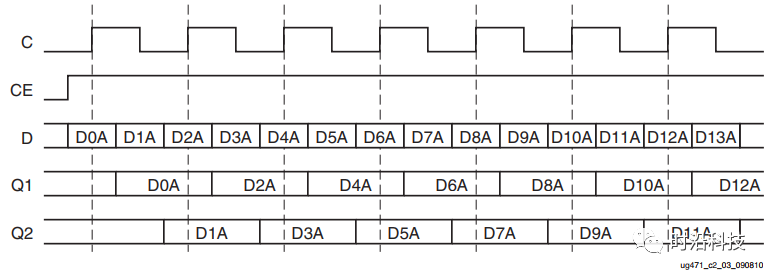

OPPOSITE_EDGE

上升沿觸發的數據通過輸出端Q1呈現,下降沿觸發的數據通過輸出端Q2呈現。

OPPOSITE_EDGE模式

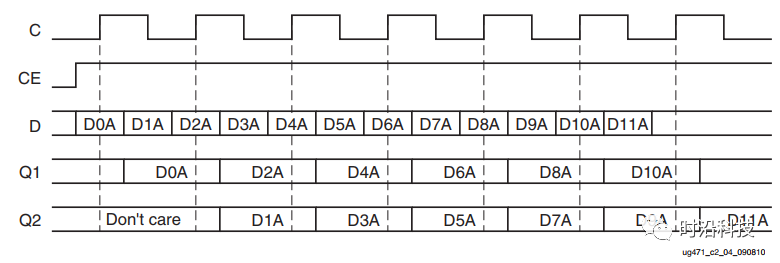

SAME_EDGE

在時序圖中,同一時刻輸出對Q1和Q2不再是D0A和D1A,而是第一對呈現的是一對D0A和(不關心),然后下一個時鐘輸出一對D2A和D1A。

SAME_EDGE模式

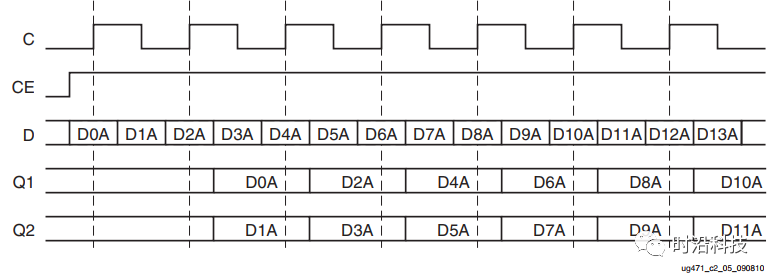

SAME_EDGE_PIPELINED

輸出對Q1和Q2在同一時刻輸出。

SAME_EDGE_PIPELINED模式

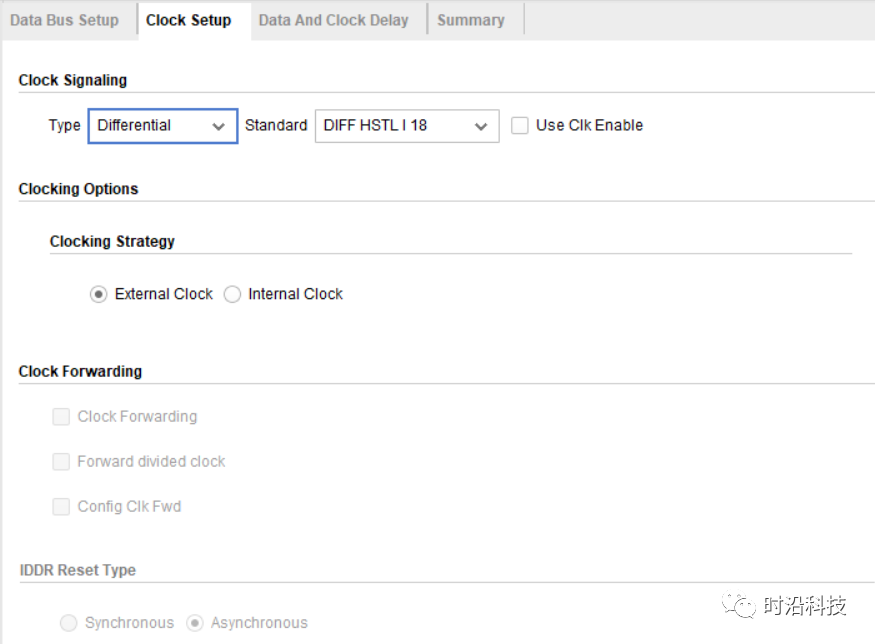

Clock Setup

Clock Setup界面

External Clock

如果在輸出數據路徑上設置了任何延遲,則將同樣的延遲分配給時鐘,使數據和時鐘保持同步。

Internal Clock

如果你的時鐘來自時鐘輸出模塊,你會想要選擇內部時鐘,但是需要確保實例化一個MMCM來驅動時鐘。

Clocking Signaling

您可以為輸入時鐘指定信令類型和標準。I / O信號標準將嵌入所提供的HDL源代碼。

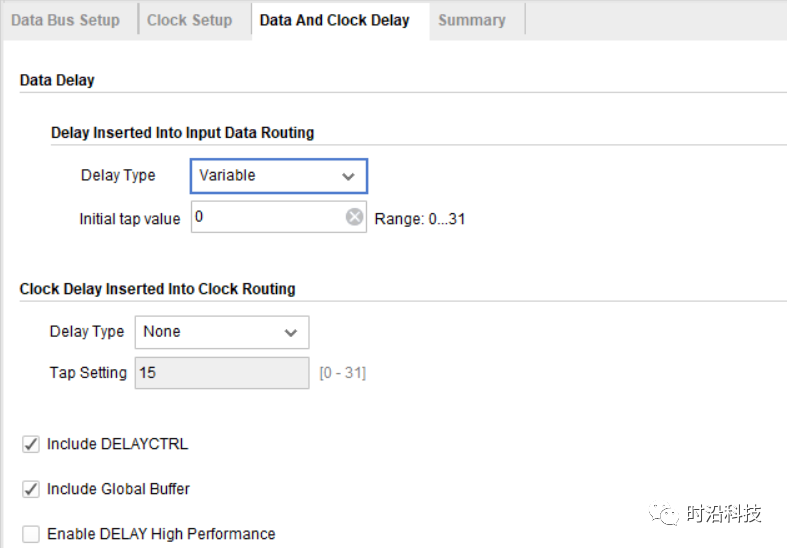

Data And Clock Delay

Data And Clock Delay界面

Delay Type

FIXED

在固定延遲模式下,延遲值由屬性IDELAY_VALUE確定。一旦設置,該值不能為改變了。在此模式下使用時,必須實例化IDELAYCTRL原語。

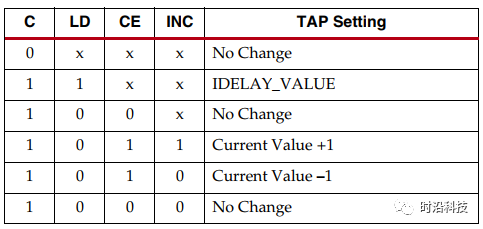

VARIABLE

在可變延遲模式下,延遲值可以通過控制信號CE和INC配置。在此模式下使用,IDELAYCTRL原語必須實例化。

VARIABLE模式延時控制

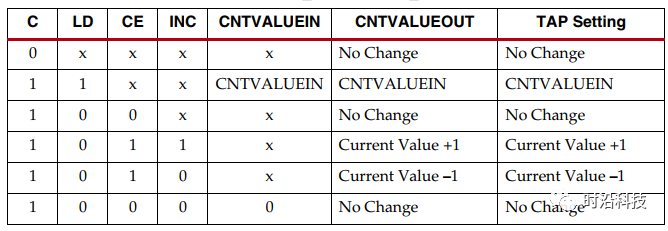

VAR_LOAD

IDELAY tap可以通過5輸入位CNTVALUEIN[4:0]設置。當LD脈沖時,CNTVALUEIN[4:0]的值將是新值。作為這個功能的結果,IDELAY_VALUE屬性是忽略了。在此模式下使用時,必須實例化IDELAYCTRL原語。

VAR_LOAD模式延時控制

Include DELAYCTRL

只適用于固定/可變的延遲。如果選中,則包含IODELAYCTRL在設計中實例化。

Include Global Buffer

如果選中,則在設計中實例化BUFG。當未選擇包含DELAYCTRL時,沒有啟用BUFG以供選擇。

Enable DELAY High Performance

如果啟用,則設置IDELAY塊的HIGH_PERFORMANCE_MODE屬性為true,否則設置值為false。

審核編輯 :李倩

-

Xilinx

+關注

關注

73文章

2200瀏覽量

131139 -

參數

+關注

關注

11文章

1869瀏覽量

33947 -

GUI

+關注

關注

3文章

697瀏覽量

43472

原文標題:Xilinx SelectIO IP使用說明

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

ESD測試的詳細解釋

恩智浦GUI Guider 1.10.0正式上線

基于E203的DMA ip的使用

關于保偏光纖的詳細解釋

FPGA利用DMA IP核實現ADC數據采集

GUI Guider全新優化方案GUI xTurbo-VeloRender初體驗:基于i.MX RT平臺的LVGL渲染能力突破

ip6808參數詳細解釋

Xilinx Shift RAM IP概述和主要功能

AWTK,開啟屬于你的GUI之美

ip6806芯片的詳細參數解析

詳解Xilinx的10G PCS PMA IP

Xilinx SelectIO IP的GUI參數詳細解釋

Xilinx SelectIO IP的GUI參數詳細解釋

評論