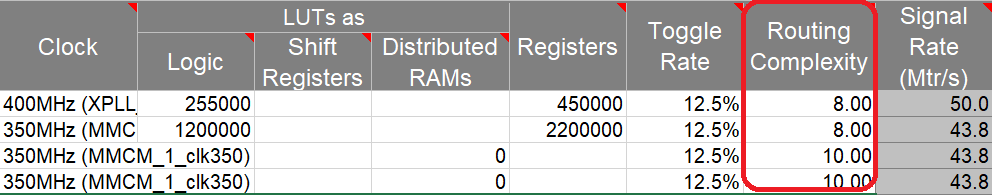

在對XilinxFPGA設計進行功耗評估時,都要用到XPE(XilinxPower Estimator)。從2015.4版本開始,針對UltraScale/UltraScale+器件,Fanout被RoutingComplexity所取代,以獲取更為精確的的評估結果,如下圖所示。

在老版本的XPE中,對于動態功耗,需要準確填入扇出以估計布線資源的使用率。這里有一個假設:扇出越大,消耗的布線資源就越多。這會帶來一個問題:如果一個設計中的短線或長線用得比較多,那么評估的布線模型就與實際布線結果不同。為了補償這個差異,從2015.4版本開始,用物理實現的Routing Complexity取代了邏輯定義的扇出。 那么Routing Complexity是什么含義呢?

RoutingComplexity實際反映的是每個logic cell使用的布線資源的平均數目。此值越大說明布線擁塞程度越高。典型值為8(也是默認值),可滿足大部分設計的需求。同時,應將此值控制在5~15之間,過高(超過15)或過低(小于5)都不合適。例如,對于一個全局復位信號,其扇出非常大,導致RoutingComplexity可能超過20,畢竟這個net需要到達芯片幾乎所有的邏輯單元。但這種情況是比較罕見的。另一方面,某個net扇出為1,并且源端和目的端在同一個SLICE,那么Routing Complexity就會非常低。這種情況也是非常罕見的。 在填寫RoutingComplexity時,需要考慮如下幾個因素:扇出、芯片規模、設計的資源利用率、綜合或布局布線跟Floorplan相關的選項。 另一方面,如果我們已經有一個現成的設計,并完成了布局布線,那么可以在Vivado下利用命令report_power生成.xpe,并將該文件導入到XPE中,相應的Routing Complexity的值就會被反標到XPE里,這樣可獲得較為精確的RoutingComplexity。

審核編輯 :李倩

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636331 -

布線

+關注

關注

9文章

821瀏覽量

86145

原文標題:XPE中的routing complexity怎么填?

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

多模光纜型號字母代碼及其含義

解析PD協議DRP角色含義及LDR6020 DRP芯片核心特性

高清視頻光端機指示燈含義全解析:廣州郵科設備狀態一目了然

村田貼片電感的精度檔位及代表含義是什么?

電流探頭 100mV/A應該如何解讀呢?

變頻器通訊代碼地址的含義

怎樣理解變頻器內置PID控制參數的含義

常用電子元器件字母和含義解析

光纖收發器6個指示燈含義

Routing Complexity是什么含義呢?

Routing Complexity是什么含義呢?

評論