對于實時系統,尤其是對安全至關重要的系統,多核處理器由于對處理器內核之間共享資源的爭用,對嚴格的確定性提出了重大挑戰。

嵌入式系統在更高的吞吐量和更好的尺寸、重量和功率 (SWaP) 方面受益于多核處理器的使用。具有異構處理器內核的處理器增加了將應用程序與每種內核類型的功能相匹配的能力,進一步提高了吞吐量和 SWaP。多核處理器的優勢在于軟件架構的復雜性增加,以最大限度地利用處理器內核。對于實時系統,尤其是對安全至關重要的系統,多核處理器由于對處理器內核之間共享資源的爭用,對嚴格的確定性提出了重大挑戰。這一挑戰隨著異構內核的增加而增加,因為最壞情況下的執行時間可能會因應用程序執行的內核而異。

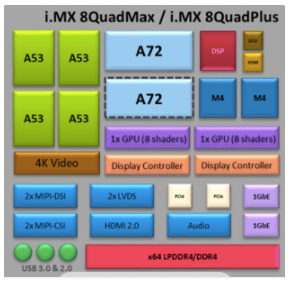

要更詳細地探索這種權衡,請考慮 NXP? i.MX 8QuadMax 應用處理器中的異構內核(圖 1)。i.MX 8QuadMax 具有四個 Arm? Cortex?-A53 內核和兩個 Cortex-A72 內核,可通過將每個應用任務的性能要求與不同內核的性能容量相匹配來實現功耗優化。與 A53 核心相比,A72 核心提供大約兩倍的性能,但功耗更高。

圖 1:NXP i.MX 8 架構

為了實現多核解決方案的吞吐量和 SWaP 優勢,軟件架構需要支持可用處理器內核的高利用率。必須支持所有多核功能,從啟用內核的并發操作(相對于可用內核被強制進入空閑狀態或在啟動時保持重置)到提供確定性負載平衡機制。軟件多處理架構越靈活,系統架構師實現高利用率所需的工具就越多。

軟件多處理架構

與多處理器系統一樣,多核處理器上的軟件架構可以根據內核之間共享和協調的數量進行分類。基于多核的系統最簡單的軟件架構是非對稱多處理 (AMP),其中每個內核獨立運行,每個內核都有自己的操作系統或管理程序/客戶操作系統對。每個核心運行不同的應用程序,核心之間在調度方面很少或沒有有意義的協調。由于缺乏負載平衡、難以緩解共享資源爭用以及無法跨核心執行協調活動(例如綜合內置測試所需的),這種解耦可能導致利用率不足。

AMP 的現代替代方案是對稱多處理 (SMP),其中單個操作系統控制所有資源,包括哪些應用程序線程在哪些內核上運行。這種架構易于編程,因為所有內核都“對稱”地訪問資源,從而使操作系統可以將任何線程分配給任何內核。對于具有異構內核的處理器,例如 i.MX 8QuadMax,不知道應用程序將在哪種類型的內核上運行可能會導致執行時間范圍廣泛,從而顯著影響確定性性能。

綁定多處理 (BMP) 直接解決了這個問題,它是一種增強型和受限形式的 SMP,它將應用程序的任務/線程靜態綁定到特定內核。這種靜態綁定允許系統架構師嚴格控制多個內核的并發操作。

確保確定性行為

除了實現多核處理器的吞吐量和 SWaP 目標外,安全關鍵系統還需要為每個應用程序保持可預測的最壞情況執行時間 (WCET)。使用 BMP 限制與應用程序配對的內核類型是確保異構系統中確定性行為的重要組成部分。確保確定性的其他技術是時間和空間分區以及管理共享資源的爭用。

在單核處理器中,多個安全關鍵應用程序可以通過在托管應用程序之間穩健地劃分內存空間來在同一處理器上執行。內存空間分區將內存的非重疊部分專用于在給定時間運行的每個應用程序,由處理器的內存管理單元 (MMU) 強制執行。確定性可以通過使用時間劃分來進一步增強,時間劃分將一個固定的時間間隔(稱為主幀)劃分為一系列固定的子間隔,稱為劃分時間窗口。每個應用程序都分配有一個或多個分區時間窗口,窗口的長度和數量由應用程序的 WCET 和所需的重復率決定。

多核干擾挑戰確定性

在多核環境中,可以有多個應用程序在不同的內核上同時運行。這些并發應用程序每個都需要訪問處理器的資源。每個處理核心都有一些專用資源,但大多數資源在處理器核心之間共享,包括內存控制器、I/O、共享緩存以及連接它們的內部結構。當多個處理器內核嘗試同時訪問同一資源時,會導致這些共享資源的爭用。在航空電子設備等安全關鍵型應用程序中,主要問題是這種共享資源爭用如何導致運行在一個內核上的應用程序干擾運行在另一個內核上的應用程序,從而對確定性、服務質量以及最終的安全性產生負面影響。

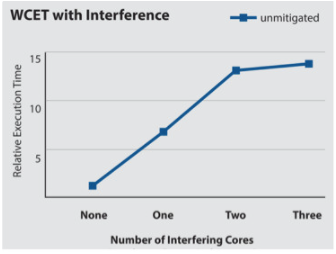

如果不加以緩解,共享資源爭用的影響可能會很大。僅檢查其中一種共享資源 DDR 內存,人們可能會猜測,當另一個內核嘗試訪問同一內存并且兩個內核都運行內存受限的應用程序時,WCET 可能會翻倍。實際上,由于共享資源仲裁和調度算法中的非線性行為,WCET 可以增加 8 倍而不是 2 倍。嘗試訪問 DDR 內存或爭奪其他資源(例如片上互連)的其他內核可能會導致 WCET 增長得更加顯著(圖 2)。

圖 2:多核干擾的增加速度快于核心數量。

多核干擾緩解

減輕多核干擾的一種方法是手動調度應用程序以最小化資源爭用。這種方法不會消除所有干擾,并且任何時候修改任何單個應用程序或添加新應用程序都需要重新測試和驗證所有應用程序。另一種方法是安排一次只運行一個多任務應用程序。任務之間仍然會發生干擾,但不會對其他應用程序產生干擾。這種方法在具有異構內核的處理器上尤其無效,因為不同內核類型的執行時間不同。

更通用的方法是讓操作系統管理共享資源爭用。與操作系統使用硬件 MMU 通過將不同的內存區域分配給不同的應用程序來實現空間分區的方式相同,操作系統可以按內核為共享資源分配帶寬。解決操作系統中的多核干擾為系統集成商提供了有效、靈活和敏捷的解決方案。它還簡化了新應用程序的添加,而無需對系統架構進行重大更改,并減少了重新驗證活動。

航空電子設備中異構核心的示例解決方案

NXP i.MX 8QuadMax 應用處理器包括四個共享 1MB L2 緩存的 Arm Cortex-A53 內核和兩個共享另一個 1MB L2 緩存的 Arm Cortex-A72 內核。該處理器還包括兩個用于卸載系統功能的 Cortex-M4F 內核和兩個能夠運行 OpenCL、Vulkan 和 OpenVX 視覺加速的 GPU。i.MX 8 的一項獨特功能是硬件資源分區,其中系統控制器將外圍設備和內存區域提交到特定的客戶定義域中。域之間的任何通信都被迫使用通過硬件消息單元運行的消息協議。i.MX8QuadMax 面向廣泛的應用,包括工業 HMI(人機界面)和控制、電子駕駛艙 (eCockpit)、平視顯示器、樓宇自動化和單板計算機。

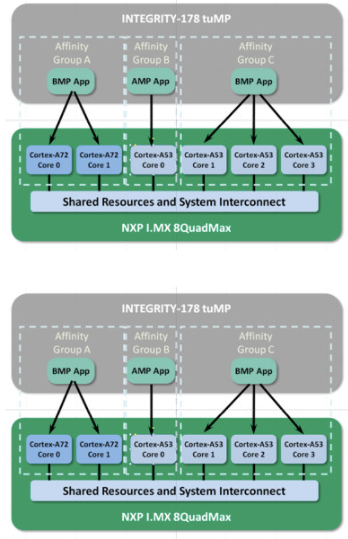

綠山的誠信?-178 tuMP? 多核 RTOS 是一個統一的操作系統,可在 i.MX 8 中的所有 64 位處理器內核上運行,并支持 AMP、SMP 和 BMP 的同時組合。RTOS 的時變統一多處理 (tuMP) 方法為將安全關鍵型和安全關鍵型應用程序移植、擴展和優化到多核架構提供了最大的靈活性。INTEGRITY-178 tuMP 使用跨所有內核運行的時間分區內核,允許應用程序綁定到一個內核或稱為關聯組的內核組。如果需要,可以進一步限制關聯組中應用程序的每個任務以在特定核心上運行。對于 i.MX 8QuadMax 處理器,

圖 3:使用 Affinity Groups,一個應用程序綁定到兩個 Cortex-A72 內核,而另外兩個應用程序綁定到一組 Cortex-A53 內核。

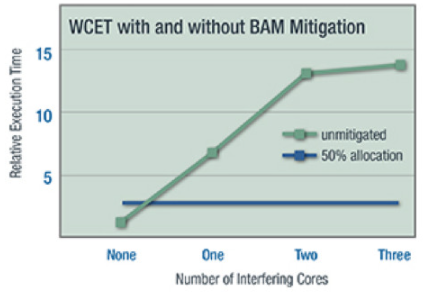

INTEGRITY-178 tuMP 直接解決多核干擾,包括開發到最嚴格安全級別的帶寬分配和監控 (BAM) 功能。BAM 功能監控并強制分配來自每個處理器內核的共享資源的帶寬。BAM 模擬一種基于硬件的高速方法,以確保對每個核心對共享資源的使用進行連續分配強制。BAM 在整個應用程序的執行時間窗口中平滑地調節帶寬,從而允許同一執行時間窗口中的其他應用程序獲取它們分配的共享資源部分。使用前面的內存訪問干擾示例,將 50% 的內存帶寬分配給高關鍵應用程序會導致幾乎恒定的 WCET,即使干擾內核的數量增加,而當存在多個干擾內核時,WCET 也會降低 8 倍(圖 4)。這種能力有效地減輕了多核干擾并大大降低了集成和認證風險,同時還使集成商能夠獲得多核處理器的最大性能優勢。

圖 4:使用 BAM 將 50% 的共享資源帶寬分配給關鍵應用程序后,WCET 幾乎保持不變并大大降低。

NXP i.MX 8QuadMax 為優化航空電子設備和其他嵌入式實時系統中的 SWaP 提供了重要機會。Cortex-A72 和 Cortex-A53 內核的結合使系統架構師能夠強調性能或電源效率,從而創建最佳的系統級解決方案。相應的軟件架構需要具有靈活性和可控性,以充分利用這些異構應用內核,同時保持嚴格的確定性。結合使用 Affinity Groups 或某種其他形式的 BMP 的能力以及多核干擾緩解解決方案(例如 BAM),可以在安全關鍵型應用中有效使用 i.MX 8QuadMax。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

20255瀏覽量

252308 -

嵌入式

+關注

關注

5198文章

20449瀏覽量

334079 -

NXP

+關注

關注

61文章

1396瀏覽量

197657

發布評論請先 登錄

驅動板PCB布線的注意事項

信號調理設備的接地和環境適配有哪些注意事項?

電機維修安全注意事項

裝置日常運行時的安全防護檢查有哪些注意事項?

別讓這些細節毀了PCBA!焊接注意事項清單

智多晶PLL使用注意事項

IGBT器件的防靜電注意事項

設置射頻網絡分析儀的測試條件有哪些注意事項

SiC MOSFET驅動電路設計注意事項

BNC 接頭阻抗匹配:接線中的關鍵技術與注意事項

安全關鍵應用中異構臂核心的軟件注意事項

安全關鍵應用中異構臂核心的軟件注意事項

評論