這是一篇技術干貨快文,能夠快速閱讀完。文章內容是關于如何從命令行獲取和解析參數,包括SystemVerilog本身支持的系統函數和UVM提供的函數封裝,并給出示例代碼和仿真結果。

01 SV系統函數

通過命令行來傳遞參數在實際項目中算是常規操作,比如通過命令行參數來指定Testbench的配置信息等等。在SystemVerilog LRM規范里,命令行提供的仿真參數要求使用加號(+)作為引導,這部分參數可以被驗證環境中的SV代碼通過系統函數訪問到。由于是額外增加的,這些參數也就被稱之為plusargs。

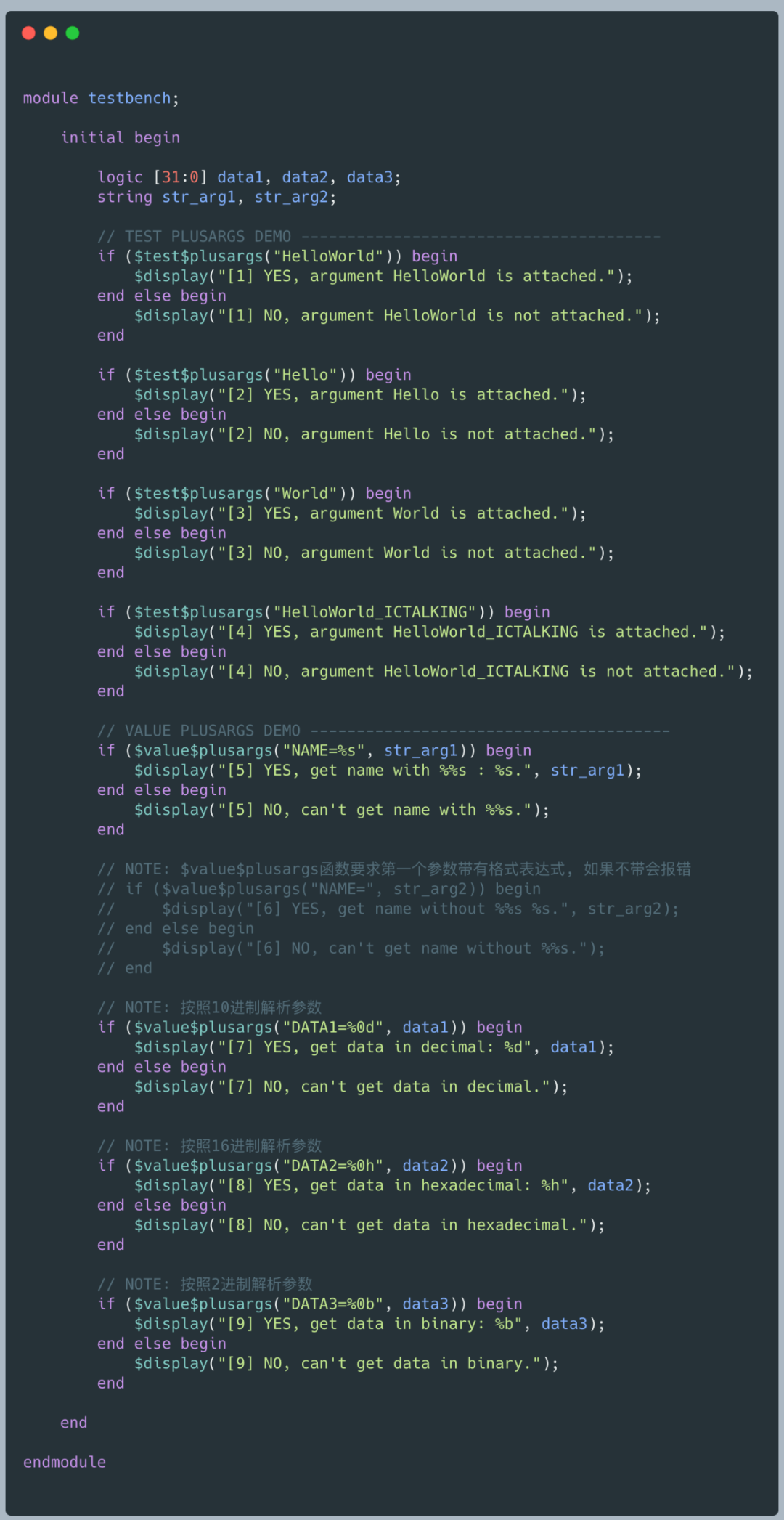

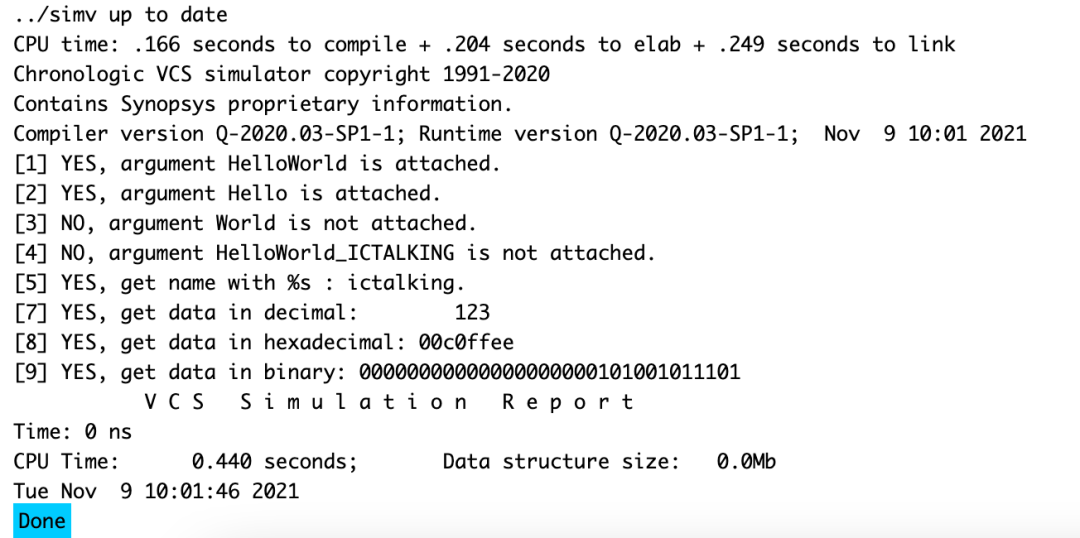

訪問plugargs的系統函數有$test$plusagrs(arg_string)和$value$plusargs(arg_string, target_var)。這兩個系統函數都會根據用戶指定的字符串arg_string,去檢索plusargs列表。如果找到了,則系統函數返回值1;如果沒有找到,返回值0。

其中$test$plusargs(arg_string)可以被用于判斷命令行是否帶了arg_string參數,以此來作為驗證環境的配置開關;$value$plusargs(arg_string, target_var)則是在$test$plusargs的基礎上,增加了對參數arg_string的值的解析:如果匹配到了arg_string,系統函數會將其值賦給target_var;如果沒有找到,則不修改target_var的值。

執行仿真命令:

./simv +vcs+lic+wait +HelloWorld +NAME=ictalking +DATA1=123 +DATA2=C0FFEE +DATA3=101001011101

仿真結果如下: ?

?

?

?02UVM_CMDLINE_PROCESSOR

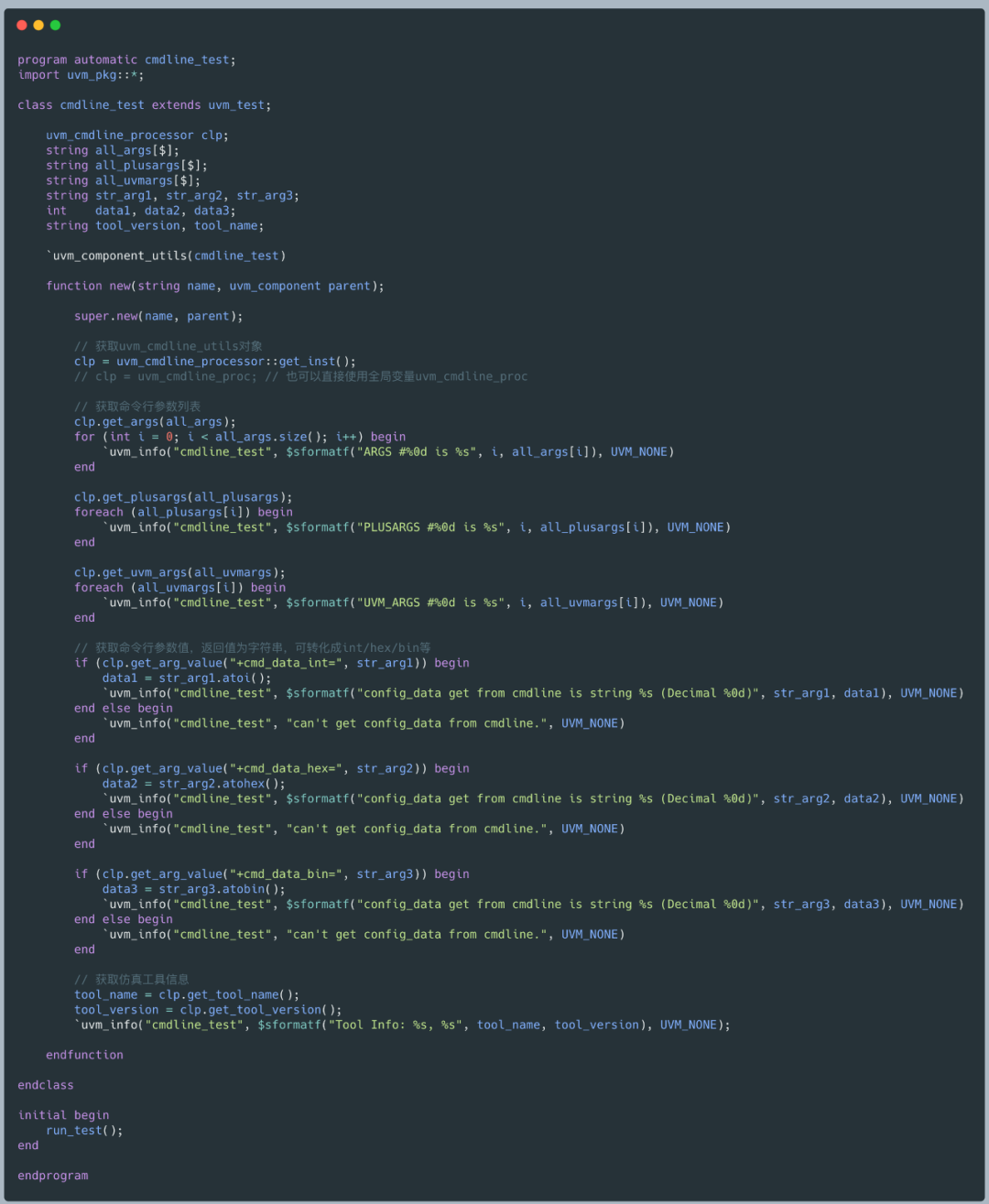

UVM是個非常喜歡搞封裝的類庫。UVM中有個類叫uvm_cmdline_processor,該類繼承自uvm_report_object,再往上就到uvm_object了。uvm_cmdline_processor提供的底層函數接口,說白了跟$test$plusargs和$value$plusargs沒有什么大的區別,不過其中有匹配功能或返回參數列表的函數,對于uvm_root解析UVM配置相關的參數還是很有幫助的。

uvm_cmdline_processor全局單一例化,并提供了get_inst()靜態方法用來獲取對象句柄。UVM默認在初始化的時候,會構造uvm_cmdline_processor的全局對象,叫uvm_cmdline_proc。不過在實際使用中,我們還是可以按照習慣,先聲明一個uvm_cmdline_processor句柄,然后通過get_inst()函數來指向uvm_cmdline_processor對象。

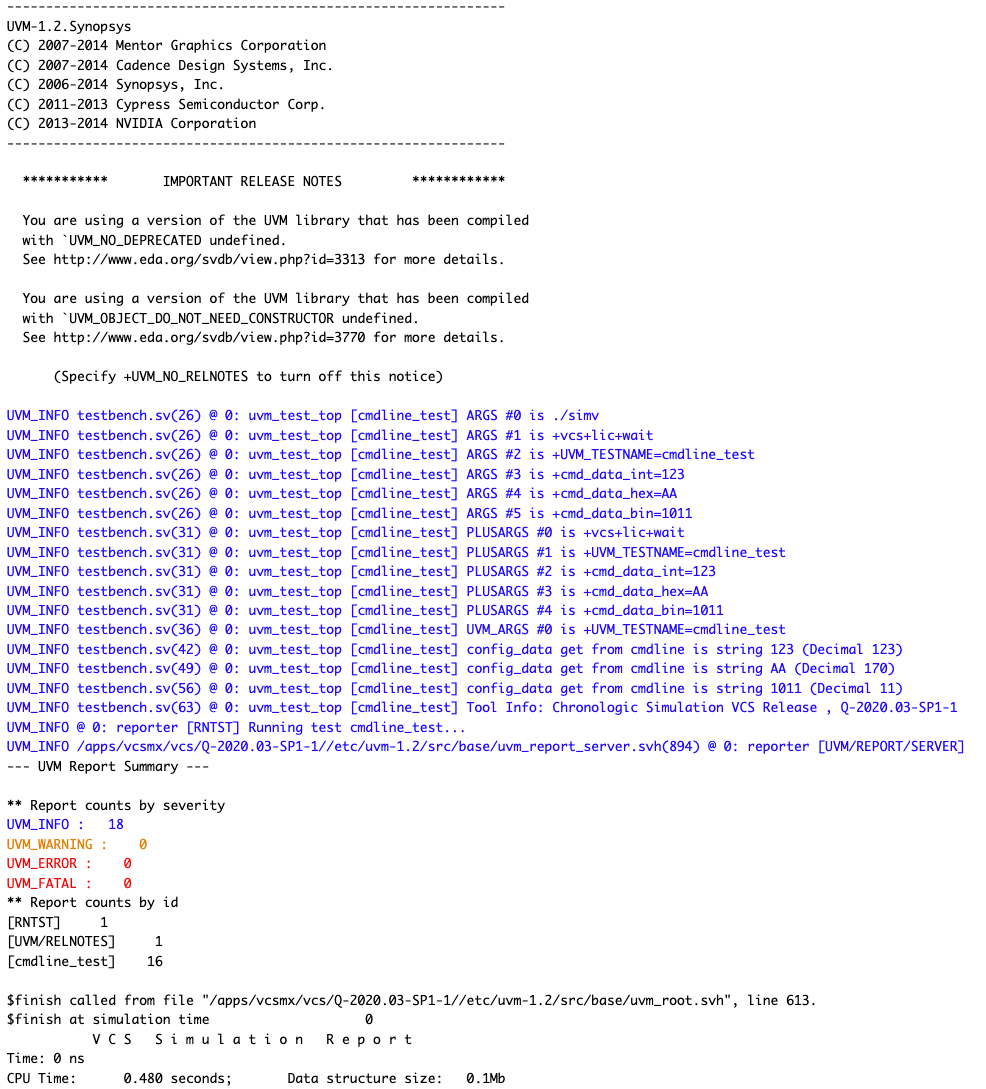

執行仿真命令:

./simv +vcs+lic+wait +UVM_TESTNAME=cmdline_test +cmd_data_int=123 +cmd_data_hex=AA +cmd_data_bin=1011

仿真結果如下:

原文標題:SystemVerilog | UVM | 獲取命令行參數的方法,這些就夠用了

文章出處:【微信公眾號:路科驗證】歡迎添加關注!文章轉載請注明出處。

-

參數

+關注

關注

11文章

1870瀏覽量

34006 -

函數

+關注

關注

3文章

4419瀏覽量

67753 -

UVM

+關注

關注

0文章

183瀏覽量

20075 -

命令行

+關注

關注

0文章

83瀏覽量

10778

原文標題:SystemVerilog | UVM | 獲取命令行參數的方法,這些就夠用了

文章出處:【微信號:Rocker-IC,微信公眾號:路科驗證】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

怎么從命令行執行Momentum

如何從命令行指定程序員?

如何從命令行注入宏?

支持命令行傳遞的參數嗎?

如何獲取其它程序的命令行參數

Shell命令行解釋器簡介

Fcoder從命令行批量轉換為TIFF

LabVIEW命令行調用exe傳入的參數如何獲取

如何從命令行獲取和解析參數

如何從命令行獲取和解析參數

評論