世芯電子完整體現了其在先進FinFET(先進鰭式場效電晶體)的技術組合并且成功完成在臺積電7/6/5納米的流片。除了先進 FinFET的技術組合,世芯的ASIC整體設計解決方案更是涵蓋了全方位一流的IP種類和先進封裝技術。世芯在7/6/5納米的ASIC設計上能特別專注于具有數十億邏輯門數的超大規模/尺寸IC設計。這些先進的IC主要用于人工智能、高性能計算、網絡及存儲應用等領域。

擁有一套經過自身驗證的芯片設計流程和法則,是世芯成功的關鍵。它不僅能優化功耗、性能和面積的設計,同時還能符合客戶嚴格的流片計劃要求。世芯完整的7/6/5納米設計能力包括大規模芯片設計里必要的分區和簽核、測試設計流程,以及一套涵蓋了全面系統協同設計簽核的中介層/基板設計的完整2.5D封裝設計流程。

世芯的創新封裝服務也涵蓋信號/電源仿真及熱仿真(SI/PI),能提供即插即用的流片后解決方案,以減少基板層和由此產生的材料成本。這樣產生的7/6/5納米IC具有更精確的功率和熱估算流程,能避免流片后的失敗,在高功率設計中尤其關鍵。

世芯完整的5納米“設計到交付”方法側重于最大限度地縮短設計周期。其中的實體設計像是芯粒(Chiplet)技術平臺、高性能計算IP組合含世芯的D2D APLink IP、IP子系統集成服務,以及最新的2.5D異構封裝技術等。

“世芯的優勢一直是先進工藝芯片設計。在7納米系統芯片項目的設計流片量產上,我們與客戶再次合作并取得了100%的流片成功率。”世芯總裁兼首席執行官沈翔霖表示,“我們的設計和驗證法則乃經過嚴格認證,亦源于我們企業文化一貫秉持的核心服務理念”。

審核編輯 :李倩

-

芯片設計

+關注

關注

15文章

1155瀏覽量

56679 -

封裝技術

+關注

關注

12文章

599瀏覽量

69303 -

FinFET

+關注

關注

12文章

260瀏覽量

92259

原文標題:先進FinFET工藝的多項流片鞏固了世芯電子的業界領先地位

文章出處:【微信號:gh_81c202debbd4,微信公眾號:世芯電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

重磅研究:7nm FinFET 性能優化的隱藏密碼 —— 柵極與鰭片間距調控

Cadence公司成功流片第三代UCIe IP解決方案

國產芯片真的 “穩” 了?這家企業的 14nm 制程,已經悄悄滲透到這些行業…

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產業的前沿技術

瞻芯電子榮獲上海市企業技術中心認定

東芯半導體入圍2025全球電子成就獎和金輯獎評選

芯動科技亮相2025世界半導體大會

京信通信鞏固室內無線通信市場領先地位

行芯科技揭示先進工藝3DIC Signoff破局之道

揚杰科技三個工廠同時入選省先進級智能工廠名單

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實現流片成功

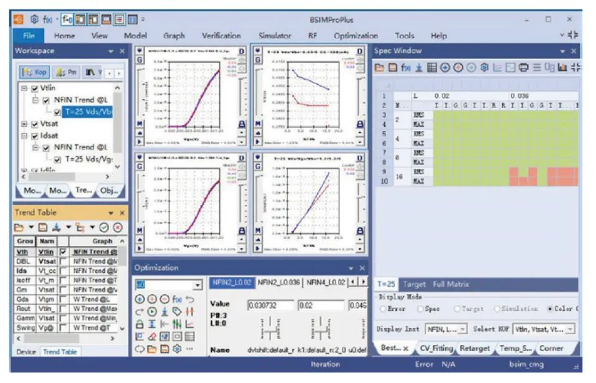

概倫電子先進器件建模平臺BSIMProPlus介紹

先進FinFET工藝的多項流片鞏固了世芯電子的業界領先地位

先進FinFET工藝的多項流片鞏固了世芯電子的業界領先地位

評論