在計算機的一生中,CPU壞的概率極小。正常使用的情況下,就算其他主要的電腦配件都壞了,CPU都不會壞。

CPU出現損壞的情況,多數都是外界原因。最主要的就是長期在超頻下工作,且散熱性差,引起電子熱遷移導致的損壞。

現在的個人電腦的更新換代基本不是由于CPU損壞才換的,主要是因為軟件不斷的升級、越來越大,造作系統的垃圾越來越多導致卡頓,讓你無法忍受,才換電腦的。

CPU在出廠之前,是經過非常嚴格的測試的,甚至在設計之初,就要考慮測試的問題。可以從pre-silicon、post-silicon和硅的物理性質等方面來解釋這個問題。

1、CPU被做成產品之前被檢出缺陷

這一個階段也就是芯片tape out之后,應用到系統或者產品之前。

事實上,在現在的芯片設計中,在設計之初就已經為芯片的制造,測試,以及良率做考慮了。保證這一步能檢測出芯片的缺陷,主要是DFT+ATE來保證。當然也有一些公司會做DFD和DFM。

DFT = Design For Test

DFD = Design For Debug

DFM = Design for Manufacture

DFT指的是在芯片的設計階段即插入各種用于提高芯片可測試性(包括可控制性和可觀測性)的硬件電路,通過這部分邏輯,生成測試向量,使測試大規模芯片變得容易的同時,盡量減少時間以節約成本。

DFT--可測性設計,按流程劃分,依然屬于設計階段(pre-silicon),只不過是為測試服務的。

而ATE(Auto Test Equipment )則是在流片之后,也就是post-silicon階段。

ATE測試就是為了檢查制造缺陷過程中的缺陷。芯片測試分兩個階段,一個是CP(Chip Probing)測試,也就是晶圓(Wafer)測試。另外一個是FT(Final Test)測試,也就是把芯片封裝好再進行的測試。

CP測試的目的就是在封裝前就把壞的芯片篩選出來,以節省封裝的成本。同時可以更直接的知道Wafer 的良率。CP測試可檢查fab廠制造的工藝水平。現在對于一般的wafer成熟工藝,很多公司多把CP給省了,以減少CP測試成本。具體做不做CP測試,就是封裝成本和CP測試成本綜合考量的結果。

一片晶圓越靠近邊緣,die(一個小方格,也就是一個未封裝的芯片)出問題的概率越大。測出壞的芯片根據不同壞的情況不同,也會分bin,最終用作不同的用途。

所以在芯片被做成成品之前,每一片芯片都是經過量產測試才發貨給客戶的。

2、做成成品出廠以后,在使用過程中壞掉了

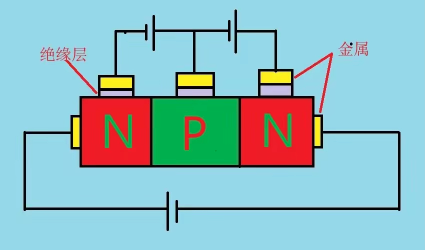

就單個晶體管來看,在正常使用過程中,真的那么容易壞掉嗎?其實不然。

硅由于物理性質穩定,禁帶寬度高(1.12ev),而且用作芯片的硅是單晶硅,也很難發生化學反應,在非外力因素下,晶體管出問題的概率幾乎為零。

即使如此,芯片在出場前,還要經過一項測試,叫“老化測試”,是在高/低溫的爐里經過 135/25/-45攝氏度不同溫度以及時間的測試,以保證其穩定性和可靠性。

根據芯片的使用壽命根據浴盆曲線(Bathtub Curve),分為三個階段,第一階段是初期失效:一個高的失效率。由制造,設計等原因造成。第二階段是本征失效:非常低的失效率,由器件的本征失效機制產生。第三個階段:擊穿失效,一個高的失效率。而在計算機正常使用的時候,是處在第二階段,失效的概率非常小。

但是,耐不住有上百億個晶體管啊。..。.. 所以,還是有壞的概率的。

就算是某個晶體管壞了,芯片設計中會引入容錯性設計,容錯性設計又可以從軟件和硬件兩個方面來實施。

比如多核CPU可以通過軟件屏蔽掉某個壞的核心,ATE測試后根據不同缺陷分bin的芯片,也會用在不同的產品上,畢竟流片是十分昂貴的。比如Intel的i3,i5,i7等。當然,也不是所有的i3都是i5、i7檢測出來的壞片。

再比如存儲器中一般存在冗余的信號線和單元,通過檢查發現有問題的單元,從而用冗余的模塊替換有缺陷的模塊,保證存儲的正常使用。

比如下面橙色的為冗余的memory,紅色的是壞的memory,我們便可以通過算法把紅色memory的地址映射到橙色備用的一個memory上。

芯片測試是極其重要的一環,有缺陷的芯片能發現的越早越好。如果把壞的芯片發給客戶,不僅損失巨大,對公司的聲譽也會造成負面的影響。

在芯片領域有個十倍定律,從設計--》制造--》封裝測試--》系統級應用,每晚發現一個環節,芯片公司付出的成本將增加十倍!!!

高質量的測試是由DFT,ATE,diagnosis,EDA等多方面協作完成的,尤其在超大規模集成電路時代,測試變得越來越難,越來越重要,其開銷在整個芯片流程中也占有很大的比重。芯片作為工業皇冠上的明珠,所有電子系統的大腦,是萬萬不能出問題的!

原文標題:CPU 為什么很少會壞?

文章出處:【微信公眾號:FPGA開源工作室】歡迎添加關注!文章轉載請注明出處。

-

芯片

+關注

關注

463文章

54010瀏覽量

466069 -

封裝

+關注

關注

128文章

9249瀏覽量

148624 -

晶體管

+關注

關注

78文章

10396瀏覽量

147757

原文標題:CPU 為什么很少會壞?

文章出處:【微信號:leezym0317,微信公眾號:FPGA開源工作室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

MUN5136數字晶體管技術解析與應用指南

電壓選擇晶體管應用電路第二期

晶體管的定義,晶體管測量參數和參數測量儀器

英飛凌功率晶體管的短路耐受性測試

0.45-6.0 GHz 低噪聲晶體管 skyworksinc

多值電場型電壓選擇晶體管結構

晶體管光耦的工作原理

下一代高速芯片晶體管解制造問題解決了!

無結場效應晶體管詳解

什么是晶體管?你了解多少?知道怎樣工作的嗎?

晶體管很容易壞掉嗎

晶體管很容易壞掉嗎

評論