隨著5G、人工智能、物聯網、汽車電子等新興應用的崛起,ADC作為信號鏈核心的地位仍在提升。距離我們上一次挖掘ADC新品,已經過去了不少時日。每一次行業內新的ADC產品發布都能帶給我們不少的驚喜,這一次也不會例外。

ADI ADC新品AD4134

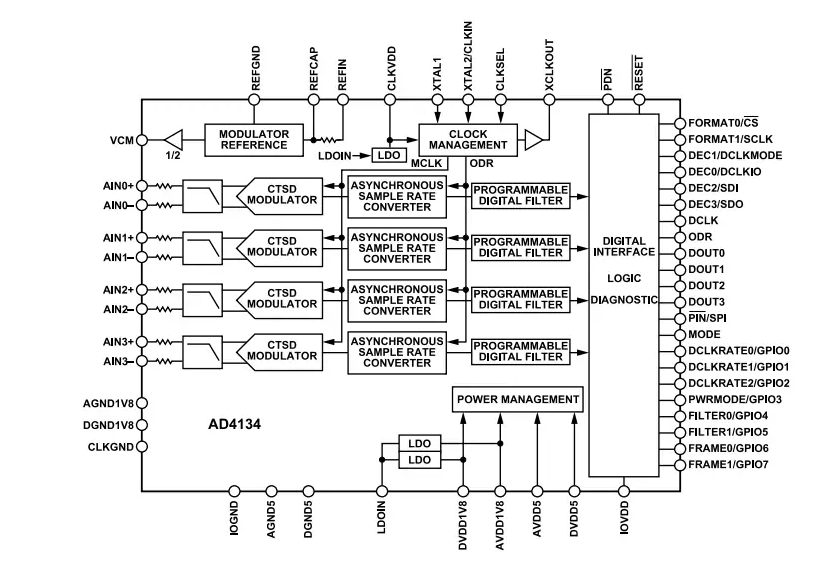

AD4134,一款24位的4通道同步采樣無混疊ADC,主要針對航空航天、醫療設備、工業自動化以及儀器儀表測量領域應用開發。該新品最大的特點就是能有效抑制ADC混疊頻帶附近的信號。

ADI ADC新品AD4134

AD4134,一款24位的4通道同步采樣無混疊ADC,主要針對航空航天、醫療設備、工業自動化以及儀器儀表測量領域應用開發。該新品最大的特點就是能有效抑制ADC混疊頻帶附近的信號。

(圖源:ADI)

首先看看它的抗混疊能力。AD4134采用了連續時間Σ-Δ(CTSD)調制方案,消除了一般設計里所需的位于Σ-Δ調制器之前的開關電容電路采樣,放寬了對ADC輸入驅動的要求。CTSD架構本身就能抑制ADC混疊頻帶附近的信號,并且不需要復雜的外部抗混疊濾波器。在AD4134高性能模式下,抗混疊抑制典型值高達102.5dB。

高抗混疊之外,它的其他關鍵性能也是毫無爭議的行業一流。其失調誤差漂移不超過0.9 μV/C,增益漂移不超過2ppm/℃,積分非線性為2ppm,在1kHZ的輸入信號音下總諧波失真典型值為-120dB。這些特性使得系統性性能得到了大幅改善,在溫度、壓力、振動、沖擊等各類傳感器中都能發揮出出色的實力。

在AD4134的四個通道中,每個通道均有CTSD調制器和數字抽取與濾波路徑,能同時對四個獨立的信號源采樣。每個信號測量支持391.5 kHz的最大輸入帶寬,四個信號測量之間實現了嚴密的相位匹配。

AD4134集成了異步采樣速率轉換器,能利用插值和重采樣技術精準地控制抽取率,進而控制ODR。AD4134支持從0.01 kSPS到1496 kSPS的寬范圍ODR頻率,調整分辨率小于0.01 SPS。異步采樣速率轉換器不再需要將數字后端的高頻低抖動主時鐘路由到各ADC,因此可簡化中等帶寬數據采集系統的時鐘分配要求。

AD4134還支持靈活且獨立的數據接口,既可充當總線主機,也可充當從機,具有各種時鐘選項,支持多種通信總線協議。而在封裝上,器件采用8 mm×8 mm、56引腳引線框架芯片級封裝。

TI ADC新品ADS7067

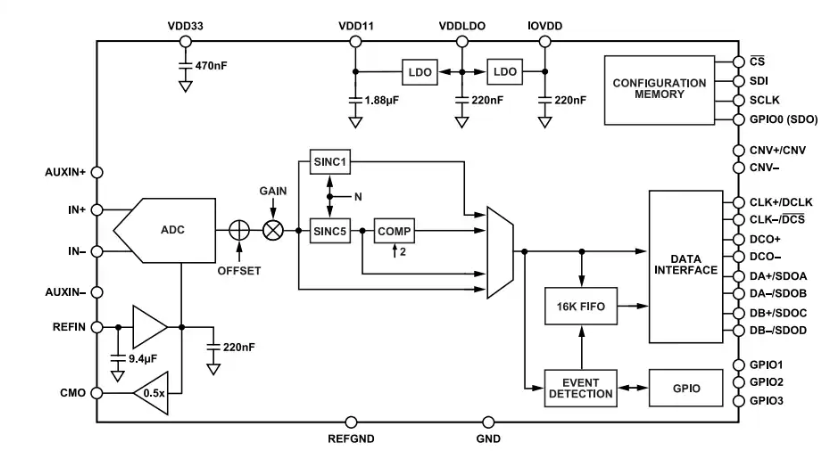

在推出了幾款汽車類應用的同步采樣ADC后,這一次TI最新推出的ADS7067是具有GPIO和SPI的八通道16位SAR ADC。

(圖源:TI)

該ADC在保證了一流的同類產品性能的前提下,大幅減少了外部組件,對減小系統整體的尺寸有相當大的助力。ADS7067具有集成的無電容基準和基準緩沖器,因此無需較多的外部組件,其本身也只有1.62mm×1.62mm,可以大幅減小整體解決方案尺寸。

ADS7067本身也具備出色的交/直流性能,90dB的SNR,-100dB的THD,800kSPS的采樣率能做到無延遲輸出,同時在內部改善了失調電壓和漂移。內置的失調電壓校準功能,可在系統的寬工作范圍內提高精度,可編程均值濾波器可實現更高的分辨率測量。ADS7067 的八個通道可以單獨配置為模擬輸入、數字輸入或數字輸出,以實現更小的系統尺寸,并簡化混合信號反饋和數字控制的電路設計。

ADS7067具備增強型的SPI數字接口,擁有60MHz的高速,能夠支持器件以較低的時鐘速度實現高數據吞吐量。這種配置進一步簡化了整個器件的布局并能降低成本。晶圓級芯片封裝讓這個新ADC能適應任何空間受限的應用。

小結

這兩款新品一個顯著抑制ADC混疊,一個大幅降低系統尺寸,反映出了ADC這個核心器件的發展方向,如何在大幅提高數據吞吐量和帶寬的同時盡可能減小功耗和尺寸,是每一個ADC廠商都在攻克的課題。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

ADI

+關注

關注

151文章

46104瀏覽量

277350 -

ti

+關注

關注

114文章

8068瀏覽量

219256 -

adc

+關注

關注

100文章

7511瀏覽量

556006

發布評論請先 登錄

相關推薦

熱點推薦

泡沫起升儀模擬前端設計:微弱信號放大與抗混疊濾波電路

泡沫起升儀的模擬前端作為傳感信號的“第一道處理關口”,承擔著將探頭捕捉的原始信號轉化為可用數據的關鍵使命。其中,微弱信號放大與抗混疊濾波電路是核心組成部分,二者協同工作,既讓微弱的傳感信號 “清晰

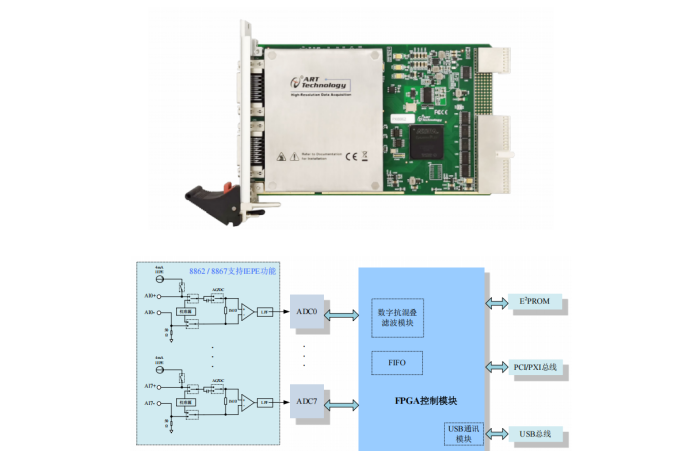

簡儀科技發布兩款高規格同步數據采集模塊JY-5321A/5322A

JY-5321A/5322A是兩款高規格同步采集模塊,核心參數與功能配置兼具精度與擴展性。模塊DC精度達220 ppm,搭載18位ADC,每通道最高采樣率1 MS/s;配備25 kHz/220 kHz 軟件可選抗混

納祥科技NX9068,PIN TO PIN CS5368的8路差分I2S輸入ADC,自帶TDM接口模式

系統設計。它支持采樣、模數轉換和抗混疊濾波,能夠以每通道高達216kHz的采樣率,將所有8個通道的輸入轉換為24位串行數據,具備114dB動態范圍、-105dBTH

高速adc,類比高精度ADC芯片ADX3202AQFN32詳解

作為抗混疊濾波器,大大降低了工程師的設計負擔。多數產品還集成了內部基準源和可編程增益放大器,進一步簡化了外圍電路設計。

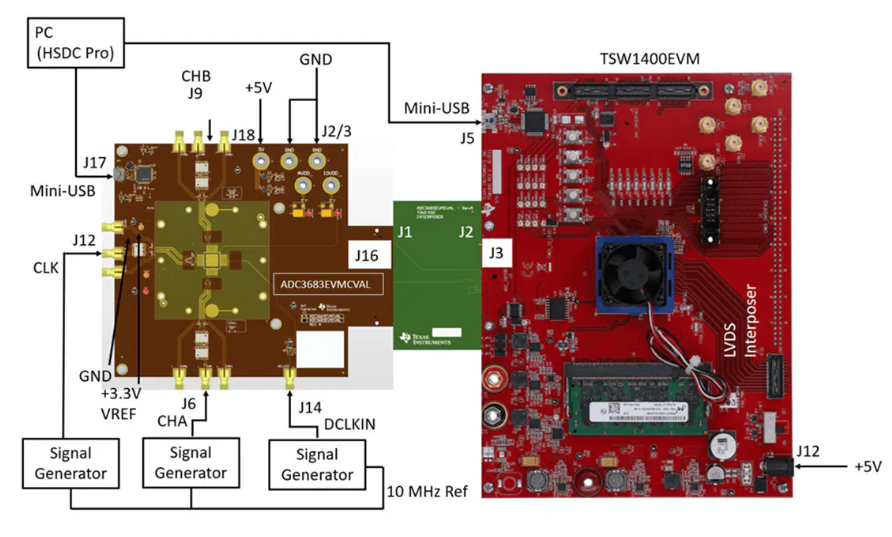

ADC3683EVMCVAL評估模塊技術解析與應用指南

號(LVDS)接口輸出數字數據。串行化LVDS接口支持高達1Gbps的輸出速率。Texas Instruments ADC36XXQML-SP可使用內部抽取濾波器以過采樣+抽取模式運行,以提高動態范圍并放松外部抗混

什么是頻率混疊?數據采集中的混疊如消除?

頻率混疊是指當最高信號頻率高于采樣頻率的一半(即不滿足奈奎斯特定理)時,高頻分量會被錯誤地映射到低頻區,導致重建后的波形出現虛假低頻分量,信號出現失真,與真實信號無法區分。

Analog Devices Inc. AD4134四通道模數轉換器數據手冊

Σ-Δ (CTSD) 調制方案。AD4134消除了Σ-Δ調制器之前傳統上所需的開關電容器電路采樣,從而放寬了ADC的輸入驅動要求。此外, CTSD架構還固有地抑制ADC混疊頻段周圍的信

PCB疊層設計避坑指南

第3層作為高速信號層時,上下需 設置地平面 。

2、電磁兼容性(EMC)

合理的疊層結構能 減少60%以上的串擾 。多個地平面層能有效減小PCB板阻抗,降低共模EMI。

3、機械穩定性

疊層必須 保持

發表于 06-24 20:09

Analog Devices Inc. AD4080差分SAR ADC數據手冊

高性能,信噪和失真 (SINAD) 比 >90dBFS,因此可用于各種精密、寬帶寬數據采集應用。對于不需要AD4080最低延遲的應用,可以通過應用過采樣以及集成數字濾波和抽取來減少噪聲和降低輸出數據速率,從而簡化輸入抗混

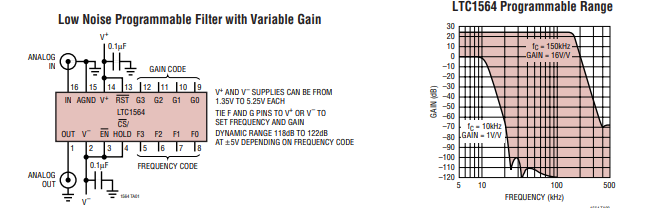

LTC1564 10kHz至150kHz數字控制式抗混疊濾波器和4位P.G.A技術手冊

LTC1564 是一款新型連續時間濾波器,適用于抗混疊、重構和其他頻帶限制應用。使用該器件無需具備其他模擬組件或濾波器專門知識。LTC1564 具有一個模擬輸入引腳和一個模擬輸出引腳。截止頻率 (f

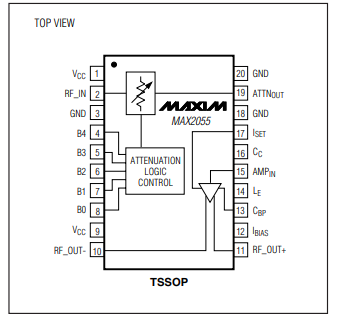

MAX2055數字控制、可變增益、差分ADC驅動器/放大器技術手冊

分輸出放大器,可以省去一個外部變壓器,或是改善變壓器耦合電路的偶階失真性能,因此降低了對ADC之前的抗混疊濾波器的要求。MAX2055的設計

求助,關于ADXL382混疊和ODR=32Khz時的輸出噪聲問題求解

1、ODR=16KHz參數配置。

當振動臺頻率為8100Hz時,發生混疊,頻率混疊為7900Hz。如何解決混

發表于 04-16 08:10

使用AD9122四倍插值的情況下,輸出20MHz的寬帶信號偶爾會出現頻譜混疊,怎么解決?

你好,在使用AD9122四倍插值的情況下,輸出20MHz的寬帶信號偶爾會出現頻譜混疊,這種該怎么解決呢

發表于 04-15 06:50

天合光能鈣鈦礦晶體硅疊層技術再破世界紀錄

今日,位于天合光能的光伏科學與技術全國重點實驗室宣布鈣鈦礦晶體硅疊層技術再破紀錄,其自主研發的210mm大面積鈣鈦礦/晶體硅兩端疊層太陽電池,經德國夫瑯禾費太陽能研究所下屬的檢測實驗室

CM2248完美替代兼容AD760

CM2248 是一款 16 位、8 通道同步采樣模擬數據采集系統(DAS)。各通道均內置模擬輸入鉗位保護、二階抗混疊濾波器、跟蹤保持放大器、16 位 SAR ADC,內置了靈活的數字濾

發表于 04-01 10:51

繼續挖掘ADC新品,抗混疊與降低尺寸再革新

繼續挖掘ADC新品,抗混疊與降低尺寸再革新

評論