一、如何知道器件所支持的時鐘頻率?

舉例說明:

DDR3 型號: MT41J256M16xx-125

(記住這個常用型號,后文還是以此型號講解)

FPGA 型號: XC7K325TFFG900-2 (常用FPGA型號)

datasheet : MT41J512M8RH-125:E(DDR3)、DS182(FPGA)

1.1DDR3芯片的帶寬、位寬和最大IO時鐘頻率

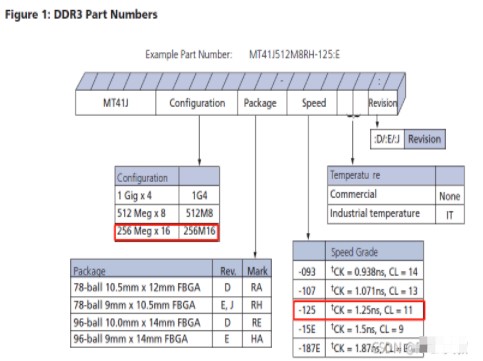

翻看DDR3對應型號MT41J256M16XX-125的數據手冊,可以看到:

圖1. DDR3 Part Numbers

IO時鐘頻率:

根據Part Number 中的“-125”我們就可以找到圖中的tCK = 1.25ns,就可以算出芯片支持的最大IO時鐘頻率:1/1.25ns = 800Mhz;此處的IO時鐘頻率也就是DDR3的頻率;

位寬:

根據Part Number 中的“256M16”我們可以找到圖中2所指出的地方,這里的16是代表芯片的數據位寬是16位(也就是16根數據線)。

注意:

1. 當一個FPGA上掛多個DDR,如4片ddr3,位寬則會相應增大;16*4 = 64bit,再乘以DDR3的突發長度BL=8;那么程序設計里DDR3的讀寫位寬就變成了16*4*8=512bit; (這里留個印象,再后文IP例化及程序設計部分還會講到,到時候對應起來看更容易理解)

2. 明明是512M的DDR,為什么又寫成256M呢?因為256M16是16根數據線16bit,對應過來就是2個byte;256M *16bit = 512MByte; 一般大B 指的是Byte,小b指的是bit;

帶寬:

由于是DDR方式傳輸數據(上升和下降沿都傳輸),所以芯片的一根數據線上的傳輸速率 = 2*800Mhz = 1600MT/s。其實就是1600Mbit/s;

帶寬就是16根數據線同時傳輸的數據速率 = 1600Mbit/s x 16 = 25600Mbit/s = 3200Mbyte/s = 3.125GByte/s

???????1.3FPGA所支持的最大頻率

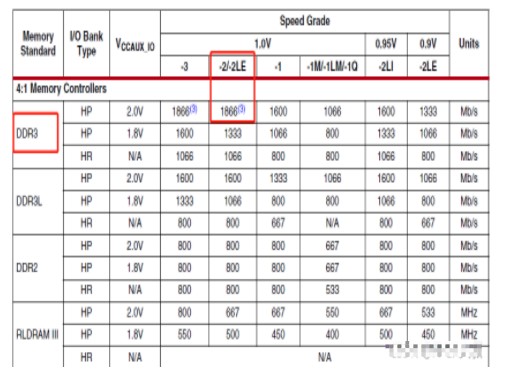

翻看k7數據手冊ds182可以看到:

圖2. k7系列支持的DDR速率

k7系列的FPGA所支持的DDR3傳輸速率高達1866MT/s,這里需要跟硬件工程師具體了解了解,實際使用最高還是1600MT/s,對應頻率= 1600M/2= 800Mhz;

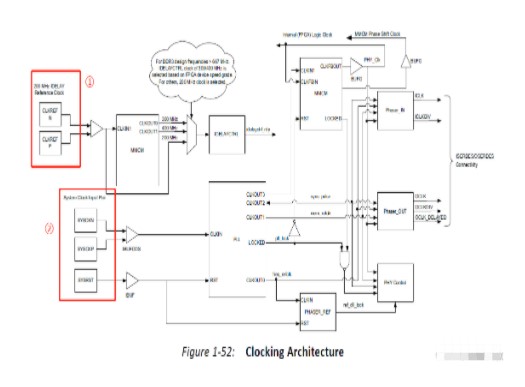

???????二、時鐘結構

圖3. 時鐘結構

從圖中,我們可以看到,主要有兩個時鐘:

①參考時鐘 : 必須為200Mhz

②系統時鐘 : 系統輸入時鐘

那么對應到MIG IP核又是如何定義的呢?繼續往下走

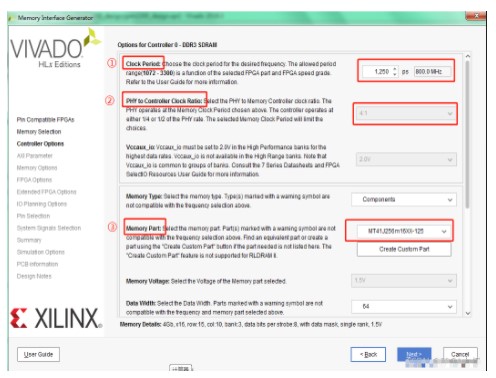

三、MIG IP核的時鐘:

3.1clock period時鐘

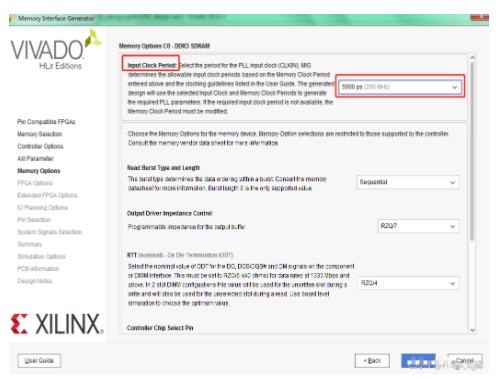

圖4. Clock Period

這里①Clock Period設置的參數就是 MIG 的PHY 接口對DDR3的時鐘,也就是DDR3芯片實際跑的IO時鐘頻率,它由system clock(主時鐘)倍頻而來,最大頻率不能超過DDR3 和MIG支持的最大頻率中的最小值(前文已講解如何查看器件所支持的最大頻率)。

對應到MIG 例化的信號:

.ddr3_ck_p (ddr3_ck_p ), //連接DDR管腳 .ddr3_ck_n (ddr3_ck_n ),

3.2 ui_clk

圖4下面②有個4:1,說明MIG 輸出到app接口上的時鐘ui_clk = 800M/4=200M ,即到時我們在寫RTL邏輯代碼時操作MIG核時,用的就是這個200M時鐘;

注:當我們選擇800M時鐘時,下面的PHY to Controller Clock Ratio 只能選擇4:1;對應過來ui_clk最大為200M;當我們clock period時鐘選擇小于800M時,這里可以選擇4:1 / 2:1;

3.3 input clock period

圖5. input clock period

input clock period 對應的時鐘就是MIG核的系統時鐘,由PLL/MMCM輸入;對應到例化代碼就是:

.sys_clk_i (sys_clk_i ), //系統時鐘輸入

我們配置MIG核時選擇多少M時鐘,那么這里就要輸入多少M

注:

推薦選擇200Mhz,因為參考時鐘也是200Mhz,配置的時候參考時鐘可以直接使用系統時鐘,減少端口信號

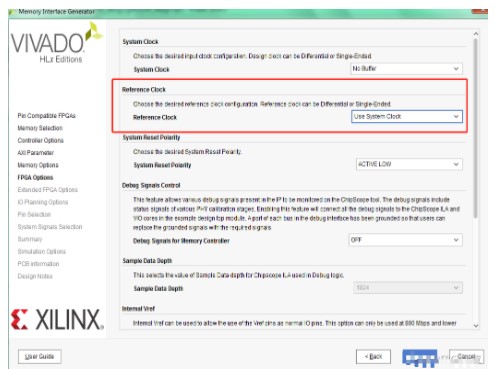

3.4 Reference clock

圖6.參考時鐘

參考時鐘必須為200Mhz!

當我們系統時鐘為200M時,參考時鐘就可以直接使用系統時鐘(use system clock)

???????四、行業術語

1. 核心頻率:核心頻率就是DDR物理層(PHY)IO時鐘頻率,對應到MIG就是第一個配置的“CLOCK PERIOD”,上文我們選擇的是800Mhz

2. 工作頻率:核心頻率* 2 (上下沿)= 1600M核心頻率* 2 = 1600M

3. 傳輸速率:核心頻率* 2 = 1600MT/s

4. 帶寬:傳輸速率*位寬 = 1600M * 16 = 25600Mbit/s = 3200Mbyte/s = 3.125GByte/s

審核編輯:湯梓紅

-

FPGA

+關注

關注

1660文章

22416瀏覽量

636614 -

芯片

+關注

關注

463文章

54024瀏覽量

466390 -

Xilinx

+關注

關注

73文章

2200瀏覽量

131198

發布評論請先 登錄

TI SN74SSQEA32882:DDR3/DDR3L注冊式DIMM的理想時鐘驅動器

探索SN74SSQEB32882:DDR3內存的高效時鐘驅動解決方案

探索 SN74SSQEC32882:DDR3 注冊 DIMM 的理想時鐘驅動器

Texas Instruments TS3DDR3812:DDR3應用的理想12通道開關解決方案

HummingBird EV Kit - DDR3 引腳不匹配是怎么回事?

基于FPGA的DDR控制器設計

DDR200T中的DDR3的使用配置

FPGA搭建DDR控制模塊

用FPGA實現DDR控制模塊介紹

AD設計DDR3時等長設計技巧

AD設計DDR3時等長設計技巧

DDR3 SDRAM配置教程

Xilinx FPGA平臺DDR3設計保姆式教程(二)

Xilinx FPGA平臺DDR3設計保姆式教程(二)

評論