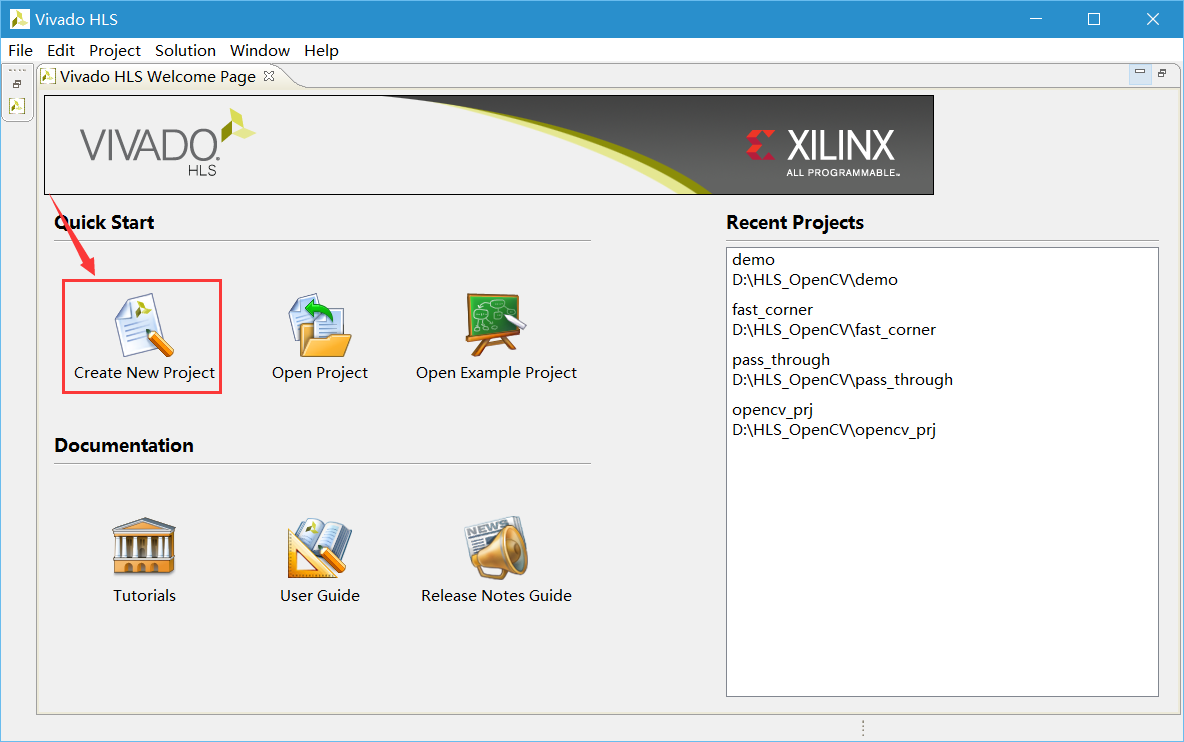

先從運(yùn)行一個(gè)創(chuàng)建一個(gè)項(xiàng)目開始吧。

首先打開Vivado設(shè)計(jì)套件Vivado HLS 2015.4;

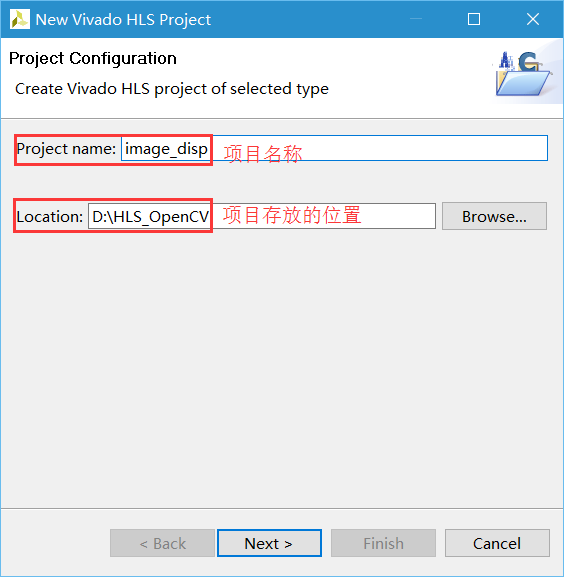

輸入項(xiàng)目的名稱和存放的位置;

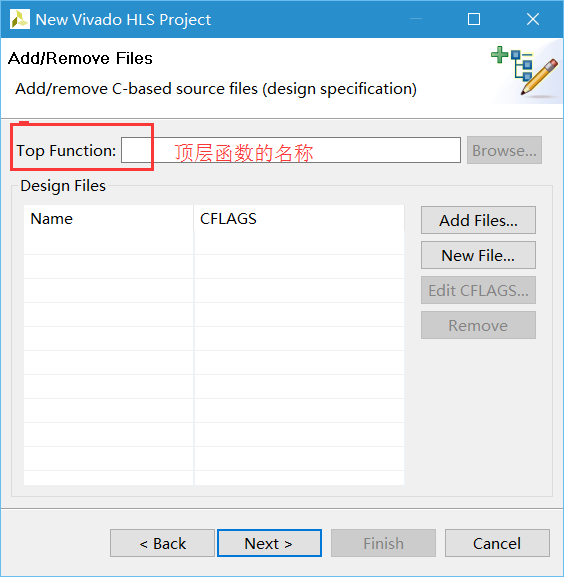

點(diǎn)擊下一步,輸入設(shè)計(jì)頂層函數(shù)的名稱,接著下一步;

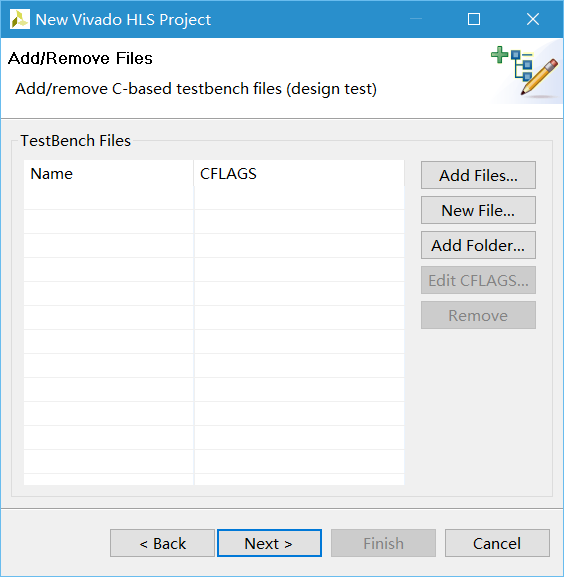

暫時(shí)不需要填寫,直接下一步;

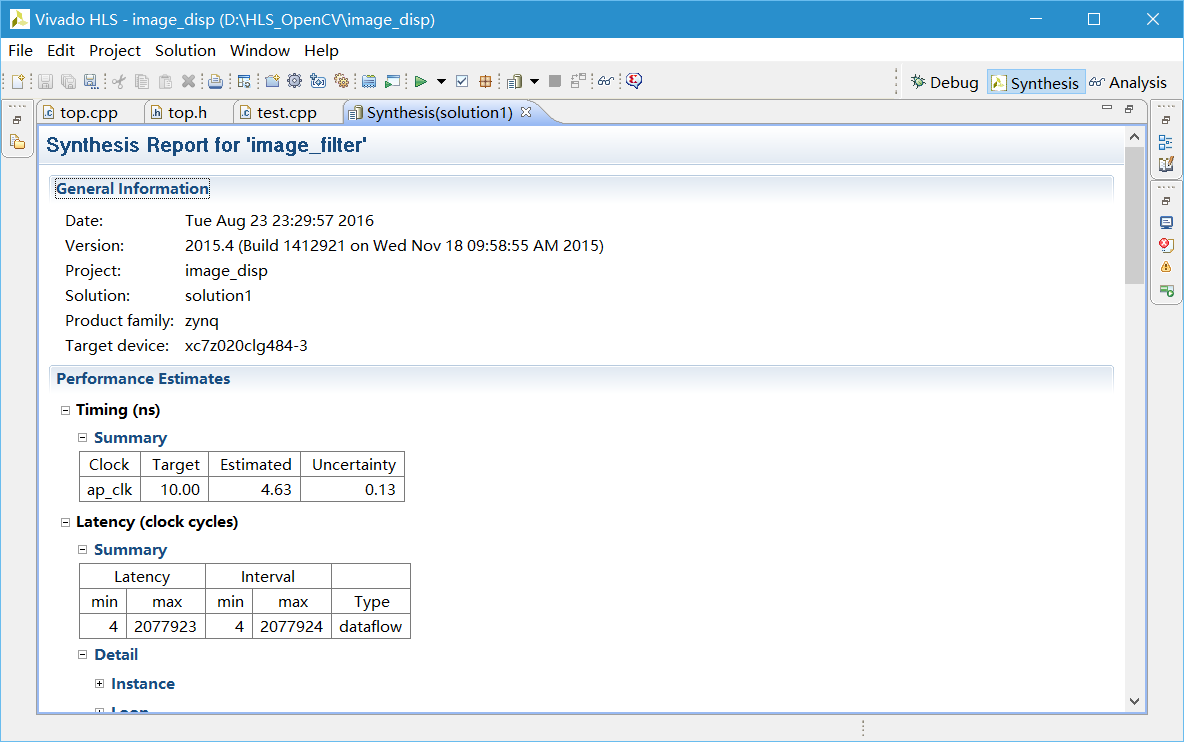

解決方案的名字默認(rèn) (solution1)就好, 時(shí)鐘周期根據(jù)需要自己設(shè),這里我設(shè)(10 ns), 時(shí)鐘的不確定性一般為12.5%,接著選擇器件,最后“finish”。

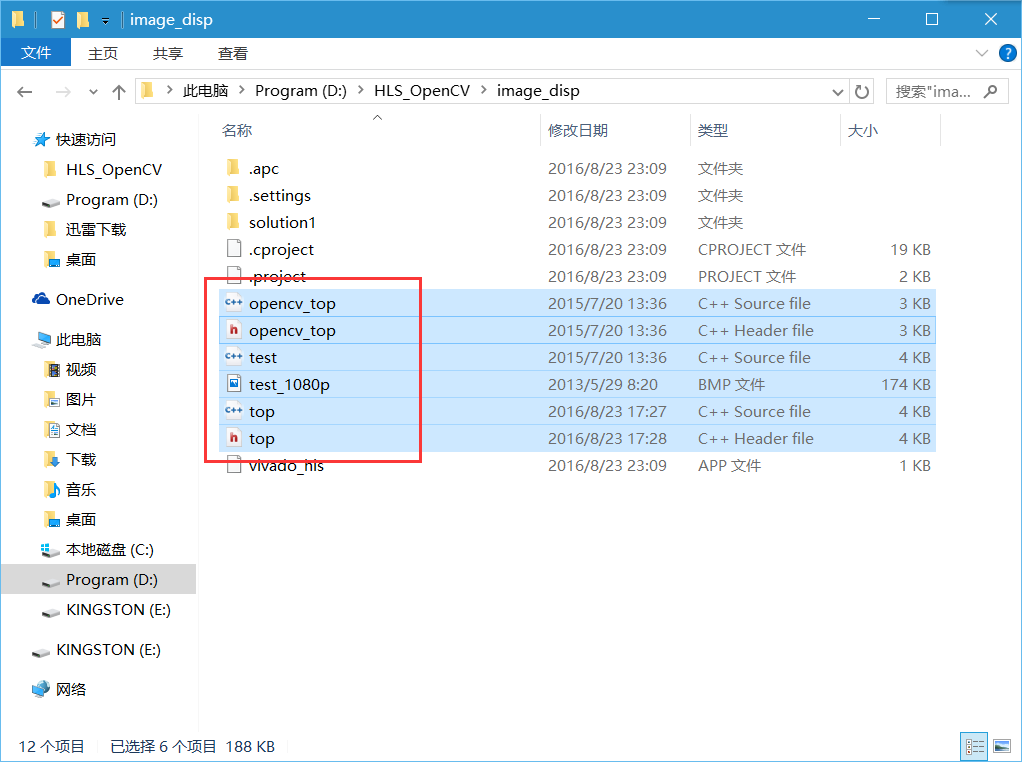

將該例程的設(shè)計(jì)文件和testbench全部復(fù)制到剛才創(chuàng)建的項(xiàng)目目錄下:

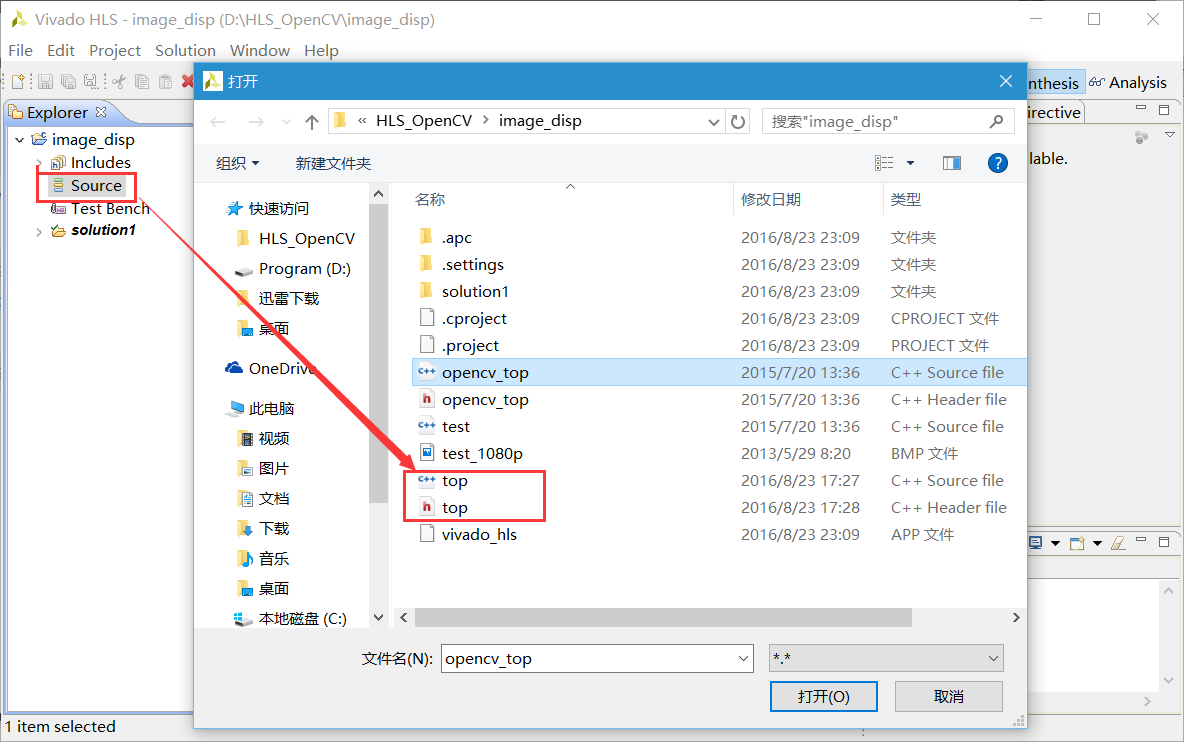

在設(shè)計(jì)資源窗口右擊“Source”,添加設(shè)計(jì)文件;

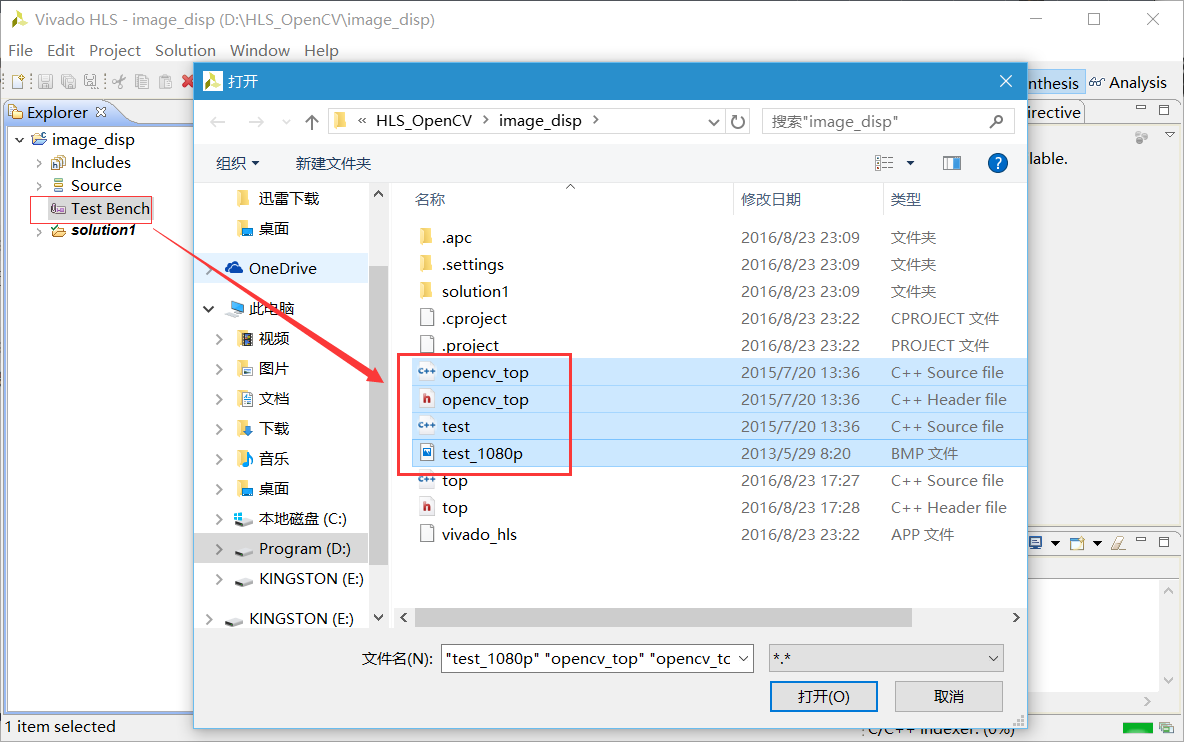

再接著右擊“Test Bench”,添加文件;

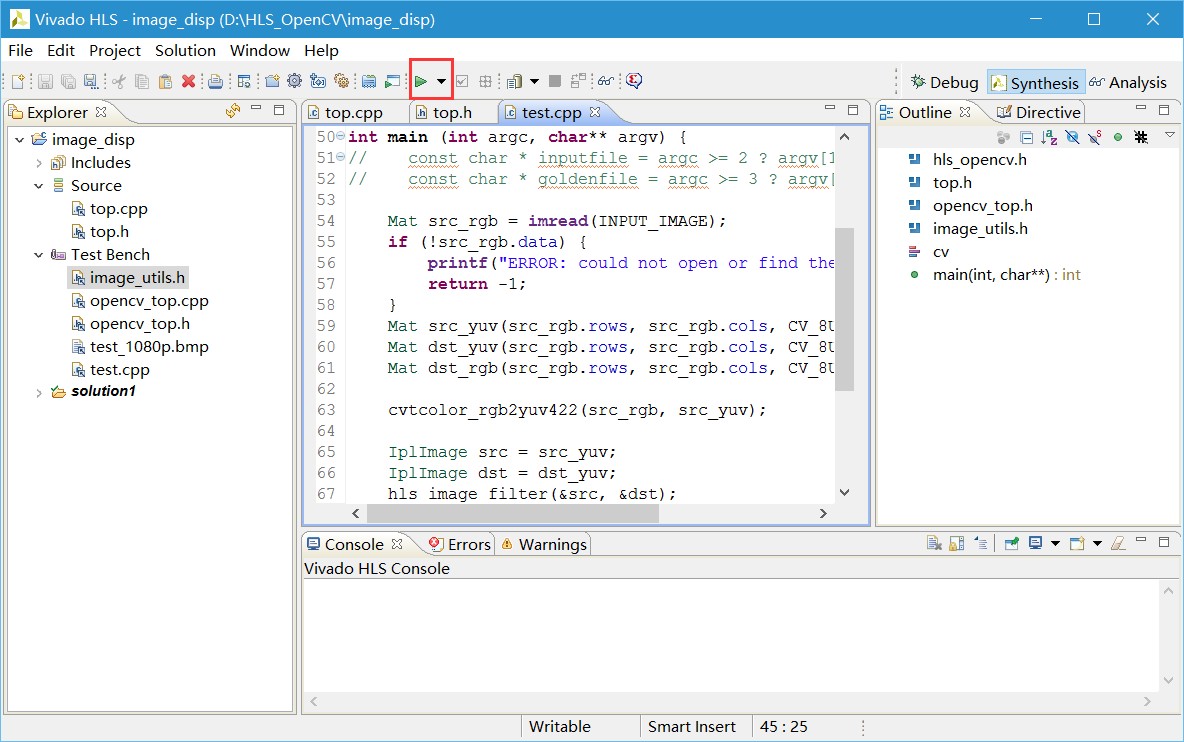

至此,項(xiàng)目建設(shè)完成。接著進(jìn)行綜合仿真,驗(yàn)證設(shè)計(jì)。 點(diǎn)擊“Run C Snthry”。

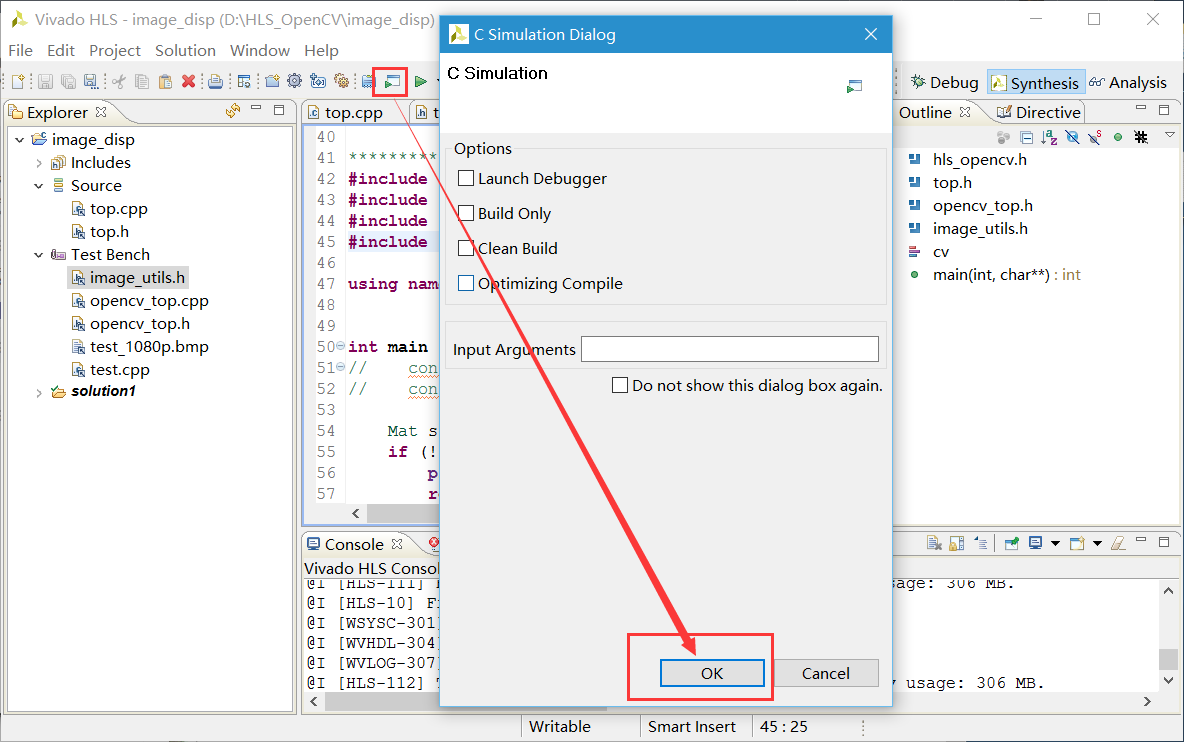

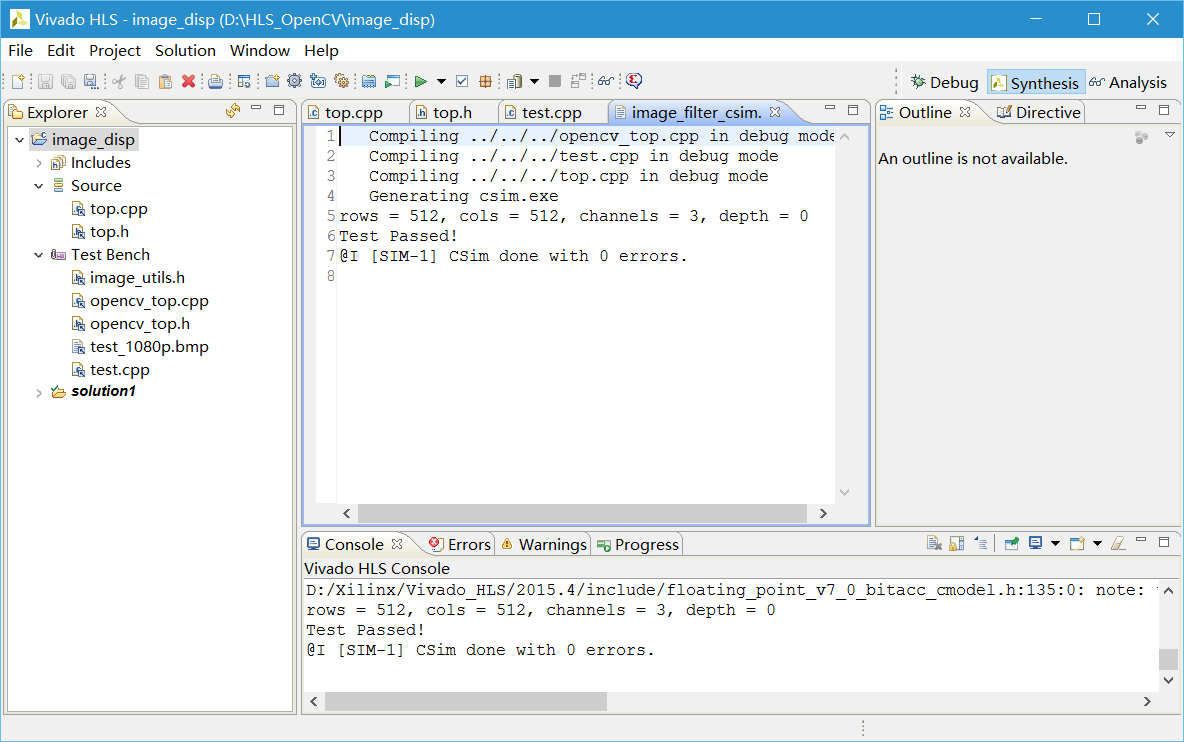

點(diǎn)擊“Run C Simulation”,接著點(diǎn)擊“OK”;

至此,此項(xiàng)目在沒有硬件調(diào)試的前提下算是成功運(yùn)行了。

審核編輯:湯梓紅

-

HDL

+關(guān)注

關(guān)注

8文章

332瀏覽量

48986 -

模型

+關(guān)注

關(guān)注

1文章

3756瀏覽量

52127 -

Vivado

+關(guān)注

關(guān)注

19文章

857瀏覽量

71149

發(fā)布評(píng)論請(qǐng)先 登錄

HLS設(shè)計(jì)中的BRAM使用優(yōu)勢(shì)

通過vivado HLS設(shè)計(jì)一個(gè)FIR低通濾波器

端側(cè)大模型上車:從“語音助手”到“車內(nèi) AI 智能體”的躍遷革命

從數(shù)據(jù)到模型:如何預(yù)測(cè)細(xì)節(jié)距鍵合的剪切力?

RA8P1部署ai模型指南:從訓(xùn)練模型到部署?|?本周六

vcs和vivado聯(lián)合仿真

如何在vivadoHLS中使用.TLite模型

干貨分享 | TSMaster MBD模塊全解析:從模型搭建到自動(dòng)化測(cè)試的完整實(shí)踐

如何在Unified IDE中創(chuàng)建視覺庫HLS組件

使用AMD Vitis Unified IDE創(chuàng)建HLS組件

如何使用AMD Vitis HLS創(chuàng)建HLS IP

從FA模型切換到Stage模型時(shí):module的切換說明

Vivado HLS設(shè)計(jì)流程

FPGA Verilog HDL語法之編譯預(yù)處理

一文詳解Verilog HDL

Vivado HLS從HDL到模型和C的描述

Vivado HLS從HDL到模型和C的描述

評(píng)論