盲目的拉線,拉了也是白拉!

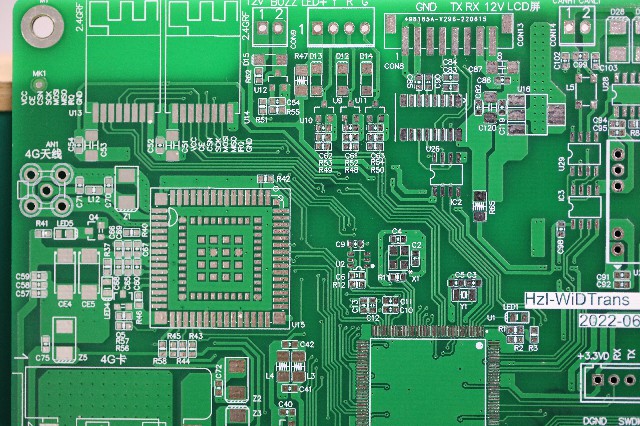

有些小伙伴在pcb布線時,板子到手就是干,由于前期分析工作做的不足或者沒做,導(dǎo)致后期處理時舉步維艱。

比如電源線、雜線拉完了,卻漏掉一組重要的信號線,導(dǎo)致這組線沒辦法同組同層,甚至都沒有完整的參考平面,需要對前面的布線工作做大修改才能完成,費(fèi)時費(fèi)力。

如果將PCB板比作我們的城市,元器件就像鱗次櫛比的各類建筑,信號線便是城里的大街小巷、天橋環(huán)島,每條道路的出現(xiàn)都是有它的詳細(xì)規(guī)劃,布線亦是如此。

布線優(yōu)先次序要求

a)關(guān)鍵信號線優(yōu)先:電源、摸擬小信號、高速信號、時鐘信號和同步信號等關(guān)鍵信號優(yōu)先。

b)布線密度優(yōu)先原則:從單板上連接關(guān)系最復(fù)雜的器件著手布線。從單板上連線最密集的區(qū)域開始布線。

c)關(guān)鍵信號處理注意事項(xiàng):盡量為時鐘信號、高頻信號、敏感信號等關(guān)鍵信號提供專門的布線層,并保證其最小的回路面積。必要時應(yīng)采取屏蔽和加大安全間距等方法。保證信號質(zhì)量。

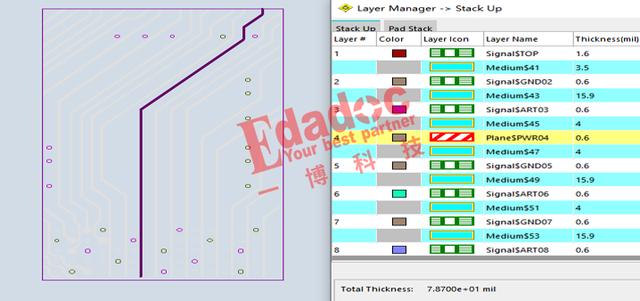

d)有阻抗控制要求的網(wǎng)絡(luò)應(yīng)布置在阻抗控制層上,須避免其信號跨分割。

2布線竄擾控制

a)3W原則釋義

線與線之間的距離保持3倍線寬。是為了減少線間串?dāng)_,應(yīng)保證線間距足夠大,如果線中心距不少于3倍線寬時,則可保持70%的線間電場不互相干擾,稱為3W規(guī)則。

b)竄擾控制:串?dāng)_(CrossTalk)是指PCB上不同網(wǎng)絡(luò)之間因較長的平行布線引起的相互干擾,主要是由于平行線間的分布電容和分布電感的作用。克服串?dāng)_的主要措施是:

i. 加大平行布線的間距,遵循3W規(guī)則;

ii.在平行線間插入接地的隔離線

iii. 減小布線層與地平面的距離。

3布線的一般規(guī)則要求

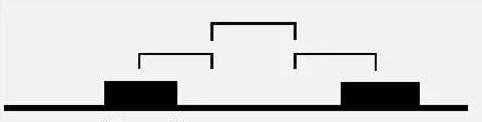

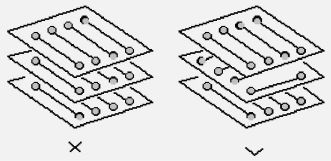

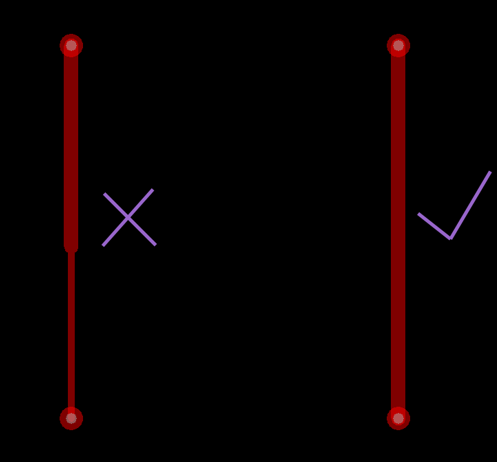

a)相鄰平面走線方向成正交結(jié)構(gòu)。避免將不同的信號線在相鄰層走成同一方向,以減少不必要的層間竄擾;當(dāng)由于板結(jié)構(gòu)限制(如某些背板)難以避免出現(xiàn)該情況,特別是信號速率較高時,應(yīng)考慮用地平面隔離各布線層,用地信號線隔離各信號線。

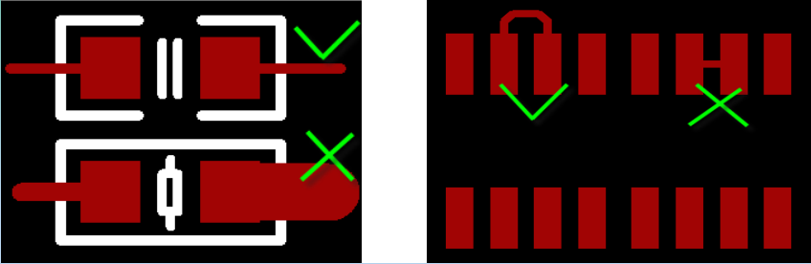

b)小的分立器件走線須對稱,間距比較密的SMT焊盤引線應(yīng)從焊盤外部連接,不允許在焊盤中間直接連接。

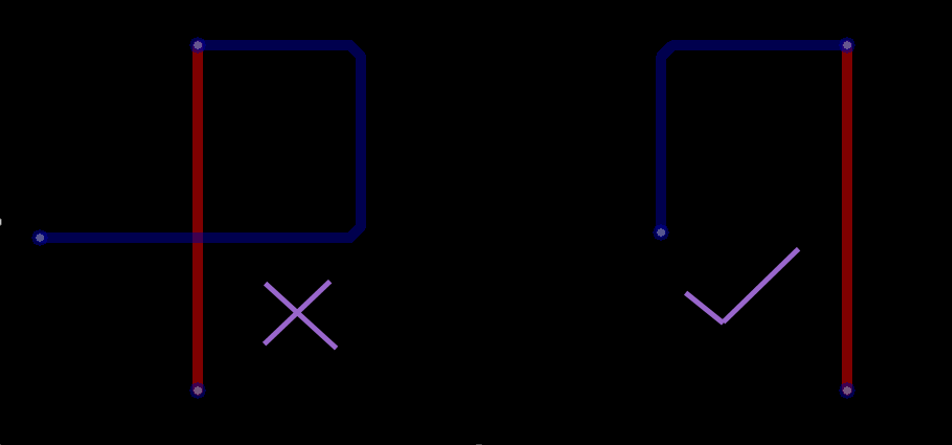

c)環(huán)路最小規(guī)則,即信號線與其回路構(gòu)成的環(huán)面積要盡可能小,環(huán)面積越小,對外的輻射越少,接收外界的干擾也越小。

d)走線不允許出現(xiàn)STUB。

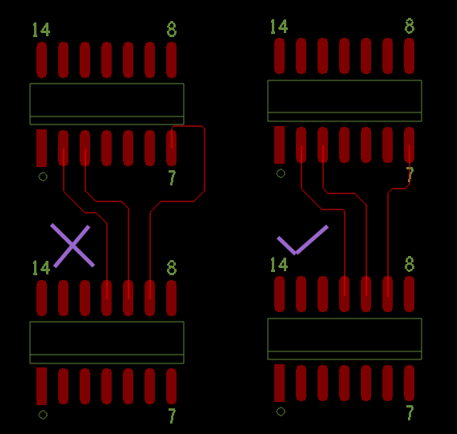

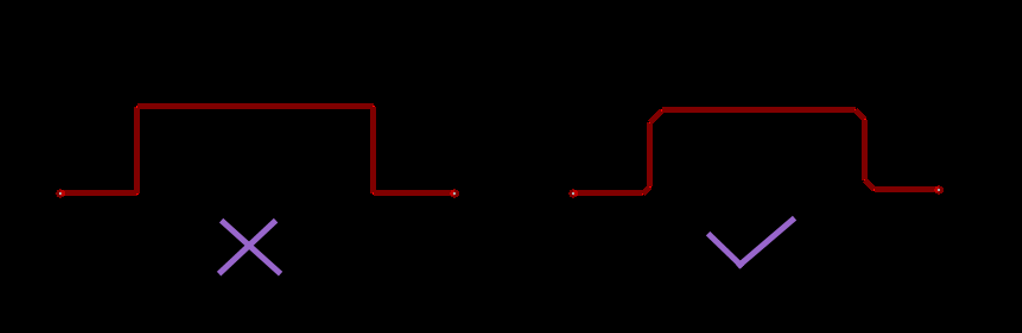

e)同一網(wǎng)絡(luò)的布線寬度應(yīng)保持一致,線寬的變化會造成線路特性阻抗的不均勻,當(dāng)傳輸?shù)乃俣容^高時會產(chǎn)生反射。在某些條件下,如接插件引出線,BGA封裝的引出線類似的結(jié)構(gòu)時,因間距過小可能無法避免線寬的變化,應(yīng)該盡量減少中間不一致部分的有效長度。

f)防止信號線在不同層間形成自環(huán)。在多層板設(shè)計中容易發(fā)生此類問題,自環(huán)將引起輻射干擾。

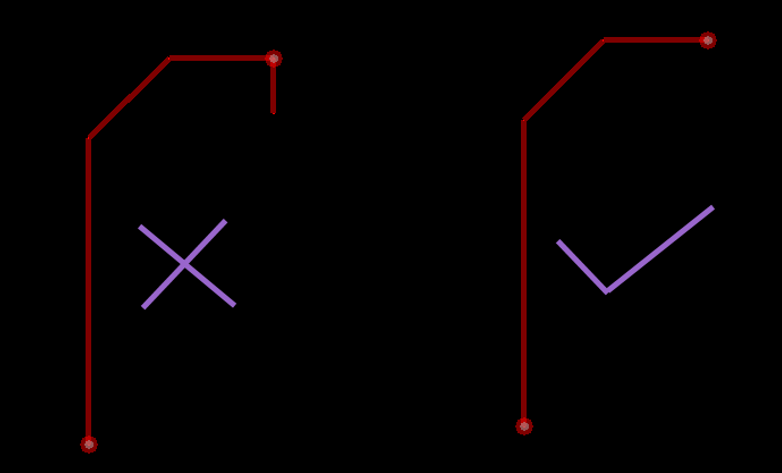

g) PCB設(shè)計中應(yīng)避免產(chǎn)生銳角和直角,產(chǎn)生不必要的輻射,同時PCB生產(chǎn)工藝性能也不好。

審核編輯 :李倩

-

pcb

+關(guān)注

關(guān)注

4405文章

23878瀏覽量

424379 -

阻抗控制

+關(guān)注

關(guān)注

1文章

57瀏覽量

11164

原文標(biāo)題:劃重點(diǎn)!PCB走線不要隨便拉

文章出處:【微信號:dianyuankaifa,微信公眾號:電源研發(fā)精英圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

MCU 的 3.3V 電源線走線有沒有問題?比如濾波電容的位置、走線長度這些是不是規(guī)范?

機(jī)房布線,上走線、下走線,哪個好?

PCB板雙面布局的DDR表底走線居然不一樣

PCB設(shè)計中的走線寬度與電流管理

到底DDR走線能不能參考電源層啊?

AD7792電流源輸出在走線時,如果走線過長,且走線很細(xì)10mil,會導(dǎo)致電流源大小衰減嗎?

別蒙我,PCB板上這幾對高速走線怎么看我都覺得一樣!

allegro軟件走線命令下參數(shù)不顯示如何解決

機(jī)柜配線架的走線方式

劃重點(diǎn)!PCB走線不要隨便拉

劃重點(diǎn)!PCB走線不要隨便拉

評論