今天要介紹的時序分析概念是fanout。中文名是扇出。指的是指定pin或者port的輸出端口數。

合理的選擇fanout的數目對設計來說是非常重要的,fanout過大與過小都會對設計帶來不利因素。

過大的fanout會使得驅動單元的負載過大,造成較大的延遲;過小的fanout會使得資源過于浪費,會使得path做得過長。

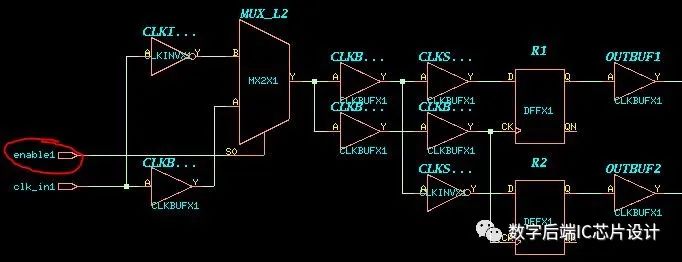

我們采用all_fanout來trace整個網表的扇出。但是需要注意的是all_fanout主要是時序路徑上的連接,不一定完全是物理連接在一起。比如下圖:

《CMD》all_fanout -from cppr_sub_2/enable1 -pin_level 3cppr_sub_2/enable1cppr_sub_2/MUX_L2/S0 cppr_sub_2/MUX_L2/Y cppr_sub_2/CLKBUF_L3_I1/Acppr_sub_2/CLKBUF_L3_I2/A

編輯:jq

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

驅動

+關注

關注

12文章

1956瀏覽量

88543 -

輸出端口

+關注

關注

0文章

25瀏覽量

10532 -

時序

+關注

關注

5文章

406瀏覽量

38870

原文標題:時序設計基本概念介紹

文章出處:【微信號:IC_Physical_Design,微信公眾號:數字后端IC芯片設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

深入解析LTC2924:高效電源時序控制器的卓越之選

深入解析LTC2924:高效電源時序控制器的卓越之選 在電子設備的設計中,電源的有序供應至關重要,它直接影響著設備的穩定性和性能。LTC2924作為一款功能強大的電源時序控制器,為多電源系統的設計提

深入剖析UCD90160A:16軌電源時序器與監控器的卓越之選

深入剖析UCD90160A:16軌電源時序器與監控器的卓越之選 在電子系統的設計中,電源管理是一個至關重要的環節。對于需要多個電壓軌且對電源時序和監控有嚴格要求的系統,UCD90160A這款16軌

TVS二極管的基本概念和主要作用

芝識課堂的全新內容又和大家見面啦!從本期開始,我們將用四節課為大家系統介紹一位在電路設計中默默奉獻的“無名英雄”——TVS二極管。我們會從它的基本概念、工作原理,聊到如何為電路挑選合適的型號、布局

vivado時序分析相關經驗

存在不滿足時序要求的邏輯級數。邏輯級數過多一般可以通過插入寄存器打拍子,分割冗長的組合邏輯。

線延時較長時,一般是因為扇出較大。

”report_high_fanout

發表于 10-30 06:58

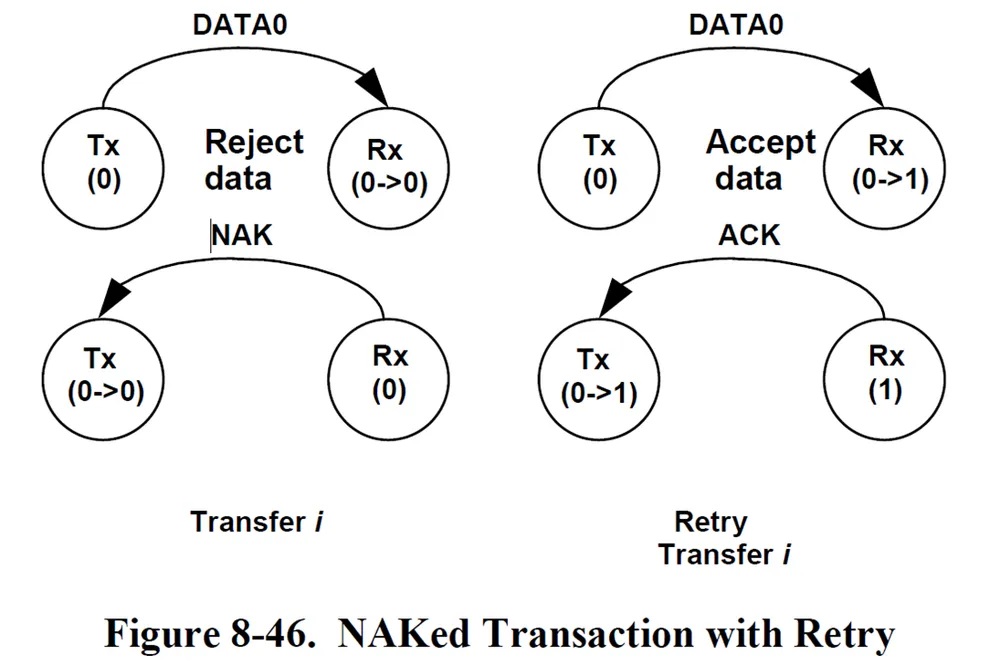

USB/HID及其基本概念

USB幀概念 如上圖所示,在USB1.1規范當中,把USB總線時間按幀劃分,每一幀占用時間是1ms; 每一幀內的最開始處是SOF token,在SOF內包含有11位的幀號; 每一幀的SOF幀號相比前

電壓波動與閃變的基本概念

如果您是電力系統工程師、電氣設備維護人員或者相關專業的學生,應該注意到了有關電能質量的國家標準GB/T 12326-2008是有關電壓波動和閃變的,那這兩個參數的考核意義是什么?國家標準規定這兩個參數如何計算、測量和考核?這篇文章帶您全面了解電壓波動和閃變的基本概念、重要性以及國家標準的規定。

自動駕駛中常提的“時序”是個啥?有啥作用?

[首發于智駕最前沿微信公眾號]自動駕駛技術的發展,不僅依賴于感知算法的精度和決策規劃的智能,還深深植根于系統內部對“時序”這一概念的精準把控。所謂時序,簡單來講,就是系統在不同模塊之間、不同傳感器

SiC MOSFET的基本概念

隨著全球對能源效率和可持續發展的關注不斷加深,寬禁帶半導體材料的研究與應用逐漸成為電子器件行業的熱點。碳化硅(SiC)作為一種重要的寬禁帶半導體材料,因其優異的電氣和熱學特性,正在快速取代傳統的硅(Si)器件,尤其是在高功率、高溫和高頻率應用中。SiCMOSFET(金屬氧化物半導體場效應晶體管)在電力電子領域的廣泛應用正在推動電源轉換效率的提高,并助力實現更高效的電能管理。本文將詳細探討SiCMOSFET的應用領域、性能優勢及未來發展趨勢。

群延遲的基本概念和仿真實例分析

在高速數字通信和射頻系統中,信號從發送端到接收端的傳輸過程中會遇到各種失真和畸變。群延遲(Group Delay)作為描述系統相位線性度的重要參數,直接影響著信號保真度和系統性能。本文將深入淺出地介紹群延遲的基本概念、應用場景,并通過仿真示例展示其在實際工程中的重要性。

淺談無線通信的基本概念

從工作頻段到信道的劃分,再到多址方式、雙工方式、調制方式、分集技術和MIMO,這些概念共同作用,使得無線通信能夠高效、可靠地進行。隨著技術的不斷發展,這些基礎技術也在不斷演進,尤其是在5G系統中,新的多址方式、雙工技術和更復雜的MIMO系統都為未來的通信提供了更多的可能性。

FPGA時序約束之設置時鐘組

Vivado中時序分析工具默認會分析設計中所有時鐘相關的時序路徑,除非時序約束中設置了時鐘組或false路徑。使用set_clock_groups命令可以使時序分析工具不分析時鐘組中時

時序設計基本概念之fanout

時序設計基本概念之fanout

評論