電賽在即,再給大家提供一個小技能,并一些有用的Verilog代碼,對于做高頻電路題目的同學(xué)有一定的參考。

以前介紹過我們用小腳丫FPGA的一根GPIO管腳制作的FM發(fā)射機,今天再介紹一個用FPGA搭配3個電阻、1個電容制作的1bit SDR接收機,接上喇叭,可以收聽中、長波電臺,連ADC都沒有用到。

該項目由Alberto Garlassi分享在Hackaday.io上,并在Github上開源了其Verilog代碼,巧的是,他使用的FPGA正好是我們小腳丫FPGA上用到的Lattice XO2系列。

原理圖用KiCad繪制,可以看出左側(cè)的3顆電阻以及1顆電容。

在Hackaday上的一些簡介:

創(chuàng)建這個項目是為了學(xué)習(xí) Verilog 并享受 FPGA 和 SDR 帶來的樂趣。主要目標(biāo)是使用盡可能少的組件接收AM廣播電臺。所選擇的FPGA萊迪思 MachXO2 也是可以使用的最簡單的組件之一。我能夠用20米長的電線作為天線,從位于三大洲的數(shù)千公里處接收電臺。最小的BOM包括一塊30歐元的 Lattice MachXO2分線板、三個電阻器、一個電容器和一個揚聲器。為了獲得更好的性能,最好添加一個晶體振蕩器,靈敏度和音頻質(zhì)量比使用內(nèi)部振蕩器更好。

天線直接連接到輸入引腳,因為您知道靜電荷會損壞電路板。當(dāng)您厭倦了破紀(jì)錄的元件數(shù)量時,最好添加一個串聯(lián)電容器和兩個限流二極管。使用 RC 濾波器、串聯(lián)電容器和有源揚聲器,音頻更實用。

無線電架構(gòu)非常標(biāo)準(zhǔn),直接變頻接收器。我們有一個 ADC、一個混頻器、兩個用于正交信號的 CIC 濾波器、一個采用信號平方和的平方根的 AM 解調(diào)器,以及一個用于音頻輸出的 PWM。頻率調(diào)諧由NCO獲得,它是一個 64 位累加器,其增量由UART控制,可以從控制PC發(fā)送一些字符并更改頻率。為此,該板有一個備用的UART通道。主通道用于編程,需要將USB轉(zhuǎn)串口轉(zhuǎn)換器的第二通道通過在電路板下側(cè)焊接橋接器連接到FPGA。

ADC 使用 LVDS 比較器作為輸入,但它的工作方式與 Sigma-Delta 轉(zhuǎn)換器不同,例如http://www.latticesemi.com/-/media/LatticeSemi/Documents/ReferenceDesigns/SZ2/FPGA-RD-02047-1-5-Simple-Sigma-Delta-ADC.ashx?document_id=35762

在這種情況下,反饋信號通過使用低RC時間常數(shù)來跟蹤輸入。在射頻下,這是不切實際的,反饋用于通過一個大的RC常數(shù)將比較器保持在開關(guān)電平附近。采樣是通過疊加到所需信號上的隨機 RF 噪聲來執(zhí)行的。我們在 80 MHz 下對 6 KHz 帶寬信號進行過采樣。對此的簡要解釋:如果輸入是真正隨機的,那么它在一定時間內(nèi)的平均值將幾乎為零。但它與來自遠處發(fā)射機的非常小的無線電信號相加,這足以對輸出產(chǎn)生輕微影響。https://en.wikipedia.org/wiki/Oversampling

CIC 濾波器抽取為 4096,因此 ADC 分辨率的理論增加為 6 位。

最好在較低的 CIC 抽取后使用 FIR 濾波器。是可以做到的,不是所有的FPGA都用到了。萊迪思沒有針對它的 IP,MachXO2 缺少 DSP 模塊,而且從未打算用于它。

另一個低組件數(shù)收音機:https://www.i2phd.org/armradio/index.html

自制的 1 位 ADC GPS 接收器,基于下面的文章:http://s53mv.s5tech.net/navsats/theory.html

以上是作者對此項目的介紹,如果使用Intel版本的小腳丫FPGA核心板,可以使用其DSP模塊獲得更高的性能,有興趣的同學(xué)可以嘗試一下。

在Github上有完整的工程內(nèi)容,基于Lattice XO2 FPGA的以及基于Intel Cyclone 3 FPGA版本。

如下是主要代碼的截圖:

有我們這款電賽綜合技能訓(xùn)練板的同學(xué),可以在這個板子上驗證一下,即便不適用高速ADC,使用板上的高速比較器(TP1961-TR),也可以輕松測試一下。

責(zé)任編輯:haq

-

FPGA

+關(guān)注

關(guān)注

1660文章

22412瀏覽量

636331 -

電容

+關(guān)注

關(guān)注

100文章

6487瀏覽量

159347 -

無線

+關(guān)注

關(guān)注

31文章

5688瀏覽量

178780

原文標(biāo)題:電賽技巧 - FPGA + 3個電阻 + 1個電容構(gòu)成的軟件定義無線電接收機,無需ADC

文章出處:【微信號:xiaojiaoyafpga,微信公眾號:電子森林】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

羅德與施瓦茨ESL3 EMI電磁干擾測量接收機

室內(nèi)如何批量測試接收機正常與否?gps信號轉(zhuǎn)發(fā)器 北斗信號放大器#單片機 #電工知識 #人工智能

AI接收機的工作原理和實現(xiàn)過程

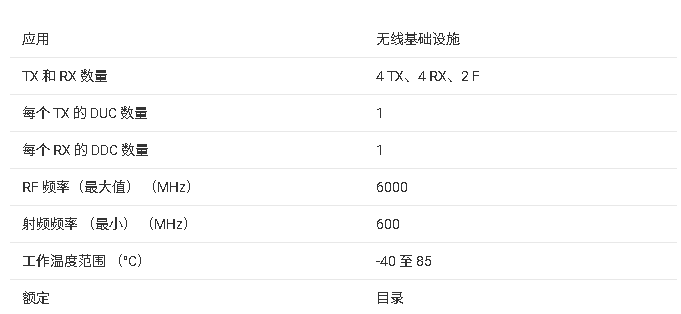

AFE7769 4 個發(fā)射、4 個接收、2 個反饋射頻收發(fā)器

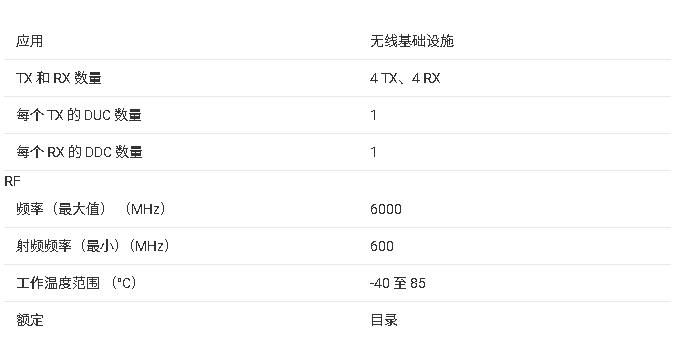

AFE7989 4 個發(fā)射、4 個接收、1 個反饋的射頻采樣收發(fā)器技術(shù)手冊

AFE7988 4 個發(fā)射、4 個接收、1 個反饋的射頻采樣收發(fā)器技術(shù)手冊

AFE8092 8 個發(fā)射、8 個接收 RF 采樣收發(fā)器技術(shù)手冊

WCDMA / HSDPA / HSUPA 前端模塊(發(fā)射機 880-915 MHz),(接收機 925-960 MHz) skyworksinc

SDR設(shè)備頻譜讀出,對于基底有個問題?

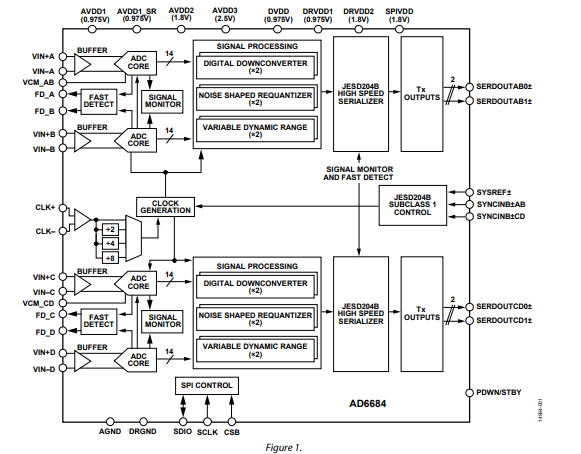

AD6684 135MHz四通道中頻接收機技術(shù)手冊

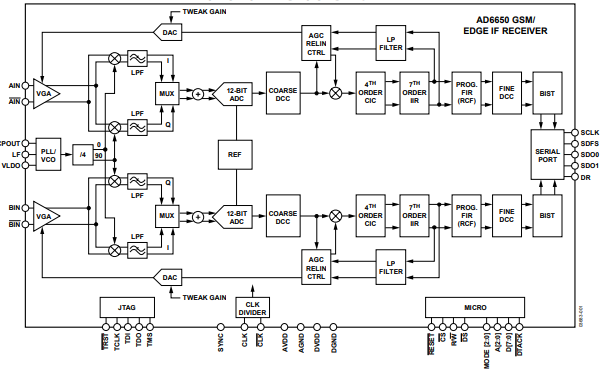

AD6650分集中頻至基帶GSM/EDGE窄帶接收機技術(shù)手冊

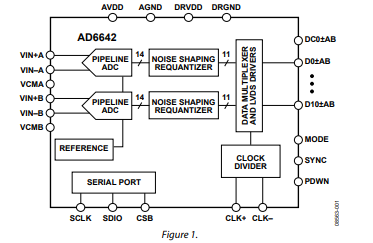

AD6642雙通道中頻接收機技術(shù)手冊

功德+1,用小安派-Eyes-S1做一個電子木魚

用FPGA搭配3個電阻、1個電容制作的1bit SDR接收機

用FPGA搭配3個電阻、1個電容制作的1bit SDR接收機

評論