Q1:

為啥制造標稱值和電路設計推薦值不一樣?

Answer:

制造標稱值和電路設計推薦值不一致,可以參照下圖,“操作空間”在你的問題上可以理解為“制造空間”。

Q2:

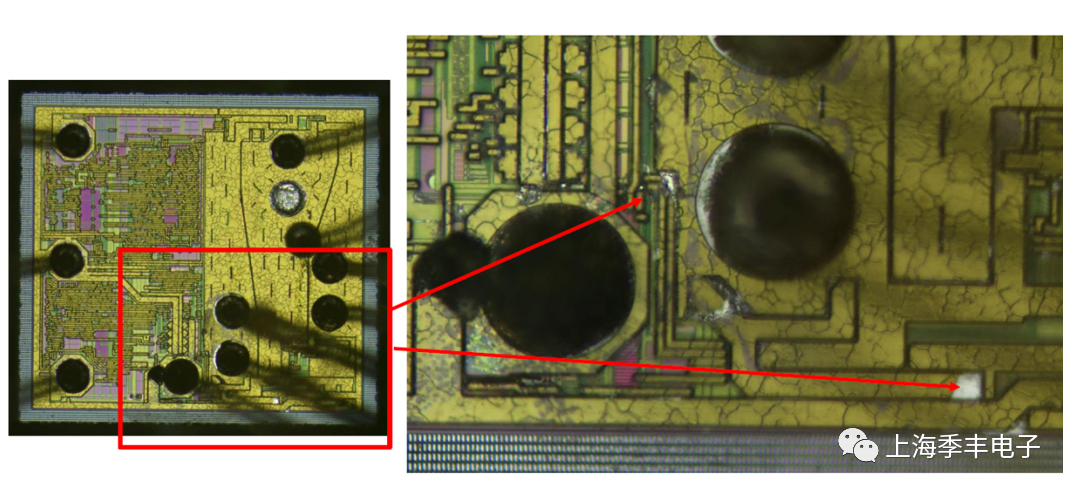

這個圖中,引起EOS的原因大概率是什么?EOS會導致打線脫落嗎?圖中標記的銀色部分是燒傷后導致的嗎?放大圖左邊PAD打線的左側是明顯的一個EOS痕跡嗎?去層的目的是定位是哪層metal的損傷位置嗎,來判定是哪個器件導致了電流過大或者電壓過大的損傷?

Answer:

導致EOS的可能原因:過電了,metal層燒傷了。EOS不會打線脫落。可以做下FIB和去層,找出失效點的位置。左邊PAD打線的左側,那個黑點應該是EOS點。

一般不會,劇烈的爆炸是有可能的,當然首先要排除封裝的問題。封裝問題需要借助SAT 和X-RAY來確認。另外,從圖片來看PAD上脫線跟開蓋清洗也有一定關系。

Q3:

burn-in有無規范?一般是按什么條件做呢?

Answer:

可以參考MIL-STD-883 METHOD 1015.11 BURN-IN TEST和JESD22-A108。

Q4:

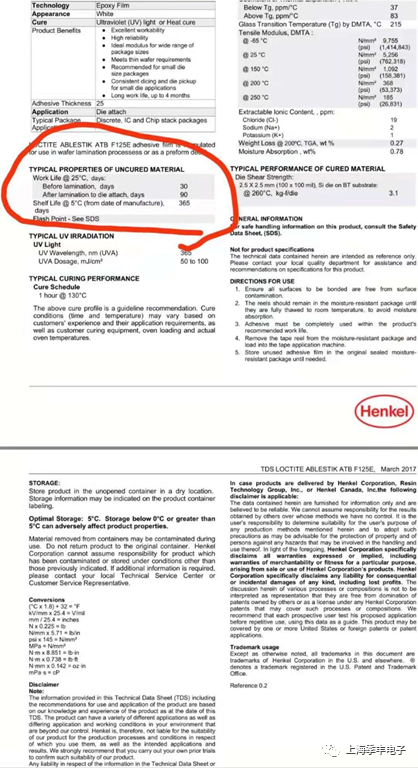

一般的UV膜的在真空包裝和氮氣柜的lifetime分別是多少?會用什么材料?

Answer:

DAF的life time僅供參考,詳細參考下圖。這是epoxy film,下面粘的是UV膜。DAF是代替非導電膠,CDAF是代替導電膠的,沒有bleed,主要用于疊die或者單芯片尺寸相對基島比較緊湊,可以使用。

Q5:

WLCSP封裝一般推薦哪些可靠性?目前有關于WLCSP可靠性驗證相關的行業標準嗎?有具體的條件嗎?

Answer:

WLCSP最容易出現的兩個情況:1、應力把球給蹦掉了;2、球熔在一起短路了。

推薦做:precon, UHAST,HTSL,TC,詳細的標準和測試條件見下表。

Q6:

SWIO通訊口管腳損傷,能通過FA分析出來是過壓還是靜電導致嗎?

Answer:

過壓和靜電都會發生的。可能的原因是:芯片管腳靜電保護沒做好,而且該管腳容易和外界接觸,比如天線,那么就容易被靜電打壞。大概率可以通過FA手段判斷damage來源。

Q7:

有沒有可以看wafer map的軟件啊?wafer map txt打開亂碼怎么辦?

Answer:

UltraEdit好用,方便修改。文件可能不是txt的格式,UE有一個轉碼功能,把碼轉一下。要確認下文件用什么編碼,如果解碼錯了就會亂碼。

Q8:

多芯片版本芯片 mapping上都是bin1,怎么可以把mapping中某一種芯片改成bin1?

Answer:

上面大佬提及的UltraEdit 就可以改,操作和Excel類似,全部替換即可,但是map里面有map說明等信息,注意要還原回來。

Q9:

CUP的pad打線出現crack,但是os和function測試都ok,能量產出貨嗎 ?后續會有什么可靠性問題嗎?頂層Al厚度1.2um,用了兩層metal,按理說pad設計沒問題,是封裝廠品控不行?

Answer:

肯定不能出貨,Crack會隨著時間惡化,最終器件早期失效。Pad打線出現的crack是在pad上,需要在pad上看下設計,有一種是底層為鋁做襯底,上層用Ti-Ni做導電傳導的,這種是可以的,我們做過可靠性,可以等效十年無異常。

Q10:

一般的device和CP測試的prober,對接地是否有特殊的要求。有沒有是直接接入辦公大樓接地極的,還是需要打獨立接地樁進行接地?

Answer:

雙線,ESD一根,接地一根,都打樁。

Q11:

很多設備的電源地和機殼地一般都設備內部短接了,這個接一根地線連接外部接地樁;ESD一根地線 是指設備提供作業員插靜電手環的孔嗎?

Answer:

雙線是大多數設備的基本方法,不管是prober還是別的設備,很多設備會有ESD口留著。

Q12:

SAT發現有嚴重分層,分層的原因可以根據SAT成像分析出來嗎?比如是水汽,EOS?

Answer:

一般SAT機臺是無法確認delamination形成的緣由的。這個是要后續的FA來界定的。

Q13:

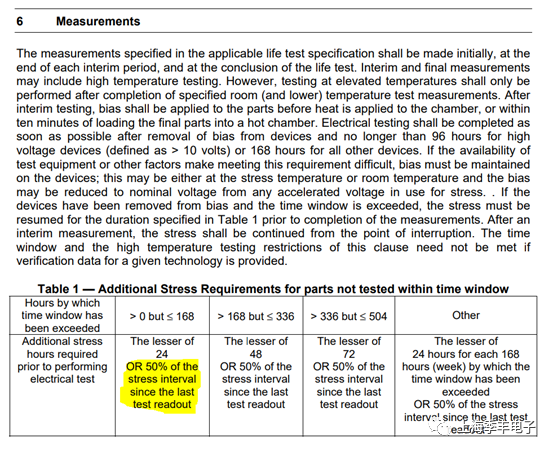

黃色的這部分怎么理解呢?

Answer:

樣品停止老化后,沒有能夠及時測試,那就要重新加應力(溫度+電壓)一段時間后再測試確認,測試前重新老化的時長參照表1. 第一列中,未及時測試時間小于168小時,則需重新老化24小時或者未完成測試的時間的一半,如耽擱了100小時,那應該再做50小時老化。

Q14:

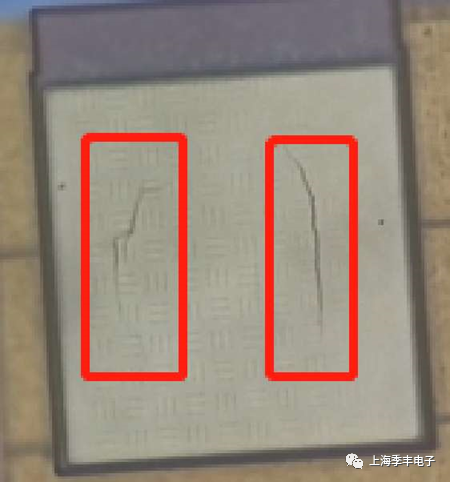

這個圖片是Al剝離以后的吧?下面有個標準圖。

Answer:

結構上沒啥問題,如果是Al層去除后發現的crack,風險很大,想出貨的話建議做3x reflow,測試后有管控的出貨。如果發生在打線后,也需要看下彈坑,看看下面結構上是不是也有問題,如果彈坑fail,處理方式同上。

引起crack問題很多,從你的圖片來看,需要確認測試od,次數及重疊狀況,針卡類型及清針方式,打線參數等。這個風險較大,reflow后降級報廢最好。另外,3xreflow后還有新的fail,基本上不能用了,還是讓封裝廠去調參數吧。

Q15:

鍵合絲線材的更換一般需要對芯片做哪些可靠性試驗呢?那個鍵合力的試驗BPS需不需要做呢?

Answer:

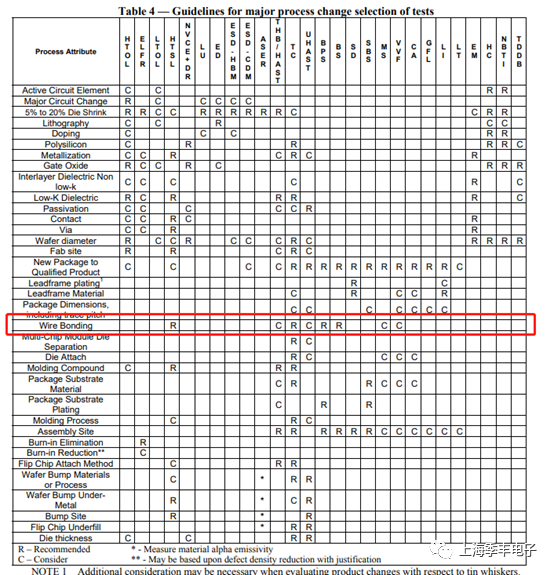

可靠性試驗:TC,HAST, HTS, HTOL, PCT。另外,鍵合力的試驗BPS也需要做。具體實驗可參考下圖。

Q16:

芯片上SMT前如果開封時間長的話要進行烘干,請問做烘干是為了去除芯片外表面的水汽還是為了去除芯片內部的水汽,內部的水汽可以通過烘干去除嗎?

Answer:

通常對新封裝類型是需要通過soaking/drying實驗來得到準確的baking condition: 取一定數量的fail 芯片先做soaking充分吸潮同時定期稱重量,至到吸潮飽和,芯片總重量不再增加;然后再對這些芯片在某一高溫下做烘烤,定期稱重量直到重量不會再減少。畫出芯片重量隨時間的變化曲線,就能定下來baking condition。

可以將烘烤的實驗,想象成一個水果,如果被烘成水果干,是不是內部和外部的水汽都被烘干。也可以找OSAT要一次這類package的baking推薦溫度/時間條件。芯片內部的水汽,應該主要是導電膠吸濕吧,DB烘烤125度2H就夠了。

Q17:

我們有時發現熱點在某個電阻部位,但設計公司認為是同一回路上其它地方器件損壞,而不是該電阻損壞。一般分析發現熱點的地方就一定是器件損壞的地方嗎?

Answer:

不一定。看你用的什么定位設備,OBIRCH和THERMOS的話,熱點和缺陷位置重合的概率高,尤其是Thermos。用EMMI的話,很多時候熱點和失效位置不重合,有時候還有假hotspots, 需要做layout tracing分析電路來進一步定位。

Q18:

55nm LOW-K工藝一定要用激光劃片嗎?激光劃片成本比刀具劃片成本一般會高出多少?

Answer:

Low k建議用激光開槽,否則chipping會很嚴重。成本增加主要是激光保護液增加的成本,具體看chip size即劃片道長度。或者可以直接blade saw,但是為了減少crack,需要feeding特別慢,不適合量產。

Q19:

一般哪些產品需要做EMC,MCU是否需要做這項?做MCU消費類應用需要達到什么等級,有什么標準可以參考?

Answer:

基本所有的電子產品都要做EMC,國內的CCC,歐洲的CE,美國的FCC,澳洲的RCM都要做的。還有車規也要做EMC,季豐有條件自己做車規EMC。

編輯:jq

-

芯片

+關注

關注

463文章

54010瀏覽量

466107 -

ESD

+關注

關注

50文章

2402瀏覽量

179918 -

編碼器

+關注

關注

45文章

3953瀏覽量

142647

原文標題:季豐電子IC運營工程技術知乎 – 21W28

文章出處:【微信號:zzz9970814,微信公眾號:上海季豐電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

電源適配器一般要做哪些認證

班通科技:一般PCB離子污染度限值對照表

rt-thread軟件定時器大家一般怎么用?

變頻器無規律過流故障問題

FCC認證周期一般多久

測量絕緣電阻一般用什么儀器

電能質量在線監測裝置硬件故障檢測的一般流程是什么?

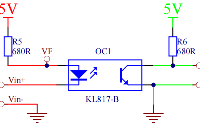

一般光耦的開關電路設計

鎧裝光纜和一般光纜區別對比分析

人臉識別門禁終端的一般故障排查方法

一般工控機與防爆工控機有哪些不同?

burn-in有無規范 一般是按什么條件做

burn-in有無規范 一般是按什么條件做

評論