每隔幾年,幾乎所有市場上廣泛普及的高頻串行通信標準(PCI-Express、USB、以太網、同步光網絡(SONET)、串行ATA(SATA)、Infiniband等)都會被修訂,以更好應對如今數據饑渴型社會的更高期望。隨著這些標準新版本的推出,市場對支持它們的電子電路的需求也加強了。集成在當代系統應用中的高性能時鐘產生及分配器件使用頻域參數,也就是相位噪聲和相位抖動來描述它們的性能。本文探討相位噪聲圖怎樣配合估計制造商數據表上沒有明確提及的時鐘器件特性,使工程師能夠更好地評判針對特定應用的適合情況。

當應用高速串行鏈路時,可以利用周期抖動來推導相關位誤差率(BER)。時鐘器件的抖動傳遞及PLL帶寬也是重要衡量標準,因為透過這些參數有可能更好推測輸入源或輸入時鐘會怎樣影響器件的輸出。所有這些都將幫助工程師選擇符合他們需求的恰當時鐘器件。然而,這些參數很少直接標明,故必須進行計算。

抖動傳遞

抖動傳遞揭示一定偏移頻率范圍內的衰減量或產生的噪聲。它由鎖相環(PLL)的環路濾波器響應來確定。相位噪聲圖提供所有偏移頻率時的噪聲密度,因此它包含確定時鐘器件抖動傳遞所必要的數據。顯示抖動傳遞、產生及衰減的最佳方式,是使用在較低偏移頻率時擁有較高底噪及在較高偏移頻率時擁有較低底噪的時鐘源。在低頻時,PLL將高源噪聲傳遞至輸出;而在高頻時,它將顯示固有底噪,這是PLL低通帶寬特性的緣故。

低帶寬PLL即使在較低偏移頻率時也能衰減抖動,PLL帶寬越低,在此等頻率時的衰減性能也會更高。然而,低帶寬PLL存在響應時間較慢的缺點——它會花費時間來跟蹤輸入時鐘變化。大多數網絡通信鏈路在較低偏移頻率時的約束不那么嚴格。

PLL帶寬

如果使用了恰當的參考時鐘源,除了抖動傳遞,相位噪聲圖也能幫助確定PLL帶寬。為了充分理解PLL帶寬估計及PLL的抖動傳遞,應當進行簡單的測量設置,使用兩個不同時鐘源來為一個高性能零延遲緩沖器(ZDB)饋送信號。

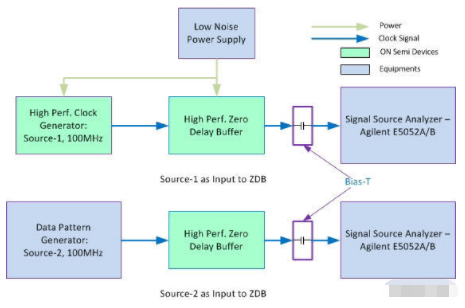

圖1:電路圖顯示了PLL帶寬及抖動傳遞測量

圖1顯示了介紹相位噪聲測量設置的簡單電路圖。測量是使用安捷倫5052A信號源分析儀進行的。源1(高性能時鐘產生器)和ZDB采用低噪聲電源供電。

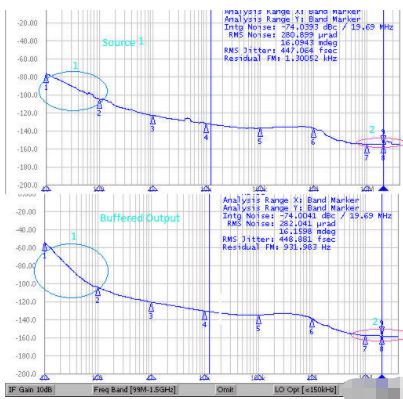

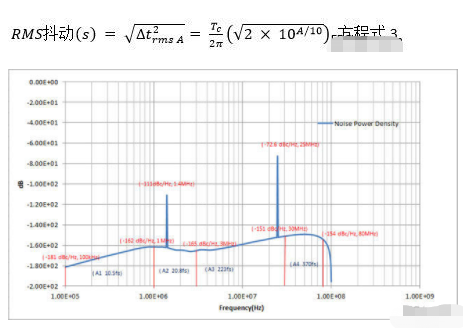

圖2:源1及緩沖器輸出的相位噪聲圖

如圖2所示,源1的均方根(RMS)相位抖動為約447 fs,而緩沖器輸出為約448.8 fs。RMS抖動是在從10 kHz至20 MHz的偏移頻率范圍內測量的。在10至100 Hz的較低偏移頻率時,緩沖器噪聲相比源而言較高,但對大多數通信信道而言這并不構成問題,因為它被PLL輕易地跟蹤。輸出緩沖器相位噪聲圖大致匹配高達1 MHz的源相位噪聲圖。高于此頻率時,緩沖器輸出的底噪低于源底噪,如圖2中的第2號圈所示。

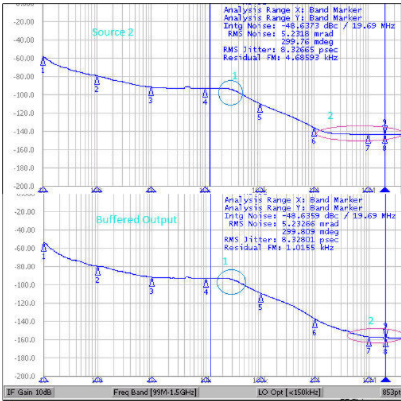

源2使用了數據模式產生器(DPG)。它擁有比源1量多高的底噪。因此,圖3所示的緩沖器輸出圖匹配較低頻率(10-100Hz)時的輸入源。緩沖器-PLL傳遞低于1 MHz的輸入噪聲;源噪聲圖中30 kHz附近的突兀變化反射在緩沖器輸出噪聲圖中,如圖3中所第1號圈所示。對于高于1 MHz的頻率而言,緩沖器底噪明顯低于源底噪,如圖3中2號圈所示;這表示緩沖器在此頻率范圍內充當抖動衰減器。

圖3:源2及緩沖輸出的相位噪聲圖

周期抖動

如前所述,周期抖動是用于在高速串行標準中對BER進行近似估算的一項重要參數,但通常情況下時鐘器件制造商僅提供使用低噪聲頻域設備測量的相位抖動或相位噪聲數據。相位噪聲頻譜定義為基于載波功率頻譜密度峰值的衰減(單位為dB/Hz)。相位噪聲頻譜密度與RMS周期抖動之間的關系是:

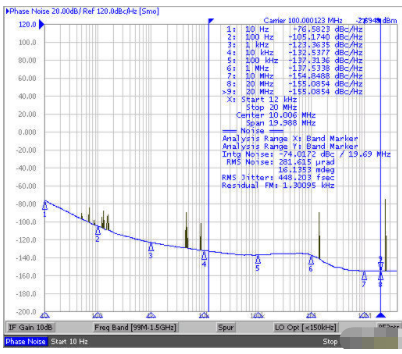

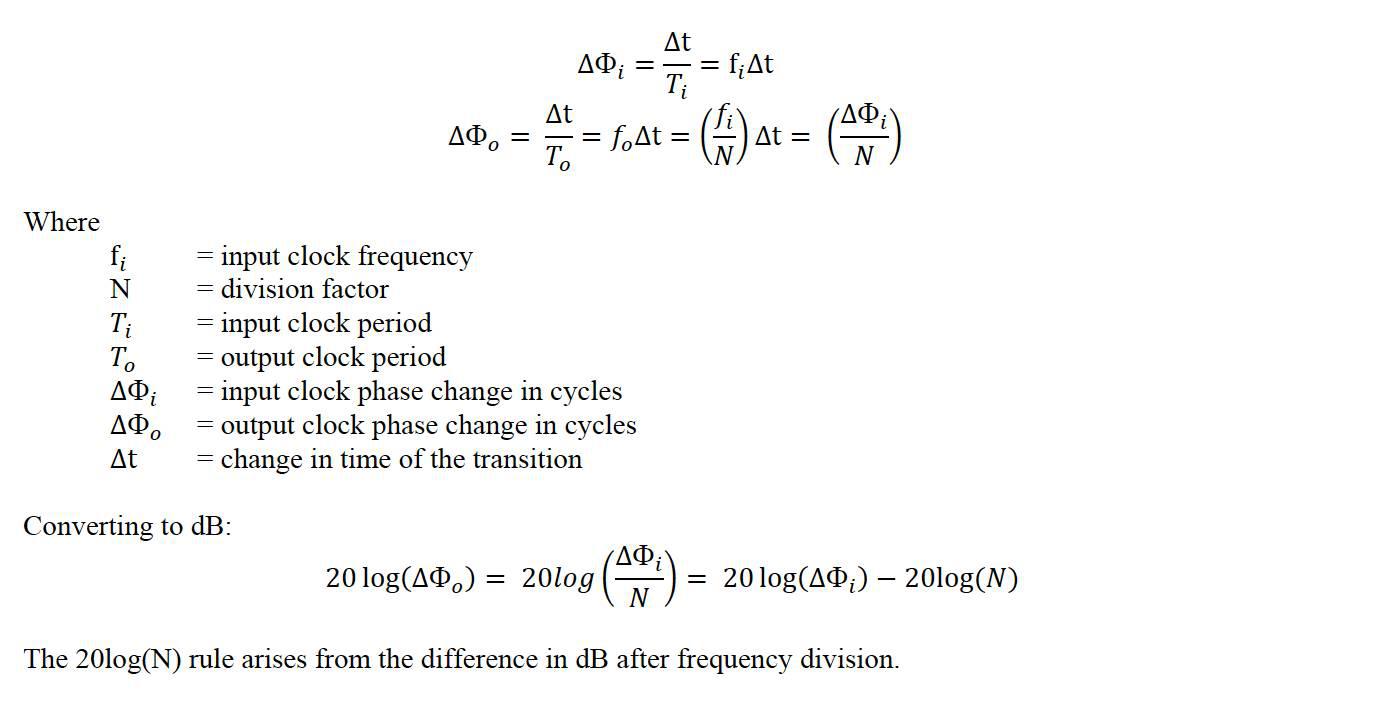

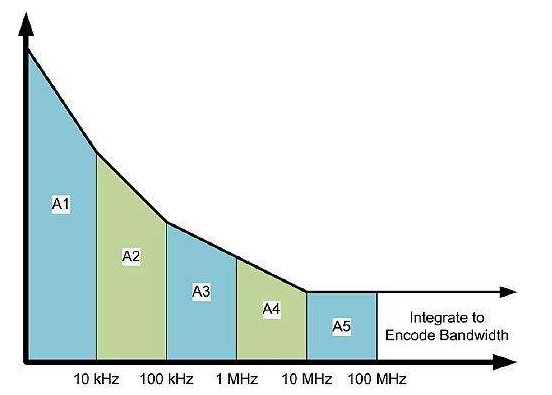

為了根據相位噪聲圖估計周期抖動,偏移頻率的相位噪聲必須乘以〖4sin〗^2 (πfτ)函數。dB換算4〖sin〗^2 (πfτ)顯示它擁有-20dB/十倍頻(decade)的斜率(見圖5)。4〖sin〗^2 (πfτ)以dB為單位的值可以增加到相位噪聲圖數據中,單位為dBc。相關偏移頻率范圍內最終數據的數值積分將提供單邊頻帶的相位噪聲密度。例如,為了根據圖4中給出的相位噪聲圖來估計周期抖動,增加以dB為單位的4 〖sin〗^2 (πfτ)函數數據到相位噪聲(PN)數據(單位為dBc/Hz)中,如圖5所示。所獲得的藍色曲線顯示了相位噪聲頻譜密度。

圖4:帶有毛刺的時鐘產生器輸出相位噪聲圖

對圖5中藍色曲線以下區域進行積分將得到相位噪聲頻譜密度(單位為dB)(對應區域A)。它可以使用下列方程式換算為均方根拉動:

圖6:相位噪聲的RMS抖動換算

如圖6所示,曲線下面的區域根據曲線形狀或是使用分段線性函數,可以劃分為幾個不同部分(A1、A2等)。由于較低偏移頻率噪聲不會大幅影響周期抖動,故僅考慮較高偏移頻率下的曲線。為了提高精度,完整曲線可以劃分為多個部分,相應各個部分對周期抖動的影響。圖6中的曲線劃分為4個部分,每個部分包含2個相關數據點(相位噪聲、偏移頻率)。使用這些數據點,每個部分的面積可以換算為等效的抖動(以秒為單位為表述)。

每個部分對RMS抖動的貢獻如圖6所示。這些RMS抖動值之和可以使用下列方程式來計算:

根據這個等式,可以計算出圖6中顯示的4個區域對抖動的總體貢獻之和為434 fs。此值乘以2即得到總噪聲貢獻△trmsPN)——868 fs。此外,圖6中還有2個毛刺。由于這些毛刺在單個頻率上,可以使用下列方程式來單獨計算及增加它們對抖動的貢獻:

每個毛刺的dB值都可以使用方程式3換算為抖動。

圖6中顯示的示例在1.4 MHz和25 MHz頻率時有毛刺,分別為-111 dB和-72.6 dB。1.4 MHz毛刺的等效RMS抖動為6.3 fs,25 MHz毛刺等效RMS抖動為527 fs。較高頻率的毛刺對周期抖動的影響比較低頻率的毛刺更大。25 MHz毛刺的值要比1.4 MHz毛刺高得多。使用方程式5計算的總毛刺RMS抖動值△trms Spur)極接近于527 fs,因此,1.4 MHz毛刺的影響可以忽略不計。高dB毛刺可能是某些應用中因抖動影響增加而易于出現的誤差。使用方程式2,可以估算出圖6中描繪圖表的總周期抖動為1.015ps。

總而言之,工程師在指定時鐘器件時,諸如相位噪聲及相位抖動等頻域參數對他們極有價值。器件制造商提供的相位噪聲圖是這些產品的極重要性能指示工具。可以使用圖表來近似估算PLL的帶寬及抖動傳遞特性,因而幫助確定它在相關頻率范圍的特性(作為抖動衰減器或產生器)。也可以根據給定圖表來估算周期抖動,方式是考慮主導頻率范圍內的相位噪聲及關鍵頻率時的毛刺。尋求為下一代設計應用指定時鐘器件的工程師使用這些信息,可以作出具有更高權威性的產品造型決策。

責任編輯:gt

-

以太網

+關注

關注

41文章

5998瀏覽量

180854 -

帶寬

+關注

關注

3文章

1040瀏覽量

43372 -

測量

+關注

關注

10文章

5636瀏覽量

116730

發布評論請先 登錄

敏捷合成器的技術原理和應用場景

電源噪聲和時鐘抖動對高速DAC相位噪聲的影響分析及管理

測量較低時鐘頻率的相位噪聲和相位抖動

時鐘抖動(CLK)和相位噪聲之間的轉換

電源噪聲和時鐘抖動對高速DAC相位噪聲的影響

相位噪聲定義 相位噪聲來源 相位噪聲對信號的影響

RTC時鐘芯片的特性及應用場景

如何使用相位噪聲圖方向時鐘器件特性及適用應用場景

如何使用相位噪聲圖方向時鐘器件特性及適用應用場景

評論