簡(jiǎn) 介:

集成電路設(shè)計(jì)越來越向系統(tǒng)級(jí)的方向發(fā)展,并且越來越強(qiáng)調(diào)模塊化的設(shè)計(jì)。SPI(Serial Peripheral Bus)總線是Motorola公司提出的一個(gè)同步串行外設(shè)接口,容許CPU 與各種外圍接口器件以串行方式進(jìn)行通信、交換信息。本文簡(jiǎn)述了SPI總線的特點(diǎn),介紹了其4條信號(hào)線,SPI串行總線接口的典型應(yīng)用。

重點(diǎn)描述了SPI串行總線接口在一款802.11b芯片中的位置,及該接口作為基帶和射頻的通訊接口所完成的功能,并給出了用硬件描述語(yǔ)言Verilog HDL 實(shí)現(xiàn)該接口的部分程序。該實(shí)現(xiàn)已經(jīng)在Modelsim 中完成了仿真, 并經(jīng)過了FPGA 驗(yàn)證, 最后給出了仿真和驗(yàn)證的結(jié)果。

在SOC設(shè)計(jì)中,利用EDA 工具設(shè)計(jì)芯片實(shí)現(xiàn)系統(tǒng)功能已經(jīng)成為支撐電子設(shè)計(jì)的通用平臺(tái)。并逐步向支持系統(tǒng)級(jí)的設(shè)計(jì)方向發(fā)展。而且,在設(shè)計(jì)過程中,越來越強(qiáng)調(diào)模塊化設(shè)計(jì)。

SPI總線是Motorola公司提出的一個(gè)同步串行外設(shè)接口,具有接口線少、通訊效率高等特點(diǎn)。本文給出的是利用Verilog HDL實(shí)現(xiàn)的SPI總線模塊,該模塊是802.11b無線局域網(wǎng)芯片中一個(gè)子模塊,該模塊完成了芯片中基帶(base band)與RF的通訊工作。

1 SPI總線接口概述

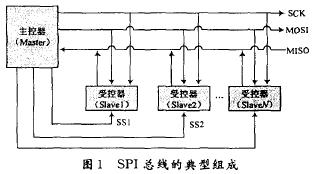

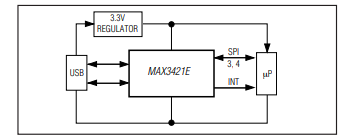

SPI(Serial Parallel Bus)總線是Motorola公司提出的一個(gè)同步串行外設(shè)接口,允許CPU 與各種外圍接口器件(包括模/數(shù)轉(zhuǎn)換器、數(shù)/模轉(zhuǎn)換器、液晶顯示驅(qū)動(dòng)器等)以串行方式進(jìn)行通信、交換信息。他使用4條線:串行時(shí)鐘線(SCK)、主機(jī)輸入/從機(jī)輸出線(MISO)、主機(jī)輸出/從機(jī)輸入線(MOSI)、低電平有效的使能信號(hào)線(CS)。這樣,僅需3~4根數(shù)據(jù)線和控制線即可擴(kuò)展具有SPI接口的各種I/O器件 其典型結(jié)構(gòu)如圖1所示。

SPI總線具有以下特點(diǎn):

(1)連線較少,簡(jiǎn)化電路設(shè)計(jì)。并行總線擴(kuò)展方法通常需要8根數(shù)據(jù)線、8~16根地址線、2~3根控制線。而這種設(shè)計(jì),僅需4根數(shù)據(jù)和控制線即可完成并行擴(kuò)展所實(shí)現(xiàn)的功能。

(2)器件統(tǒng)一編址,并與系統(tǒng)地址無關(guān),操作SPI獨(dú)立性好。

(3)器件操作遵循統(tǒng)一的規(guī)范,使系統(tǒng)軟硬件具有良好的通用性。

2 SPI總線接口的設(shè)計(jì)與實(shí)現(xiàn)

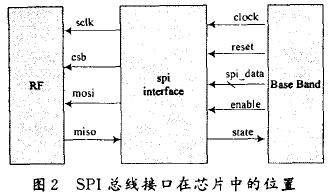

該模塊是802.1lb無線局域網(wǎng)芯片中的一子模塊,其在芯片中的位置如圖2所示。

其中base band(基帶)為SPI的主控器(master),RF(射頻)為SPI的受控器(slave)。SPI interface作為baseband與RF的通訊接口,主要完成以下工作:

(1)將從base band接收到的16位的并行數(shù)據(jù),轉(zhuǎn)換為RF所能接收的串行數(shù)據(jù),并將該數(shù)據(jù)根據(jù)SPI協(xié)議送給RF。

(2)產(chǎn)生RF所需的時(shí)鐘信號(hào)SCLK,使能信號(hào)CSB。

(3)接收從RF傳回的串行數(shù)據(jù),并將其轉(zhuǎn)換為并行數(shù)據(jù)。

(4)將base band發(fā)送的數(shù)據(jù),與RF返回的數(shù)據(jù)進(jìn)行比較,并把比較結(jié)果傳給base band。

下面給出用Verilog HDL語(yǔ)言實(shí)現(xiàn)前兩項(xiàng)功能的關(guān)鍵程序,相關(guān)變量的聲明在此略去。

//generate a counter

always@ (posedge clock or negedge reset)

begin

if(!reset)

counter《= 0;

else if(enable)

begin

if(counter《 53)

counter=counter + 1;

end

end

//generate signal “csb”

always@ (posedge clock or negedge reset)

begin

if(!reset)

csb 《=1;

else if(counter》= 1 && counter 《= 50)

csb = 0;

else

csb = 1;

end

//Generate “sclk”

always@ (posedge clock or negedge reset)

begin

case(counter)

6‘d02: sclk = 1;

6’d05: sclk = 1;

6‘d08: sclk = 1;

6’d11: sclk = 1;

6‘d14: sclk = 1;

6’d17: sclk = 1;

6‘d20: sclk = 1;

6’d23: sclk = 1;

6‘d26: sclk = 1;

6’d29: sclk = 1;

6‘d32: sclk = 1;

6’d35: sclk = 1;

6‘d38: sclk = 1;

6’d41: sclk = 1;

6‘d44: sclk = 1;

6’d47: sclk = 1;

default sclk = 0;

endcase

end

always@ (counter or csb)

begin

if(csb == 0)

case(counter)

6‘h00,

6’h01,

6‘h02,

6’h03:mosi_index = 5‘h00;

6’h04,

6‘h05,

6’h06:mosi_index = 5‘h01;

6’h07,

6‘h08,

6’h09:mosi_index = 5‘h02;

6’h0A,

6‘h0B,

6’h0C:mosi_index = 5‘h03;

6’h0D,

6‘h0E,

6’h0F:mosi_index = 5‘h04;

6’h10,

6‘h11,

6’h12:mosi_index = 5‘h05;

6’h13,

6‘h14,

6’h15:mosi_index = 5‘h06;

6’h16,

6‘h17,

6’h18:mosi_index = 5‘h07;

6’h19,

6‘h1A,

6’h1B:mosi_index = 5‘h08;

6’h1C,

6‘h1D,

6’hlE:mosi_index = 5‘h09;

6’h1F,

6‘h20,

6’h21:mosi_index = 5‘h0A ;

6’h22,

6‘h23,

6’h24:mosi_index = 5‘h0B;

6’h25,

6‘h26,

6’h27:mosi_index = 5‘h0C ;

6’h28,

6‘h29,

6’h2A:mosi_index = 5‘h0D ;

6’h2B,

6‘h2C,

6’h2D:mosi_index = 5‘h0E;

6’h2E,

6‘h2F,

6’h30:mosi_index = 5‘h0F;

default:mosi_index = 5’h00;

endcase

else

mosi_index = 5‘h00:

end

assign mosi=spi_data[mosi_index3];

用Verilog HDL實(shí)現(xiàn)的SPI總線接口模塊,在ModelSim 中編譯、調(diào)試,并做了前仿真。

前仿真通過后,又在Altera公司的EPXA10 Develop Board上做了FPGA驗(yàn)證,結(jié)果與在ModelSim 中的仿真結(jié)果一致。最后在base band與RF的聯(lián)合調(diào)試過程中,該SPI總線接口模塊達(dá)到了預(yù)期的要求。

編輯:jq

-

cpu

+關(guān)注

關(guān)注

68文章

11313瀏覽量

225652 -

soc

+關(guān)注

關(guān)注

40文章

4610瀏覽量

229965 -

SPI

+關(guān)注

關(guān)注

17文章

1894瀏覽量

101819 -

CS

+關(guān)注

關(guān)注

0文章

55瀏覽量

25597 -

MOSI

+關(guān)注

關(guān)注

0文章

5瀏覽量

4359

原文標(biāo)題:SPI串行總線接口的Verilog實(shí)現(xiàn)

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

深入解析Microchip 23A256/23K256 256-Kbit SPI總線低功耗串行SRAM

深入解析Microchip 25AA128/25LC128 128K SPI總線串行EEPROM

使用PicoScope示波器解碼SPI總線信號(hào)

瑞芯微(EASY EAI)RV1126B SPI使用

PCA9958:24通道SPI串行總線63 mA/5.5 V恒流LED驅(qū)動(dòng)器的深度解析

SPI、I2C、UART三種串行總線的區(qū)別與對(duì)比

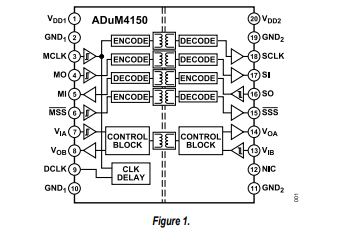

ADUM4150用于SPI高速接口的5kV專用隔離器技術(shù)手冊(cè)

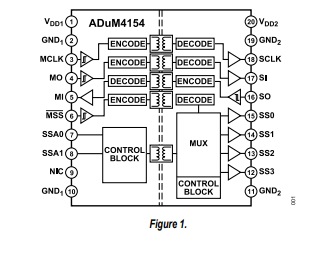

ADUM4154用于SPI接口的5 kV專用隔離器技術(shù)手冊(cè)

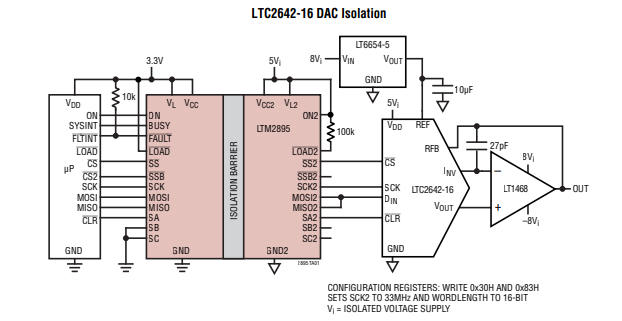

LTM2895 100MHz隔離型DAC SPI串行接口技術(shù)手冊(cè)

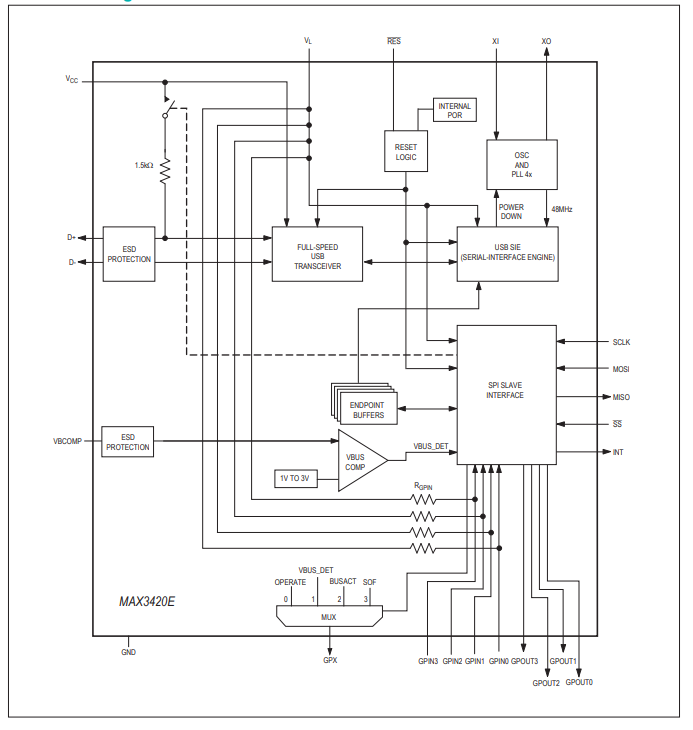

MAX3420E USB外設(shè)控制器,SPI接口技術(shù)手冊(cè)

MAX3421E USB外設(shè)/主機(jī)控制器,SPI接口技術(shù)手冊(cè)

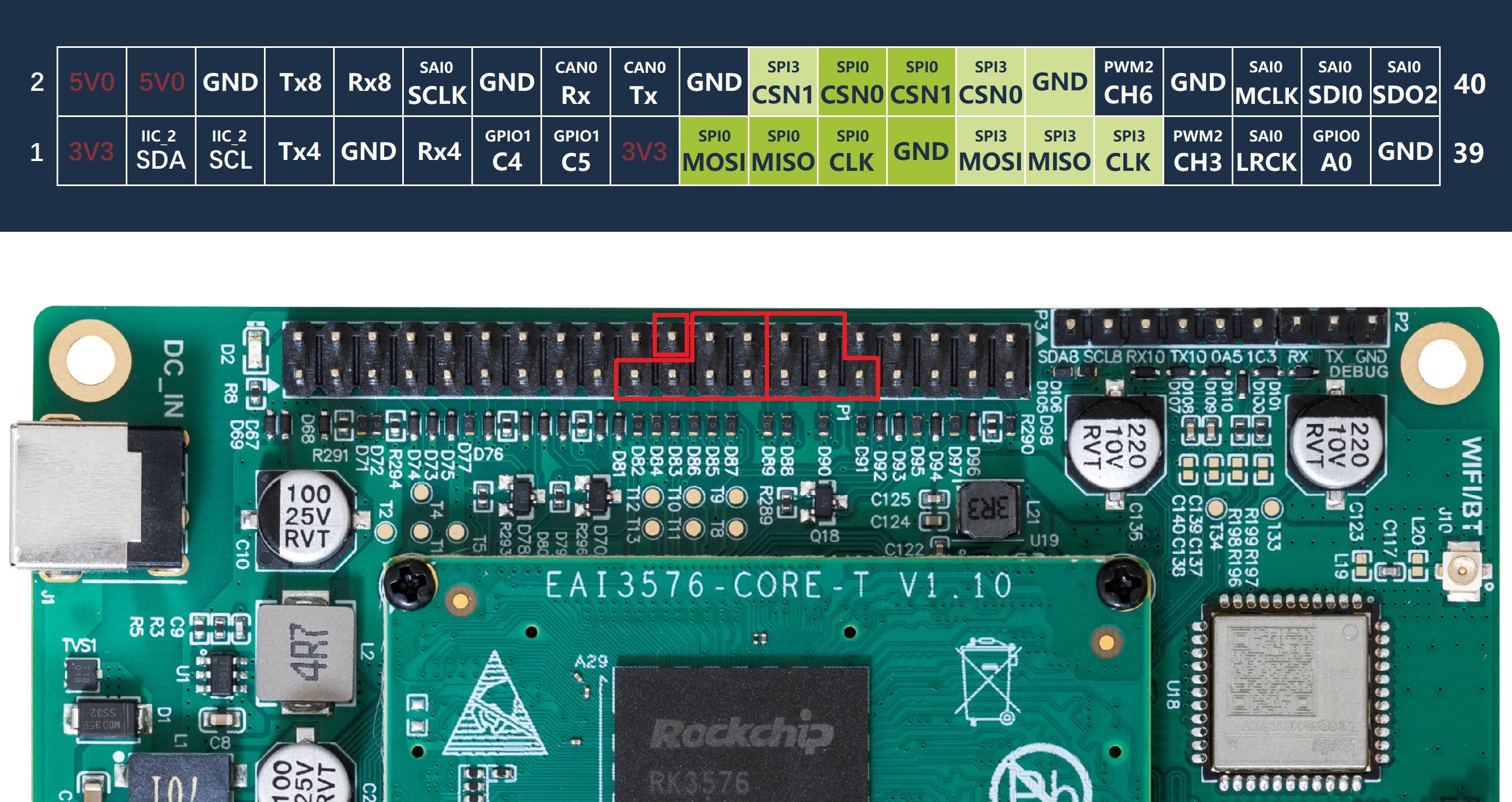

基于RK3576開發(fā)板的SPI使用說明

串行通信接口SPI與QSPI的區(qū)別

基于SPI串行總線接口的Verilog實(shí)現(xiàn)

基于SPI串行總線接口的Verilog實(shí)現(xiàn)

評(píng)論