當(dāng)前,通過常規(guī)的晶體管尺寸微縮越來越難以獲得理想性能增益,每一次集成電路工藝的進(jìn)步都凝聚著產(chǎn)業(yè)鏈上下各個(gè)環(huán)節(jié)的辛勞成果。加州大學(xué)圣迭戈分校研究團(tuán)隊(duì)近期報(bào)導(dǎo)了針對CFET這一被認(rèn)為是3nm以下必然采用的新型晶體管結(jié)構(gòu)進(jìn)行的前沿研究,探究了晶體管物理結(jié)構(gòu)實(shí)現(xiàn)的兩類協(xié)同優(yōu)化技術(shù),其成果有望加速CFET技術(shù)的成熟和應(yīng)用落地。

研究背景

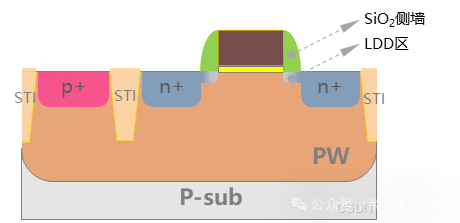

隨著技術(shù)節(jié)點(diǎn)的不斷進(jìn)步,已服役十年的FinFET集成電路器件,其工藝單元設(shè)計(jì)工藝協(xié)同優(yōu)化(DTCO)*由于布線空間和p-n橫向排布間距受限而逐漸達(dá)到了工藝微縮的極限。因此,系統(tǒng)工藝協(xié)同優(yōu)化(STCO)*概念被提出來,其典型應(yīng)用代表是三維結(jié)構(gòu)的Complementary-FET (CFET)晶體管,這種新型結(jié)構(gòu)通過將p-FET堆疊在n-FET上實(shí)現(xiàn)工藝單元集成,減少單個(gè)工藝單元的面積占用。然而,CFET的標(biāo)準(zhǔn)單元(standard cell,以下采用文中簡稱“SDC”)設(shè)計(jì)要求從全局考慮以克服堆疊結(jié)構(gòu)帶來的高度限制,從而實(shí)現(xiàn)面積多小對晶體管性能最大化增益。

傳統(tǒng)晶體管結(jié)構(gòu)與互補(bǔ)型堆疊晶體管結(jié)構(gòu)

針對CFET結(jié)構(gòu)設(shè)計(jì)的問題,加利福尼亞大學(xué)圣迭戈分校(以下簡稱UCSD)的研究團(tuán)隊(duì)提出了一個(gè)基于可滿足模性理論(SMT)的CFET標(biāo)準(zhǔn)單元的綜合架構(gòu),解決了后端布局布線的優(yōu)化問題。其成果以以“Complementary-FET (CFET) Standard Cell Synthesis Framework for Design and System Technology Co-Optimization Using SMT”為題發(fā)表于IEEE Transactions on VLSI Systems,UCSD計(jì)算機(jī)科學(xué)與工程學(xué)院與電子計(jì)算機(jī)工程學(xué)院聯(lián)合團(tuán)隊(duì)的Chung-Kuan Cheng(陳中憲)、Chia-Tung Ho、Daeyeal Lee, Bill Lin, and Dongwon Park五人為共同通訊作者。

*設(shè)計(jì)工藝協(xié)同優(yōu)化,全稱Design Technology Co-optimization,是指芯片設(shè)計(jì)與制造共同合作,合作適配最適合芯片設(shè)計(jì)的晶體管結(jié)構(gòu)和工藝的整體優(yōu)化方案,以達(dá)到器件PPAC最優(yōu)解的一種研發(fā)合作模式。

*系統(tǒng)工藝協(xié)同優(yōu)化,全稱System Technology Co-optimization,是指在系統(tǒng)集成層次進(jìn)行優(yōu)化的技術(shù)概念,一般STCO與系統(tǒng)級設(shè)計(jì)意義相近,即在先進(jìn)封裝中實(shí)現(xiàn)對die-to-die互連線路的微縮優(yōu)化,而本文中討論的則是單元(Cell)級內(nèi)部線路優(yōu)化和后道工藝中區(qū)塊級(block-level)布線優(yōu)化。

*Complementary-FET,一種新型晶體管結(jié)構(gòu),通過在垂直方向堆疊p型和n型晶體管實(shí)現(xiàn)CMOS結(jié)構(gòu)。

*標(biāo)準(zhǔn)單元,standard cell是數(shù)字集成電路設(shè)計(jì)中最基本的邏輯單元。

*可滿足模性理論,Satisfiability Modulo Theories,簡稱SMT,數(shù)學(xué)理論概念,在SAT布爾表達(dá)式(由運(yùn)算符AND、OR、NOT和“()”構(gòu)成,又稱命題邏輯公式)可滿足性理論基礎(chǔ)上拓展了其他一階邏輯表達(dá)式,常用于計(jì)算機(jī)科學(xué)領(lǐng)域研究。

研究內(nèi)容

UCSD研究團(tuán)隊(duì)開發(fā)了一個(gè)自動化CFET SDC綜合微縮框架,該框架支持track數(shù)量減少、設(shè)計(jì)規(guī)則改變和晶體管堆疊方案,優(yōu)化了不同CFET SDC結(jié)構(gòu)和設(shè)計(jì)規(guī)則,在以布通率為導(dǎo)向的研究思路下,最大限度利用了pin可達(dá)性(pin accessibility)和布通率(routability)。

除此之外,團(tuán)隊(duì)還研究了集成CSP問題*的SMT解決方案、針對MPL(最小I/O引腳長度)和MPO(最小I/0引腳孔)的單元優(yōu)化技術(shù)等工作,并分析了p-on-n和n-on-p結(jié)構(gòu)下2-4T布線高度*對于器件結(jié)構(gòu)的影響并與傳統(tǒng)晶體管結(jié)構(gòu)進(jìn)行了對比,以及DTCO在前沿技術(shù)節(jié)點(diǎn)中各類優(yōu)化手段與后端工藝實(shí)現(xiàn)結(jié)果的相互作用。

*CSP問題,全稱Constraint Satisfaction Problem,中文意為約束滿足問題,CSP問題將其問題中的單元(entities)表示成在變量上有限條件的一組同質(zhì)(homogeneous)的集合, 這類問題透過“約束補(bǔ)償方法”來解決,是人工智能和運(yùn)籌學(xué)的熱門課題。

*布線高度,指一個(gè)標(biāo)準(zhǔn)單元的高度,用“數(shù)字+T”來表示,T指track,電信號的傳輸線路必須走在track上,數(shù)字表示track數(shù)量,即單元高度內(nèi)允許布線的數(shù)量。

優(yōu)化方案的整體框架

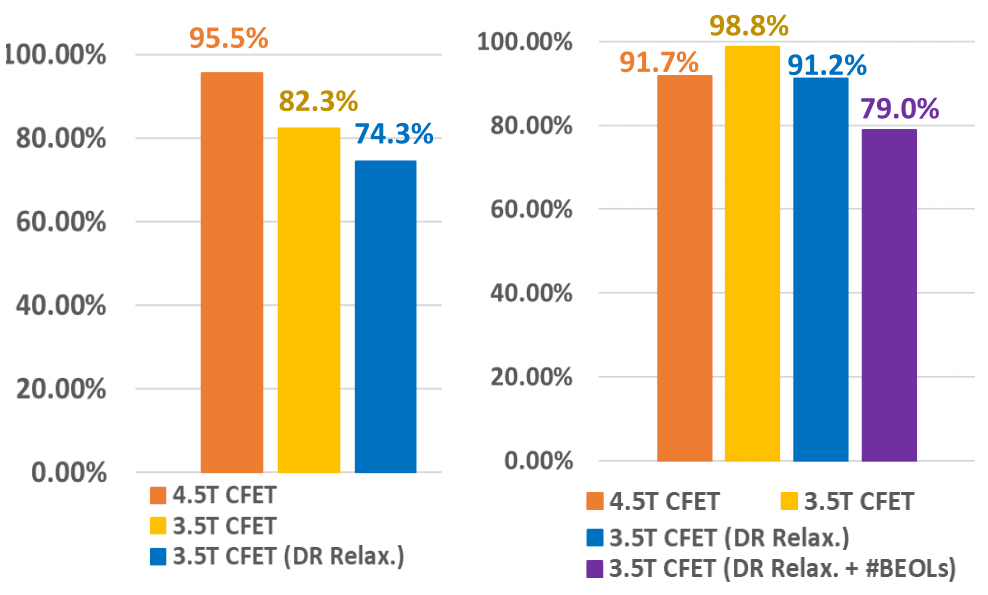

單元和模塊級的面積縮放增益對比:

左為單元面積變化;右為模塊級面積變化

研究團(tuán)隊(duì)通過實(shí)驗(yàn)發(fā)現(xiàn)與傳統(tǒng)晶體管結(jié)構(gòu)相比,微縮至3.5T高度的CFET結(jié)構(gòu)的平均單元面積和金屬長度分別減少了10.94%和21.27%,模塊級平均面積減少了15.10%,并且大幅降低了DRV(Design Rule Violation)。

前景展望

文章介紹了沿著當(dāng)前先進(jìn)制程主要的三大實(shí)現(xiàn)路徑,即:新器件結(jié)構(gòu)、DCTO協(xié)同優(yōu)化和系統(tǒng)級設(shè)計(jì)三個(gè)方向,針對CFET以及實(shí)現(xiàn)這一前沿新型晶體管結(jié)構(gòu)性能增益必要的兩大協(xié)同優(yōu)化技術(shù)進(jìn)行了探究。繼IMEC等研究領(lǐng)域的排頭兵提出和驗(yàn)證了新結(jié)構(gòu)的可行性,業(yè)界已經(jīng)認(rèn)可了CFET的應(yīng)用前景并全面跟進(jìn),包括英特爾、臺積電-臺灣TSRI-日本AIST、應(yīng)用材料等企業(yè)和研究機(jī)構(gòu)都開始著手布局相關(guān)的研究和技術(shù)儲備,在常規(guī)的晶體管尺寸微縮越來越難以獲得理想的性能增益的情況下,每一次集成電路工藝的進(jìn)步都凝聚著產(chǎn)業(yè)鏈上下各個(gè)環(huán)節(jié)的研究成果,我們也期待著CFET等新技術(shù)的研發(fā)成功和應(yīng)用落地那一天盡快到來。

原文標(biāo)題:科研前線 | 未來會來嗎?摩爾定律大殺器CFET研究又有新成果

文章出處:【微信公眾號:芯片揭秘】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

責(zé)任編輯:haq

-

集成電路

+關(guān)注

關(guān)注

5453文章

12574瀏覽量

374681 -

晶體管

+關(guān)注

關(guān)注

78文章

10396瀏覽量

147852

原文標(biāo)題:科研前線 | 未來會來嗎?摩爾定律大殺器CFET研究又有新成果

文章出處:【微信號:ICxpjm,微信公眾號:芯片揭秘】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

MUN5136數(shù)字晶體管技術(shù)解析與應(yīng)用指南

電壓選擇晶體管應(yīng)用電路第二期

英飛凌功率晶體管的短路耐受性測試

晶體管的基本結(jié)構(gòu)和發(fā)展歷程

多值電場型電壓選擇晶體管結(jié)構(gòu)

晶體管架構(gòu)的演變過程

下一代高速芯片晶體管解制造問題解決了!

鰭式場效應(yīng)晶體管的原理和優(yōu)勢

薄膜晶體管技術(shù)架構(gòu)與主流工藝路線

無結(jié)場效應(yīng)晶體管詳解

什么是晶體管?你了解多少?知道怎樣工作的嗎?

多值電場型電壓選擇晶體管結(jié)構(gòu)

多值電場型電壓選擇晶體管結(jié)構(gòu)

晶體管電路設(shè)計(jì)(下)

晶體管柵極結(jié)構(gòu)形成

晶體管物理結(jié)構(gòu)實(shí)現(xiàn)的兩類協(xié)同優(yōu)化技術(shù)探究

晶體管物理結(jié)構(gòu)實(shí)現(xiàn)的兩類協(xié)同優(yōu)化技術(shù)探究

評論