摘要:自動(dòng)測(cè)試設(shè)備 (ATE) 技術(shù)緊跟半導(dǎo)體IC 及其測(cè)試設(shè)備的趨勢(shì)。隨著帶寬、集成度和成本壓力的增加,下一代 ATE 系統(tǒng)需要更高的密度和更高的吞吐量來滿足最新的半導(dǎo)體需求。

介紹

在多個(gè)大趨勢(shì)的推動(dòng)下,推動(dòng)世界對(duì)半導(dǎo)體需求的技術(shù)繁榮依然強(qiáng)勁。無線基礎(chǔ)設(shè)施、物聯(lián)網(wǎng)、人工智能、數(shù)據(jù)中心和電動(dòng)汽車是推動(dòng)對(duì)先進(jìn)半導(dǎo)體 IC 需求增加的應(yīng)用示例。隨著每個(gè)單獨(dú)的 IC 中包含更多功能,測(cè)試要求也會(huì)增加,降低成本變得更具挑戰(zhàn)性。半導(dǎo)體制造商如何提高其最終產(chǎn)品的復(fù)雜性,同時(shí)降低測(cè)試成本?

測(cè)試系統(tǒng)未標(biāo)準(zhǔn)化

從廣義上講,半導(dǎo)體開發(fā)過程包括設(shè)計(jì)、制造和測(cè)試。今天,IC 設(shè)計(jì)人員使用 EDA(電子設(shè)計(jì)自動(dòng)化)軟件工具。這些工具是標(biāo)準(zhǔn)化的,大大簡(jiǎn)化了設(shè)計(jì)過程。晶圓的制造設(shè)備在一定程度上也是標(biāo)準(zhǔn)化的,因?yàn)樵S多工藝和設(shè)備是代代相傳的。ATE 系統(tǒng)不能這樣說。缺乏標(biāo)準(zhǔn)和 IC 復(fù)雜性的增加導(dǎo)致測(cè)試成本上升。研究表明,封裝和測(cè)試占產(chǎn)品總成本的 50% 到 70% 之間。

降低測(cè)試成本

降低測(cè)試成本的一個(gè)明顯方法是采用更高的并行度并同時(shí)測(cè)試多個(gè)部分。每當(dāng) ATE 系統(tǒng)并行測(cè)試更多部件時(shí),吞吐量就會(huì)提高。例如,如果之前的測(cè)試平臺(tái)可以并行測(cè)試四個(gè)設(shè)備,總測(cè)試時(shí)間為 10 秒,那么每個(gè)設(shè)備測(cè)試是 2.5 秒。使用每秒 0.02 美元的假設(shè)成本,那么每個(gè)設(shè)備都有 0.05 美元的測(cè)試成本。通過將 ATE 系統(tǒng)升級(jí)到八進(jìn)制站點(diǎn)甚至 16 個(gè)站點(diǎn)的測(cè)試儀,測(cè)試成本顯著下降,分別為 0.025 美元和 0.0125 美元。與 16 個(gè)站點(diǎn)的測(cè)試設(shè)置相比,這項(xiàng) 75% 的測(cè)試成本節(jié)省比原始測(cè)試成本節(jié)省了 0.0375 美元。

接下來,想象一下總測(cè)試時(shí)間是否可以減少一半。由于 ATE 生產(chǎn)車間測(cè)試工程師將最大限度地利用資源來測(cè)試器件,因此減少測(cè)試時(shí)間的方法是提高驅(qū)動(dòng)信號(hào)到被測(cè)器件 (DUT) 和比較器信號(hào)返回到FPGA的速度。驅(qū)動(dòng)器和比較器 IC 所在的引腳電子速度提高了 2 倍,將測(cè)試時(shí)間縮短了一半。計(jì)算測(cè)試成本的數(shù)學(xué)與前面的示例一樣簡(jiǎn)單。測(cè)試 16 臺(tái)設(shè)備需要 5 秒,而不是 10 秒。這意味著每臺(tái)設(shè)備的測(cè)試成本為 0.00625 美元,是 0.0125 美元的一半。雖然實(shí)際測(cè)試時(shí)間各不相同,但這個(gè)假設(shè)示例清楚地展示了更快系統(tǒng)和更高密度卡的潛在節(jié)省。

更高的密度和速度

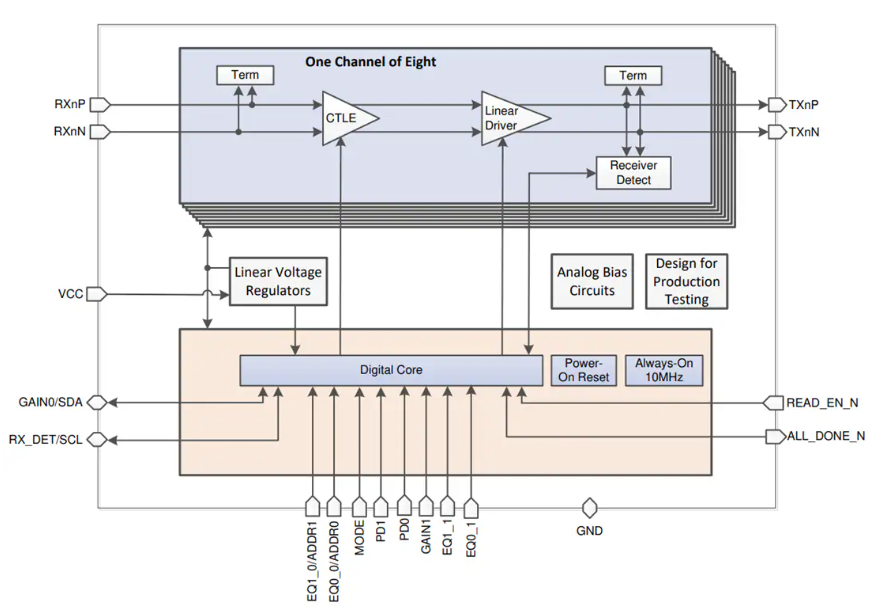

前面提到的引腳電子驅(qū)動(dòng)板具有驅(qū)動(dòng)器和比較器 IC。圖 1中的 ATE 框圖顯示了MAX32007所在的位置(DCL + DAC + SWITCHES 盒)。MAX32007 是 ADI 最新發(fā)布的 8 通道 3Gbps 引腳驅(qū)動(dòng)器。

電纜下垂補(bǔ)償

由于PCB上的長(zhǎng)跡線和/或長(zhǎng)或有損耗的同軸電纜,驅(qū)動(dòng)到 DUT 的波形和返回信號(hào)可能會(huì)衰減或退化。當(dāng)波形受到這種影響時(shí),有效數(shù)據(jù)速率會(huì)降??低,或者更糟的是,數(shù)據(jù)無法使用,從而影響測(cè)試的吞吐量和成本。MAX32007 在輸出波形中加入了長(zhǎng) (CDRPL) 和短 (CDRPS) 雙時(shí)間常數(shù),通過受控量的過沖和下沖來恢復(fù)圓潤(rùn)邊沿。

結(jié)論

結(jié)論

隨著半導(dǎo)體 IC 不斷跟上最新的技術(shù)需求,測(cè)試它們所需的自動(dòng)化測(cè)試設(shè)備也必須如此。Pin 電子驅(qū)動(dòng)器在處理這種技術(shù)激增方面發(fā)揮著關(guān)鍵作用,更高密度和更高數(shù)據(jù)速率可實(shí)現(xiàn)下一代設(shè)備的高吞吐量和更低的測(cè)試成本。

介紹

在多個(gè)大趨勢(shì)的推動(dòng)下,推動(dòng)世界對(duì)半導(dǎo)體需求的技術(shù)繁榮依然強(qiáng)勁。無線基礎(chǔ)設(shè)施、物聯(lián)網(wǎng)、人工智能、數(shù)據(jù)中心和電動(dòng)汽車是推動(dòng)對(duì)先進(jìn)半導(dǎo)體 IC 需求增加的應(yīng)用示例。隨著每個(gè)單獨(dú)的 IC 中包含更多功能,測(cè)試要求也會(huì)增加,降低成本變得更具挑戰(zhàn)性。半導(dǎo)體制造商如何提高其最終產(chǎn)品的復(fù)雜性,同時(shí)降低測(cè)試成本?

測(cè)試系統(tǒng)未標(biāo)準(zhǔn)化

從廣義上講,半導(dǎo)體開發(fā)過程包括設(shè)計(jì)、制造和測(cè)試。今天,IC 設(shè)計(jì)人員使用 EDA(電子設(shè)計(jì)自動(dòng)化)軟件工具。這些工具是標(biāo)準(zhǔn)化的,大大簡(jiǎn)化了設(shè)計(jì)過程。晶圓的制造設(shè)備在一定程度上也是標(biāo)準(zhǔn)化的,因?yàn)樵S多工藝和設(shè)備是代代相傳的。ATE 系統(tǒng)不能這樣說。缺乏標(biāo)準(zhǔn)和 IC 復(fù)雜性的增加導(dǎo)致測(cè)試成本上升。研究表明,封裝和測(cè)試占產(chǎn)品總成本的 50% 到 70% 之間。

降低測(cè)試成本

降低測(cè)試成本的一個(gè)明顯方法是采用更高的并行度并同時(shí)測(cè)試多個(gè)部分。每當(dāng) ATE 系統(tǒng)并行測(cè)試更多部件時(shí),吞吐量就會(huì)提高。例如,如果之前的測(cè)試平臺(tái)可以并行測(cè)試四個(gè)設(shè)備,總測(cè)試時(shí)間為 10 秒,那么每個(gè)設(shè)備測(cè)試是 2.5 秒。使用每秒 0.02 美元的假設(shè)成本,那么每個(gè)設(shè)備都有 0.05 美元的測(cè)試成本。通過將 ATE 系統(tǒng)升級(jí)到八進(jìn)制站點(diǎn)甚至 16 個(gè)站點(diǎn)的測(cè)試儀,測(cè)試成本顯著下降,分別為 0.025 美元和 0.0125 美元。與 16 個(gè)站點(diǎn)的測(cè)試設(shè)置相比,這項(xiàng) 75% 的測(cè)試成本節(jié)省比原始測(cè)試成本節(jié)省了 0.0375 美元。

接下來,想象一下總測(cè)試時(shí)間是否可以減少一半。由于 ATE 生產(chǎn)車間測(cè)試工程師將最大限度地利用資源來測(cè)試器件,因此減少測(cè)試時(shí)間的方法是提高驅(qū)動(dòng)信號(hào)到被測(cè)器件 (DUT) 和比較器信號(hào)返回到FPGA的速度。驅(qū)動(dòng)器和比較器 IC 所在的引腳電子速度提高了 2 倍,將測(cè)試時(shí)間縮短了一半。計(jì)算測(cè)試成本的數(shù)學(xué)與前面的示例一樣簡(jiǎn)單。測(cè)試 16 臺(tái)設(shè)備需要 5 秒,而不是 10 秒。這意味著每臺(tái)設(shè)備的測(cè)試成本為 0.00625 美元,是 0.0125 美元的一半。雖然實(shí)際測(cè)試時(shí)間各不相同,但這個(gè)假設(shè)示例清楚地展示了更快系統(tǒng)和更高密度卡的潛在節(jié)省。

更高的密度和速度

前面提到的引腳電子驅(qū)動(dòng)板具有驅(qū)動(dòng)器和比較器 IC。圖 1中的 ATE 框圖顯示了MAX32007所在的位置(DCL + DAC + SWITCHES 盒)。MAX32007 是 ADI 最新發(fā)布的 8 通道 3Gbps 引腳驅(qū)動(dòng)器。

圖 1. 通用 ATE 系統(tǒng)框圖。

高密度、八通道、高速 3Gbps MAX32007 具有集成的 14 位電平設(shè)置 DAC、電纜下垂補(bǔ)償和壓擺率控制,可優(yōu)化 DUT 的波形。電纜下垂補(bǔ)償

由于PCB上的長(zhǎng)跡線和/或長(zhǎng)或有損耗的同軸電纜,驅(qū)動(dòng)到 DUT 的波形和返回信號(hào)可能會(huì)衰減或退化。當(dāng)波形受到這種影響時(shí),有效數(shù)據(jù)速率會(huì)降??低,或者更糟的是,數(shù)據(jù)無法使用,從而影響測(cè)試的吞吐量和成本。MAX32007 在輸出波形中加入了長(zhǎng) (CDRPL) 和短 (CDRPS) 雙時(shí)間常數(shù),通過受控量的過沖和下沖來恢復(fù)圓潤(rùn)邊沿。

圖 2. 驅(qū)動(dòng)器電纜下垂補(bǔ)償?shù)母拍畋硎尽?/font>

補(bǔ)償量可以通過一個(gè) 3 位內(nèi)部寄存器從 0 到 10% 進(jìn)行編程。圖 3中的示波器顯示了電纜下垂補(bǔ)償如何幫助信號(hào)保真度克服 24 英寸 50Ω 同軸電纜上的劣化波形的示例。外部綠色跡線表示應(yīng)用到波形的 10% 補(bǔ)償,內(nèi)部跡線顯示 0% 補(bǔ)償。

圖 3. 電纜下垂補(bǔ)償?shù)姆秶臄z。

隨著半導(dǎo)體 IC 不斷跟上最新的技術(shù)需求,測(cè)試它們所需的自動(dòng)化測(cè)試設(shè)備也必須如此。Pin 電子驅(qū)動(dòng)器在處理這種技術(shù)激增方面發(fā)揮著關(guān)鍵作用,更高密度和更高數(shù)據(jù)速率可實(shí)現(xiàn)下一代設(shè)備的高吞吐量和更低的測(cè)試成本。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

L9659八通道爆管驅(qū)動(dòng)器ASIC:安全應(yīng)用的理想之選

L9659八通道爆管驅(qū)動(dòng)器ASIC:安全應(yīng)用的理想之選 在當(dāng)今復(fù)雜的電子系統(tǒng)中,安全應(yīng)用一直是重中之重。對(duì)于航空、汽車等領(lǐng)域的安全氣囊系統(tǒng)而

八通道智能驅(qū)動(dòng)器SiLM92108,集成驅(qū)動(dòng)與診斷,簡(jiǎn)化多電機(jī)系統(tǒng)設(shè)計(jì)

:

汽車車身控制:車窗升降、天窗調(diào)節(jié)、座椅調(diào)節(jié)、后視鏡折疊及電動(dòng)尾門系統(tǒng)

工業(yè)自動(dòng)化:多軸小型電機(jī)控制、機(jī)器人關(guān)節(jié)驅(qū)動(dòng)、工控傳動(dòng)裝置

智能機(jī)電系統(tǒng):家用電動(dòng)設(shè)備、智能家居執(zhí)行機(jī)構(gòu)及商用智能柜鎖

#

發(fā)表于 01-09 08:22

英飛凌下一代電磁閥驅(qū)動(dòng)器評(píng)估套件使用指南

英飛凌下一代電磁閥驅(qū)動(dòng)器評(píng)估套件使用指南 引言 作為電子工程師,我們?cè)陂_發(fā)電磁閥驅(qū)動(dòng)相關(guān)項(xiàng)目時(shí),一款好用的評(píng)估套件能大大提高我們的開發(fā)效率。

英飛凌下一代電磁閥驅(qū)動(dòng)器評(píng)估套件使用指南

英飛凌下一代電磁閥驅(qū)動(dòng)器評(píng)估套件使用指南 一、前言 在電子工程師的日常工作中,電磁閥驅(qū)動(dòng)器的評(píng)估和開發(fā)是

探索NCV7755:八通道高端驅(qū)動(dòng)器的卓越性能與應(yīng)用潛力

在汽車電子和工業(yè)控制領(lǐng)域,高端驅(qū)動(dòng)器的性能和可靠性直接影響著整個(gè)系統(tǒng)的運(yùn)行。今天,我們將深入探討安森美(onsemi)的NCV7755八通道高端驅(qū)動(dòng)

最高支持9200 MT/s速率!瀾起科技推出新一代DDR5時(shí)鐘驅(qū)動(dòng)器(CKD)芯片

電子發(fā)燒友網(wǎng)綜合報(bào)道 11月10日,瀾起科技正式推出新一代DDR5時(shí)鐘驅(qū)動(dòng)器(CKD)芯片,該芯片最高支持9200 MT/s的數(shù)據(jù)傳輸速率,可有效優(yōu)化客戶端內(nèi)存子系統(tǒng)性能,為下

Melexis推出第四代汽車LIN電機(jī)驅(qū)動(dòng)器MLX81350

Melexis推出第四代汽車LIN電機(jī)驅(qū)動(dòng)器MLX81350,可為電機(jī)提供高達(dá)5W(0.5A)的功率。該驅(qū)動(dòng)器專為電動(dòng)汽車(EV)的空調(diào)風(fēng)門與自動(dòng)通風(fēng)系統(tǒng)設(shè)計(jì),具備高性價(jià)比,不僅能實(shí)現(xiàn)

DS320PR810八通道線性轉(zhuǎn)接驅(qū)動(dòng)器技術(shù)解析與應(yīng)用指南

Texas Instruments DS320PR810八通道轉(zhuǎn)接驅(qū)動(dòng)器是一款低功耗、高性能線性中繼器或轉(zhuǎn)接驅(qū)動(dòng)器,設(shè)計(jì)用于支持PCIe 5

?TLC5960八通道LED驅(qū)動(dòng)器技術(shù)手冊(cè)總結(jié)

TLC5960是一款八通道PWM LED驅(qū)動(dòng)器,具有四個(gè)智能裕量電壓監(jiān)測(cè)器(iHVM)輸出。LED 驅(qū)動(dòng)器具有可擴(kuò)展的高壓能力,并在 LED

專為汽車DC電機(jī)打造 亞成微電子新一代全集成智能H橋電機(jī)驅(qū)動(dòng)器RM44150DS發(fā)布

? 在汽車電子追求智能、高效、穩(wěn)定與低能耗的行業(yè)趨勢(shì)下,亞成微敏銳洞察行業(yè)需求變化,正式推出 新一代全集成智能H橋電機(jī)驅(qū)動(dòng)器RM44150DS ,為客戶提供更具競(jìng)爭(zhēng)力的解決方案。 ·? 產(chǎn)品介紹

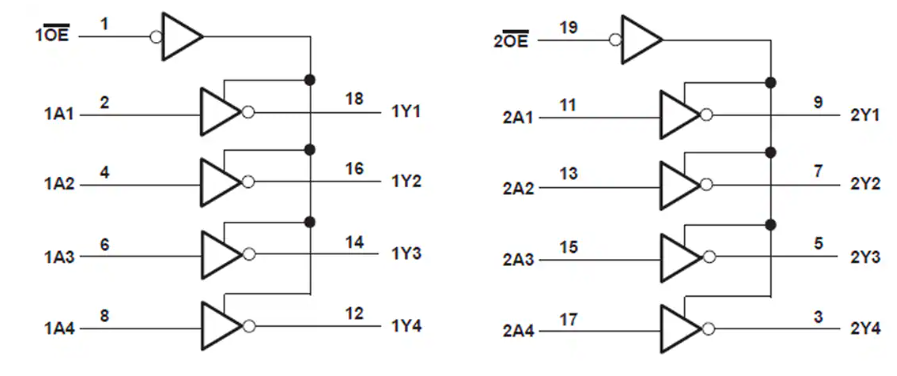

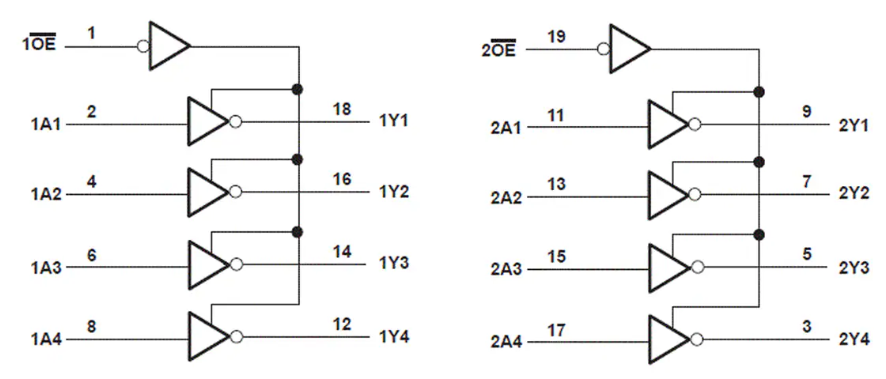

Texas Instruments SN74HCT240八通道緩沖器/線路驅(qū)動(dòng)器數(shù)據(jù)手冊(cè)

Texas Instruments SN74HCT240八通道緩沖器/線路驅(qū)動(dòng)器專門設(shè)計(jì)用于改善時(shí)鐘驅(qū)動(dòng)器、三態(tài)存儲(chǔ)器地址

Texas Instruments SN74HC240八通道緩沖器/線路驅(qū)動(dòng)器數(shù)據(jù)手冊(cè)

Texas Instruments SN74HC240八通道緩沖器/線路驅(qū)動(dòng)器專門設(shè)計(jì)用于改善時(shí)鐘驅(qū)動(dòng)器、三態(tài)存儲(chǔ)器地址

三色變光的驅(qū)動(dòng)器和單色的驅(qū)動(dòng)器能通用么?

在LED照明領(lǐng)域,驅(qū)動(dòng)器的選擇直接影響燈具的性能和壽命。關(guān)于三色變光驅(qū)動(dòng)器與單色驅(qū)動(dòng)器能否通用的問題,需要從工作原理、電路設(shè)計(jì)、兼容性等多個(gè)維度進(jìn)行深入分析。

SEGGER推出新一代Flasher ATE在線編程器

2025年5月,SEGGER推出了新一代的Flasher ATE在線編程器Flasher ATE2。該設(shè)備的外形緊湊,可以安裝在機(jī)架上或直接安裝在A

寶馬發(fā)布全新一代智能電子電氣架構(gòu)

"超級(jí)大腦"賦能寶馬新世代車型智能駕駛樂趣 全新一代電子電氣架構(gòu)搭載新世代車型,覆蓋全動(dòng)力系統(tǒng)和全細(xì)分車型 全新一代電子電氣架構(gòu)集成算力提升20倍,支持AI用戶體驗(yàn)和場(chǎng)景 全新一代電子

新一代ATE系統(tǒng)中新型八針電子驅(qū)動(dòng)器分析

新一代ATE系統(tǒng)中新型八針電子驅(qū)動(dòng)器分析

評(píng)論