隨著光芯片傳輸速率的提高,傳統的RC提取工具是否已經達到了瓶頸?面對多種工藝,更小的互聯尺寸,如何才能實現寄生參數的精確提取?有沒有一種低迭代,智能的無源建模方法?

01光芯片市場概況

得益于三大下游市場(電信、數據中心、消費電子)需求的持續井噴,2021年光芯片市場規模將爆發式增長,達到25億美元。從細分市場份額來看,電信占60%,數據中心占30%,消費電子占10%。 光芯片行業,具有極高的技術壁壘和復雜的工藝流程。因此,光芯片在光器件/光模塊中成本占比較大。對于高速光模塊(>25Gbps),芯片的成本占比約為60%左右。相較于電芯片,目前光芯片市場規模較小,主要采用垂直一體化的IDM運營模式。但伴隨VCSEL芯片的消費電子市場打開,將逐步興起設計公司+專業代工的模式。

02光芯片電磁仿真的挑戰

1.更高的數據傳輸速率

當前主流的光芯片接口速率為單通道56Gbps,業界最先進的可達到112Gbps,相信隨著工藝的進步和終端用戶對數據吞吐的進一步需求,速率會更高。從無源參數提取的角度,這是個寬頻的應用,最高的頻率已經達到毫米波。在如此復雜的電磁環境下,寄生參數的特性具有頻變的特性,同時為了滿足仿真精度必須要包含空間的電磁耦合。這些需求給電磁仿真器提出了更高的要求。

2.版圖規模極大地增加

光芯片的集成度越來越高,都在往SOC的方向去實現。根據我們實際項目的經驗,四通道光芯片版圖的尺寸為1至2平方毫米,隨著通道數增多,則版圖尺寸會進一步的增大。除了必要的電感和互聯外,版圖還包括了大量的高密度電容結構,這些結構將仿真的規模提高了一個數量級。在端口方面,普通版圖的電磁仿真通常需要50個左右的端口,而光芯片需要應對的端口數量翻了幾倍,最高甚至可以達到500個,這使得設計者在有限的硬件資源下很難快速得到精確的仿真數據。

3.復雜的多工藝場景

光芯片設計需要充分利用不同工藝的優勢,來提高電路的性能。目前主流的工藝包括CMOS 和SiGe Bi-CMOS。CMOS 工藝是低功耗設計首要的選擇,但它的噪聲性能相對較差,跨阻增益和帶寬指標也劣于 SiGe 工藝。SiGe BiCMOS 高于 CMOS 的優異性能使得設計具有高性能的高速電路成為可能,同時它還將功耗限制在可接受的水平。對于電磁提取來說,需要針對不同工藝下的襯底結構、金屬層次等進行有針對性的建模,才能更好的對信號損耗進行模擬。 綜上所述,在光芯片設計中我們將面對“更高的數據傳輸速率、版圖規模極大增加及復雜的多工藝場景”等諸多挑戰。接下來,我們將為您介紹芯和光芯片電磁仿真EDA解決方案是如何一步步解決上述難題的。

03芯和光芯片電磁仿真EDA解決方案

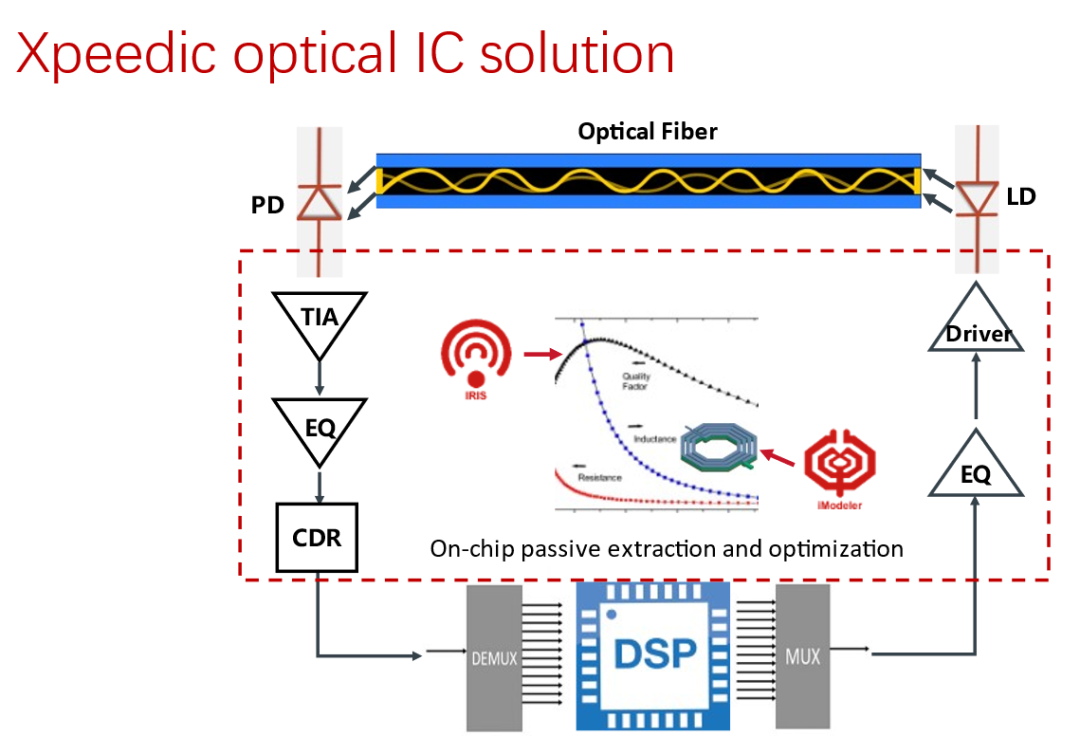

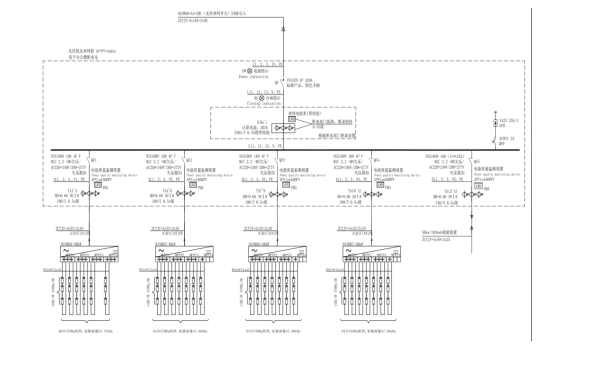

光通信芯片設計一般指的是如下紅色虛線范圍內的模塊設計,包括TIA/EQ/CDR/Driver。本文我們介紹的解決方案希望能幫助設計師針對所有這些模塊進行高效的無源結構提取、建模和優化。

圖1芯和EDA光芯片設計方案

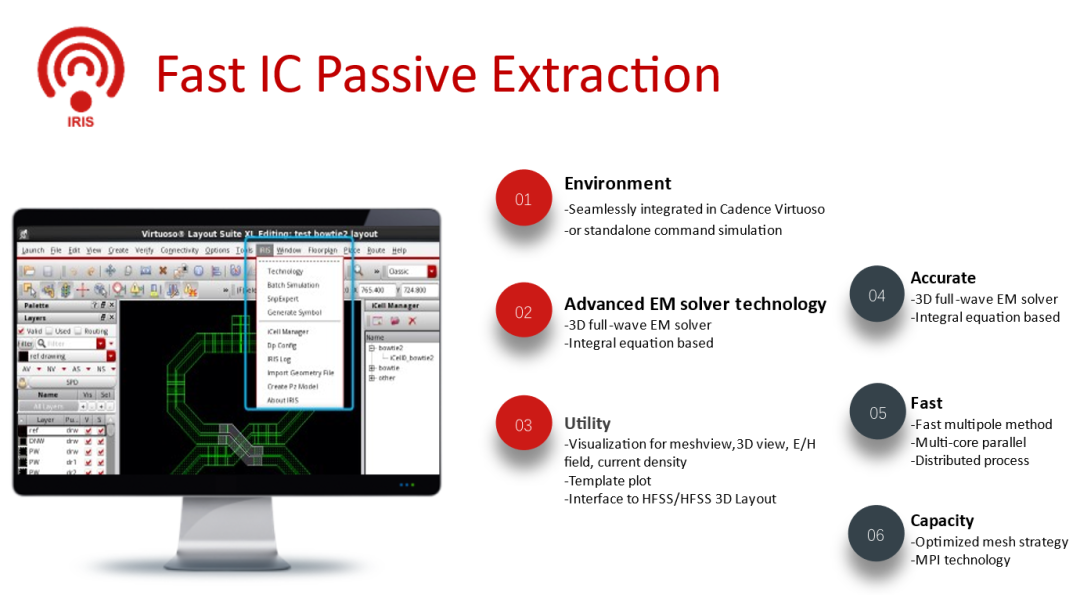

1.無源結構快速提取

我們提供了一種基于Cadence Virtuoso設計平臺的提取工具IRIS,并通過了代工廠在CMOS/ SiGe工藝上的嚴格認證。IRIS結合3D全波求解技術,滿足從DC到毫米波段的提取精度要求。使用者可以靈活運用多線程/多核技術、MPI多機處理將復雜的仿真問題分片化,提高仿真的效率。

圖2 快速的電磁提取方案-IRIS

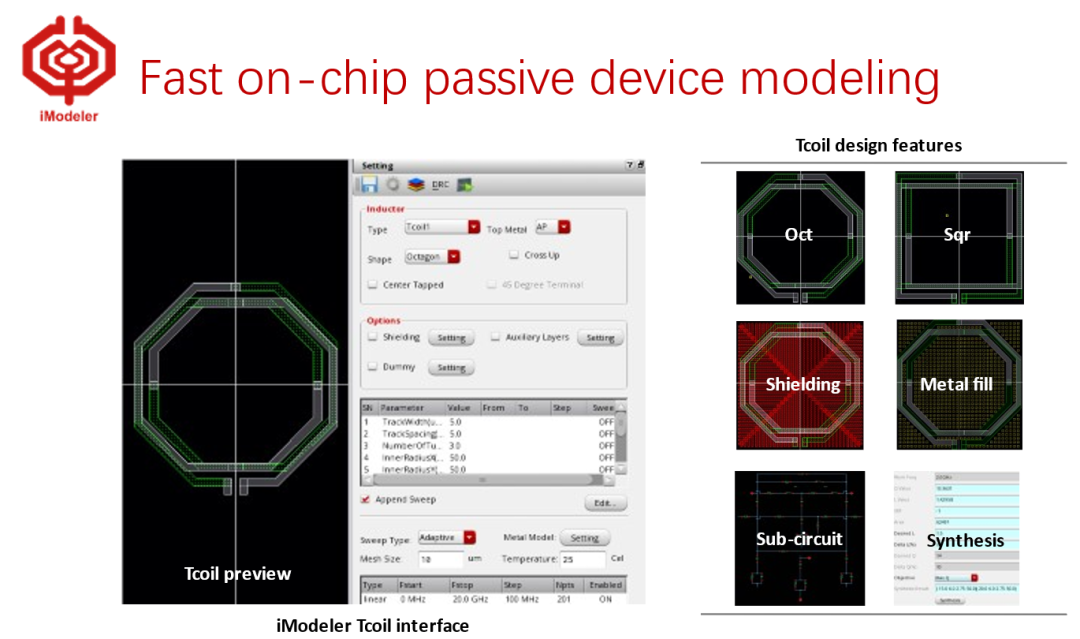

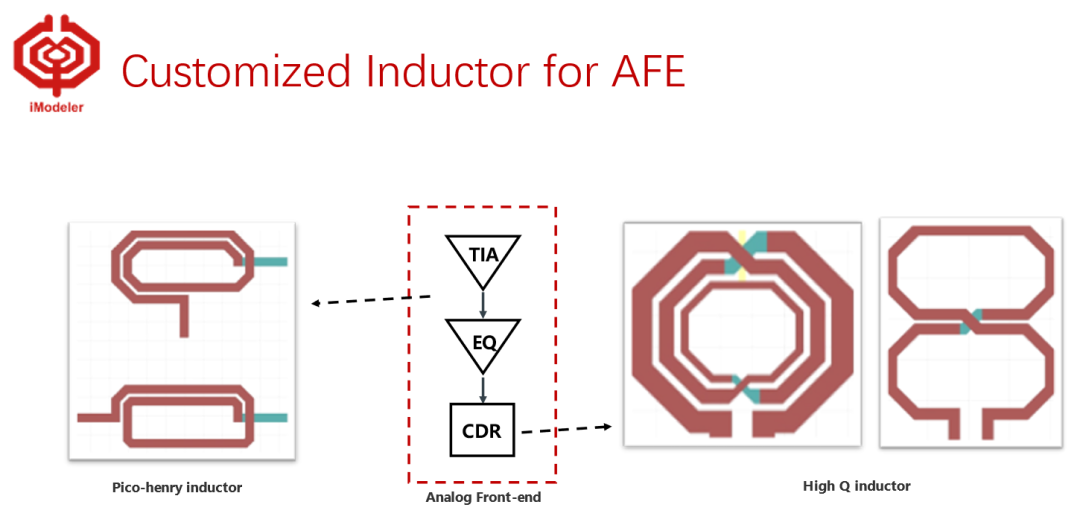

2.無源結構高效建模

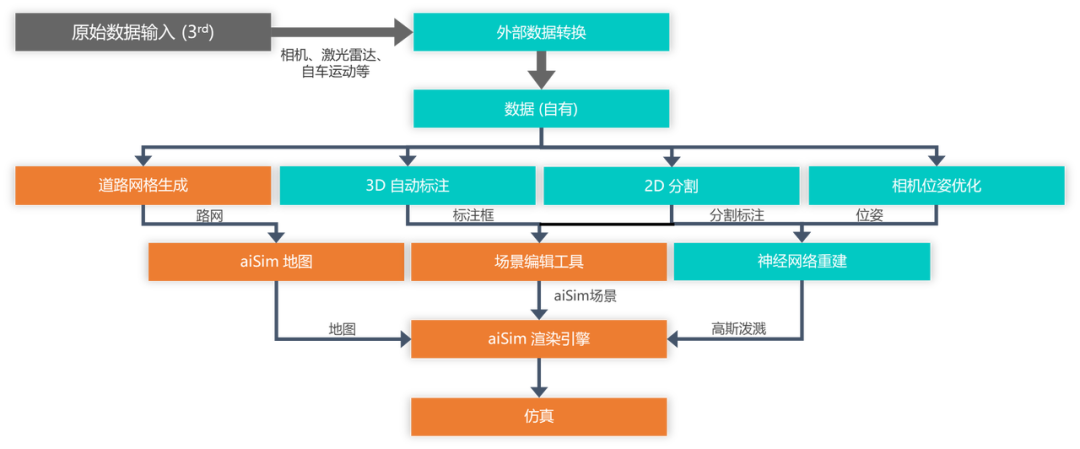

我們提供了基于神經網絡算法的無源器件定制平臺iModeler。它內建了多套面向光芯片設計的電感模板。使用者利用模板內的多種輔助選項,可輕松實現電感的多項指標優化。

圖3一站式建模流程-iModeler

04驗證對比

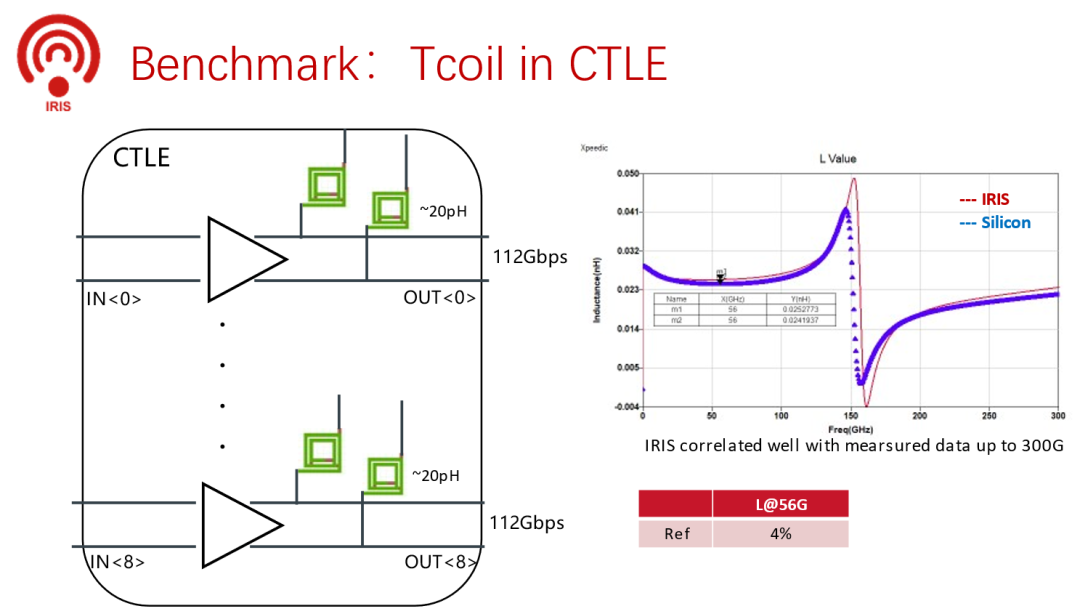

運用以上的解決方案,我們針對CTLE模塊中的小電感進行了實測對比,發現IRIS的結果在DC-300G整個頻率范圍內和測試都吻合的很好,最大偏差僅在4%以內。

圖4仿真測試結果對比

05總結

本文介紹了光芯片設計在電磁仿真方面面臨的三大挑戰,即更高的數據傳輸速率、版圖規模極大增加及復雜的多工藝場景。芯和半導體針對這些挑戰,推出了高效的光通信芯片電磁提取解決方案:利用IRIS/iModeler軟件,實現了快速高精度電磁提取,無源器件優化建模等應用,極大地降低了設計師的迭代次數和產品投放市場周期。 了解更多應用案例和技術資料,請點擊"閱讀原文"。

芯和半導體EDA介紹

芯和半導體成立于2010年,是國內唯一提供“半導體全產業鏈仿真EDA解決方案”的供應商。芯和半導體EDA是新一代智能電子產品中設計高頻/高速電子組件的首選工具,它包括了三大產品線:

芯片設計仿真產品線為晶圓廠提供了精準的PDK設計解決方案, 為芯片設計公司提供了片上高頻寄生參數提取與建模的解決方案;

先進封裝設計仿真產品線為傳統型封裝和先進封裝提供了高速高頻電磁場仿真的解決方案;

高速系統設計仿真產品線為PCB板、組件、系統的互連結構提供了快速建模與無源參數抽取的仿真平臺,解決了高速高頻系統中的信號、電源完整性問題。

芯和半導體EDA的強大功能基于:自主知識產權的多種尖端電磁場和電路仿真求解技術、繁榮的晶圓廠和合作伙伴生態圈(芯和半導體EDA在所有主流晶圓廠的先進工藝節點和先進封裝上得到了不斷驗證)、以及支持基于云平臺的高性能分布式計算技術,在5G、智能手機、物聯網、汽車電子和數據中心等領域已得到廣泛應用。

關于芯和半導體

芯和半導體是國產EDA行業的領軍企業,提供覆蓋IC、封裝到系統的全產業鏈仿真EDA解決方案,致力于賦能和加速新一代高速高頻智能電子產品的設計。

芯和半導體自主知識產權的EDA產品和方案在半導體先進工藝節點和先進封裝上不斷得到驗證,并在5G、智能手機、物聯網、人工智能、數據中心和汽車電子等領域得到廣泛應用,有效聯結了各大IC設計公司與制造公司。

芯和半導體同時在全球5G射頻前端供應鏈中扮演重要角色,其通過自主創新的濾波器和系統級封裝設計平臺為手機和物聯網客戶提供射頻前端濾波器和模組,并被Yole評選為全球IPD濾波器領先供應商。

芯和半導體創建于2010年,前身為芯禾科技,運營及研發總部位于上海張江,在蘇州、武漢設有研發分中心,在美國硅谷、北京、深圳、成都、西安設有銷售和技術支持部門。如欲了解更多詳情,敬請訪問 www.xpeedic.cn。

編輯:jq

-

芯片

+關注

關注

463文章

54010瀏覽量

466034 -

電磁

+關注

關注

15文章

1193瀏覽量

53944

原文標題:光芯片電磁仿真解決方案

文章出處:【微信號:Xpeedic,微信公眾號:Xpeedic】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

直流固態變壓器控制策略仿真解決方案

Altair Feko:引領高性能電磁仿真與優化解決方案

深度解析:康謀雙模態仿真測試解決方案!

電磁干擾自適應抑制系統平臺全面解析

從電機優化到性能飛升!ANSYS Maxwell 低頻電磁場仿真全解析

光伏電池發電系統實時仿真

數據中心防光儲充解決方案光伏電力零逆流并網

芯知識|廣州唯創電子語音芯片輸出聲音小問題解析及解決方案

光庭信息在2025上海車展展示先進智能駕駛解決方案

精彩回顧 | 《電磁兼容仿真技術與電源EMC問題解析》直播圓滿結束!

解析光芯片電磁仿真解決方案

解析光芯片電磁仿真解決方案

評論