一、介紹

在同步系統中,數據始終相對于時鐘具有固定的關系 當該關系滿足設備的建立和保持要求時,輸出將在其指定的傳播延遲時間內進入有效狀態。在同步系統中,輸入信號始終滿足觸發器的時序要求。因此,不會發生亞穩性。但是,在異步系統中,數據和時鐘之間的關系不是固定的。因此,會偶爾發生違反建立時間和保持時序的情況。發生這種建立和保持時序的情況時,輸出可能會到達其兩個有效狀態(0和1)之間的中間水平,不穩定的狀態(0和1之外的狀態即亞穩態)保持的時間也是不確定的,直到自己進入穩態。

二、亞穩態理論

由于違反了觸發器的建立和保持時間,因此會產生亞穩定性。在任何設計中使用的每個觸發器都有指定的建立和保持時間,或者說是在時鐘上升沿之前和之后不允許輸入數據變化的時間。如果信號在此時間窗口內確實發生變化,則輸出將是未知的或“亞穩的”。這種有害狀態的傳播稱為亞穩態。結果,觸發器的輸出會產生毛刺或暫時保持在亞穩狀態,因此需要更長的時間才能返回到穩定狀態。

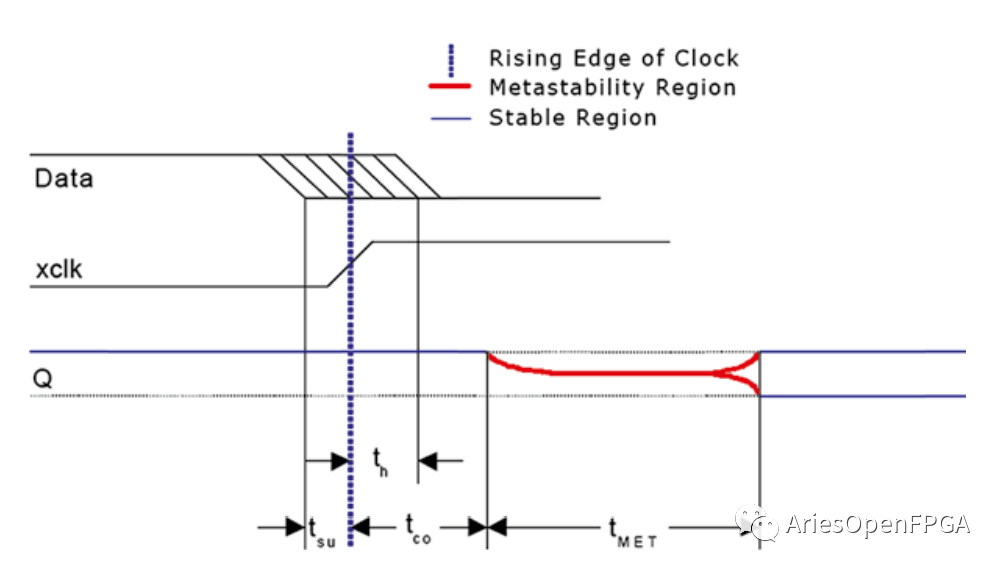

當觸發器處于亞穩態時,輸出會在高電平和低電平之間徘徊,導致輸出轉換被延遲,并超過指定的時鐘到輸出延遲(tco)。亞穩態輸出需要花費超過tco的額外時間才能解析為穩定狀態,該時間稱為穩定時間(tMET)。

圖1.1亞穩時序參數

這已在圖1.1中顯示,但并非每個違反建立或保持時間的轉換(數據轉換)都會導致亞穩態輸出。觸發器進入亞穩態的可能性和返回穩定狀態所需的時間取決于用于制造器件的工藝技術以及環境條件。通常,觸發器將在一兩個時鐘周期內返回穩定狀態。

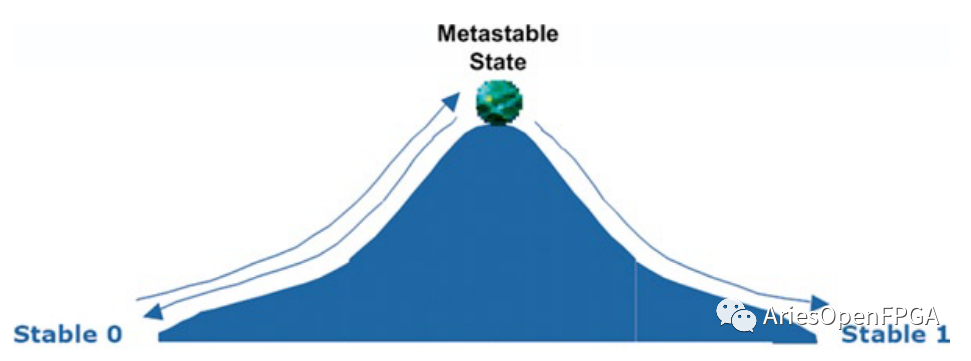

觸發器的操作類似于在無摩擦的山坡上滾動的球,如圖1.2所示。小山的每一側代表穩定狀態(即高或低),頂部代表亞穩態。假設球處于穩定狀態(即1或0),并且對球進行了足夠的推動(狀態轉換)(沒有違反建立時間或保持時間),足以使球越過另一個穩定狀態,則球在指定時間內越過另一個穩定狀態。

但是,如果推力較小(即違反建立和保持時間),則球應移動到山頂(即輸出亞穩態),停留在那里一段時間,然后返回任一穩定狀態(即輸出最終變得穩定)。球也可能會部分升起然后回來(即輸出可能會產生一些毛刺)。任何一種情況都會增加從時鐘轉換到穩定輸出的延遲。

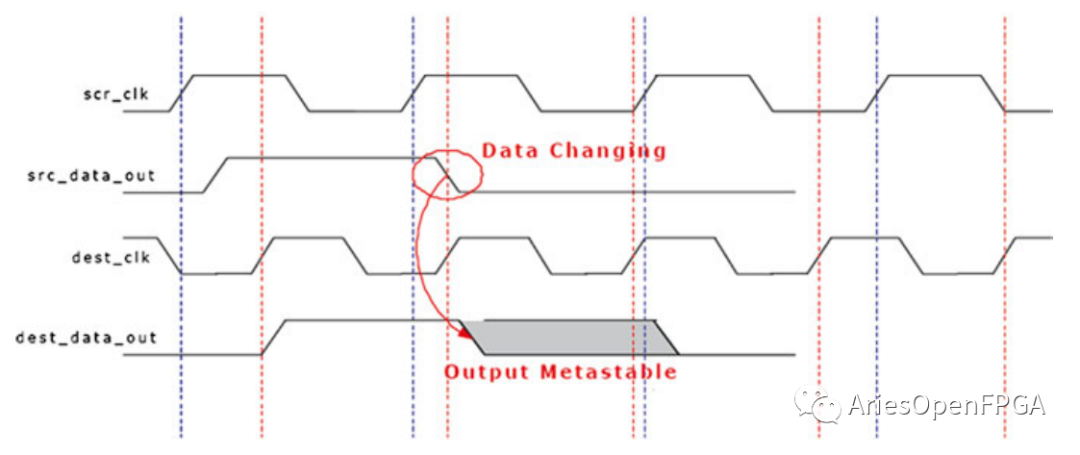

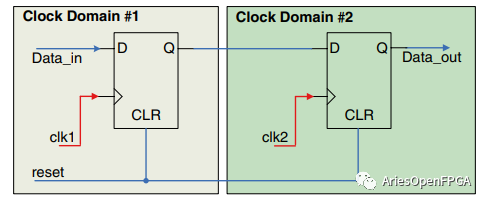

因此,簡單來說,當信號在一個時鐘域(src_data_out)中發生變化并在另一個時鐘域(dest_data_in)中被采樣時,這將導致輸出變得亞穩。這被稱為同步失敗(如圖1.3所示)。

圖1.2觸發器的亞穩態行為

圖1.3觸發器中的亞穩態

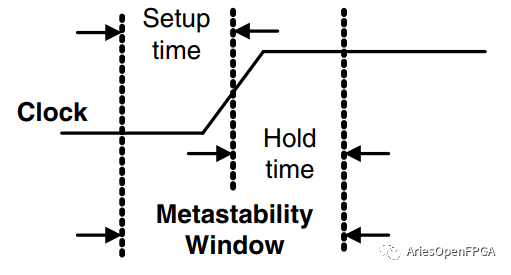

三、亞穩態窗口

亞穩態窗口被定義為特定的時間長度,在此期間數據和時鐘均不應更改。如果兩個信號有發生改變,則輸出可能變為亞穩態。如圖1.4所示,建立時間和保持時間的組合決定了亞穩窗口的寬度。窗口越大,設備進入亞穩態的機會就越大。在大多數情況下,較新的邏輯系列具有較小的亞穩態窗口,從而減少了設備變為亞穩的機會。

四、計算MTBF

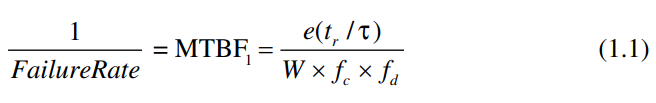

系統之間的平均故障間隔時間(MTBF)是在故障率恒定的特殊情況下故障率的倒數。這提供了有關特定觸發器失敗頻率的信息。對于具有給定時鐘頻率和異步數據邊沿的單級同步器,該邊沿在時鐘周期內具有均勻的概率密度,通過建立和保持時間窗口與時鐘邊沿之間的時間之比,再乘以數據邊沿頻率,可以計算出亞穩態事件的發生率。

圖1.4亞穩窗口

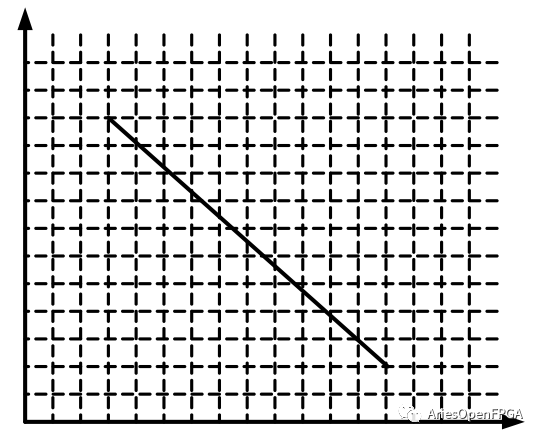

圖1.5故障率與時間的關系(對數刻度)

其中

tr =允許的解決時間超過器件的正常傳播延遲時間

π =觸發器的亞穩態(解析)時間常數

W =亞穩態窗口

fc =時鐘頻率

fd =異步數據邊沿頻率

常數W和τ與設備的電氣特性有關,并且會根據工藝技術節點而變化。因此,使用相同工藝制造的不同設備的W和τ值相似。

如果在不同的分辨時間下測量設備的故障率并繪制圖表,則結果將呈指數衰減曲線。如圖1.5所示,當以半對數標度繪制時,它成為一條斜率等于τ的直線;因此,線上的兩個數據點足以使用等式1.2計算τ的值。

其中:

tr1 = 解析時間1

tr2 = 解析時間2

N1 = tr1處的故障數

N2 = tr2處的故障數

根據公式1.1和1.2,可以通過下面的公式1.3計算兩級同步器的MTBF

其中:

tr1=同步器第一級所允許的解析時間

tr2 =接入正常傳播延遲時的解析時間

公式1.3中的第一項計算了同步器第一階段的MTBF,這實際上成為了下一階段亞穩態事件的發生率。然后,第二項根據tr2的值(同步器外部允許的解決時間)計算亞穩態事件將被解決的概率。這兩個項的乘積給出了兩級同步器的總體MTBF。以定量的方式,使用上面的公式1.3,如果特定觸發器在給定時鐘速率和輸入轉換速率的范圍內的平均故障間隔時間(MTBF)為40 s,則使用兩個這樣的觸發器的MTBF 同步輸入將是40×40 = 26.6分鐘。

五、避免亞穩態

如第二節所示,只要違反建立或保持時間,就會發生亞穩。因此,在以下情況下,信號可能會違反時序要求:

1、當輸入信號是異步信號時。

2、當時鐘偏斜/偏擺(上升/下降時間)高于容許極限時。

3、當信號越過工作在兩個不同頻率或頻率相同但相位和偏斜不同的域時。

4、當組合延遲使得觸發器數據輸入在亞穩態窗口中發生變化時

亞穩定性可能會導致過度的傳播延遲和后續的系統故障。所有觸發器和鎖存器均具有亞穩性。這個問題無法消除。但是有可能降低亞穩態的發生率

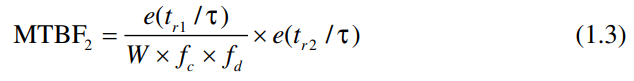

圖1.6 N級同步器

圖1.7具有時鐘提升電路的多級同步器

Multi-stage synchronizer with clock boost circuitry

在最簡單的情況下,設計人員可以通過讓時鐘周期足夠長以解決準穩態以及減少路徑中可能傳播到下一個觸發器中的任何延遲邏輯來避免亞穩態。考慮到大多數現代設計的性能要求,這種方法雖然簡單,卻并不實用。另一種方法是使用同步器。

5.1使用多級同步器

避免亞穩態的最常見方法是在一個時鐘域到另一個時鐘域的信號上添加一個或多個同步觸發器。如圖1.6所示,這種方法為第一個同步觸發器中的亞穩態事件提供了一個完整的時鐘周期(第二個觸發器的建立時間除外)以解決自身問題。但是,這確實增加了同步邏輯觀察輸入的等待時間。

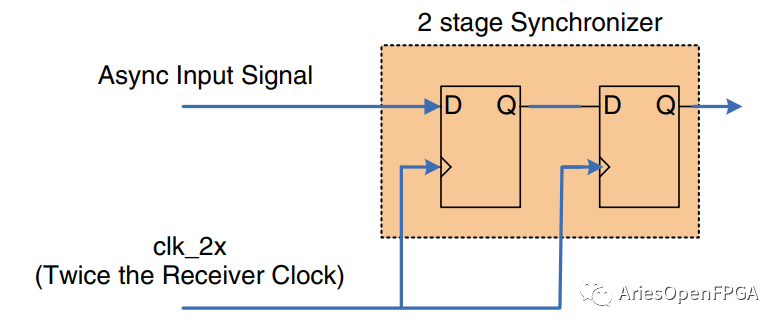

5.2使用時鐘升壓電路的多級同步器

多級同步器的一個限制是系統響應異步輸入所花費的時間更長。解決此問題的方法是使用時鐘倍頻器的輸出為兩個同步觸發器提供時鐘。Altera的FPGA將這種技術稱為Clock Boost或Clock Doubler(圖1.7)。

這種方法允許系統在一個系統時鐘周期內響應異步輸入,同時仍能改善MTBF。盡管Clock Boost時鐘可能會降低MTBF,但這種影響遠不止于兩個同步觸發器的抵消。這兩種方法都不能保證亞穩性不能通過同步器。它們只是降低了亞穩發生的可能性。

六、亞穩測試電路

每當觸發器對異步輸入進行采樣時,小概率的不可預測延遲總會在觸發器輸出端呈現出來。這不僅發生在輸入轉換違反建立和保持時間規范時,而且還發生在觸發器接收新數據時的小的時序窗口,在這些情況下,觸發器會進入亞穩態。

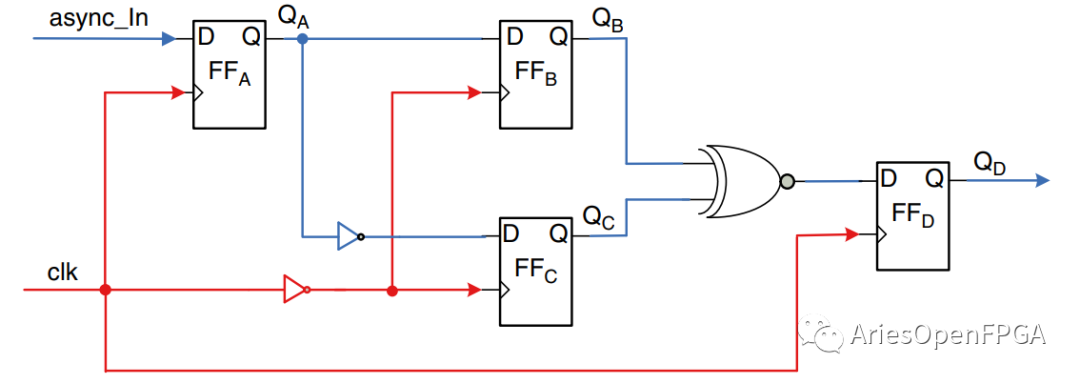

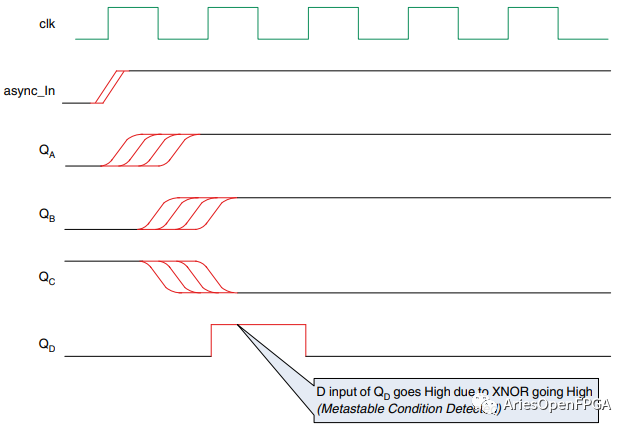

圖1.8中描述的測試電路用于確定觸發器的亞穩特性。圖1.8顯示了在時鐘“ clk”的上升沿觸發的觸發器“ FFA”的異步輸入“ async_In”。如圖所示,觸發器“ FFB”和“ FFC”均在時鐘的下降沿觸發,以便捕獲“ FFA”上的亞穩事件。

當互補信號在觸發器“ FFB”和“ FFC”的輸入上傳遞時,無論何時“ FFA”上發生亞穩態事件,XNOR門的輸出都將變為高電平。此條件在觸發器“ FFD”的輸出上捕獲,指示已檢測到亞穩態事件。

該測試電路中所有節點的時序如圖1.9所示。由于解析觸發器(“ FFB”和“ FFC”)由時鐘下降沿提供時鐘,因此可以通過更改時鐘高電平時間(△t)來控制所需的建立時間。穩定時間tMET可通過以下公式確定

其中tACN是最小時鐘周期,它等于解析觸發器(FFB或FFC)的tCQ(FFA的時鐘到輸出延遲)的建立時間tsu。

圖1.8亞穩性測試電路

圖1.9亞穩測試電路的時序

減少解析時間或建立時間的方法之一是在建立/保持期間以數據為中心增加抖動。

七、同步器類型

根據等式 1.1,具有異步輸入的電路的平均故障間隔時間(MTBF)與可從亞穩態條件恢復的時間呈指數關系。使用同步器創建時間緩沖區,以從亞穩態事件中恢復。

請注意,異步信號絕不能由多個同步器同步。(這樣做會冒著使多個同步器的輸出產生不同信號的風險)。本節顯示了兩個同步器方案A和B。

方案A是常規方案,當異步輸入信號的寬度大于時鐘周期時,其工作效果最佳(圖1.10)。

請注意,即使異步輸入在設置間隔之外達到穩定條件,它仍將以兩個時鐘周期的延遲進行計時,否則FF1可能會進入亞穩態。

如果亞穩在少于一個時鐘周期內得到解決,則FF2將具有穩定的輸入,否則需要更深的級聯,如圖1.6所示。

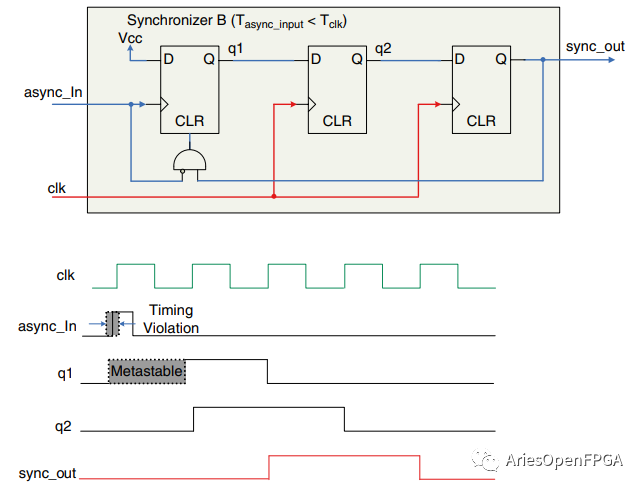

圖1.10兩級同步器的同步器方案A

圖1.11兩級同步器的同步器方案B

但是,在異步輸入的寬度小于時鐘周期的情況下,方案A不起作用。在這種情況下,方案B的工作效果最佳,如圖1.11所示。

請注意,在同步器方案B的情況下,第一個FF(觸發器)的D輸入連接到VCC,而異步輸入為FF提供時鐘。該階段中的其他兩個FF由系統時鐘或clk直接提供時鐘。短脈沖將驅動q1高電平,該信號將在兩個“clk”邊沿之后傳播到sync_out。因此,這定義了我們的經驗法則,總結如下:

當信號必須跨越時鐘域之間的邊界時,請使用同步器。

如果Clk1《Clk2在時鐘域2的輸入處使用同步器方案A(如圖1.11所示),否則使用同步器方案B。

八、處理亞穩態的建議

(a)使用同步器。

(b)使用更快的觸發器(更窄的亞穩態窗口TW)。

(c)使用亞穩態硬化觸發器(專為非常高的帶寬和減少的采樣時間而設計,并針對時鐘域輸入電路進行了優化)。

(d)級聯觸發器作為同步器(兩個或更多),如圖1.6所示。一串N個觸發器的概率為PN(P的N次方),其中P是一個觸發器發生亞穩態故障的機會。

(e)降低采樣率。

(f)避免輸入dV/dt低的信號

原文標題:亞穩態詳解

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

同步

+關注

關注

0文章

105瀏覽量

20072 -

觸發器

+關注

關注

14文章

2056瀏覽量

63411

原文標題:亞穩態詳解

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

SN54121和SN74121單穩態多諧振蕩器:設計與應用詳解

SN54AHCT123A與SN74AHCT123A雙可重觸發單穩態多諧振蕩器:設計與應用詳解

SN54LS422、SN54LS423、SN74LS422 和 SN74LS423 可重觸發單穩態多諧振蕩器詳解

CD54HC4538、CD74HC4538等系列雙可重觸發精密單穩態多諧振蕩器詳解

晶臺KLH11LX系列丨施密特觸發器光耦在按鍵消抖中的應用

施密特觸發器光耦在門鈴系統中的應用

高速施密特觸發器密封光耦合器 skyworksinc

密封表面貼裝、高速施密特觸發器光耦合器 skyworksinc

用于混合組裝的微型高速施密特觸發器光耦合器 skyworksinc

同步系統中觸發器的亞穩態詳解

同步系統中觸發器的亞穩態詳解

評論